# 5+2 Channel DC/DC Converters for DV

## **General Description**

This is a 5+2CH integrated PMIC for DV application. There are 5 DC/DC converters : one synchronous step-up, one selectable synchronous step-up/step-down, two synchronous step-downs, and one WLED driver in either asynchronous step-up or current source mode, selectable by VOUT6 initial voltage. In addition, there are 2 LDO regulators : one RTC LDO and one generic LDO. The generic LDO can choose internal feedback loop for fixed output 2.5V or external feedback loop for customized output voltage. Both low voltage synchronous step-up converters are with load disconnect function. All power MOSFETs and compensation networks are integrated. There is a power good indicator to monitor FB2, FB3, and FB4 voltage status. CH1 to CH5 enabling can be controlled flexibly : enabled independently or in preset sequences.

## Ordering Information

RT9992 🗖 🗖

Package Type

QW : WQFN-32L 4x4 (W-Type)

Operating Temperature Range

- G : Green (Halogen Free with Commercial Standard)

- Z : Cu wire and Green (Halogen Free with Commer-cial Standard)

Note :

Richtek Green products are :

- RoHS compliant and compatible with the current requirements of IPC/JEDEC J-STD-020.

- Suitable for use in SnPb or Pb-free soldering processes.

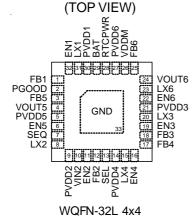

## **Pin Configurations**

### Features

- All Power MOSFETs Integrated

- 5 Channels with Internal Compensation

- Flexible Enabling Control

- Enabled Independently or in Preset Power On/ Off Sequences

- CH2 Synchronous Converter in Step-Up or Step-Down Mode Selectable by SEL Pin

- Synchronous Step-Down DC/DC Converter

- Up to 95% Efficiency

- 100% (max) Duty Cycle

- Synchronous Step-Up DC/DC Converter

- Adjustable Output Voltage

- Up to 95% Efficiency

- Asynchronous Step-Up Converter to Drive WLED, Selectable Between Step-Up or Current Source

- LED Open Protection (OVP6) in Step-Up Mode

- PWM Dimming Control

- Load Disconnect Function for CH1 and CH2 Synchronous Step-Up Converter

- Fixed 2MHz Switching Frequency for CH1, CH2, CH3, and CH4

- Fixed 1MHz Switching Frequency for CH6

- Generic LDO (CH5)

- Output Voltage : Fixed 2.5V or Set by External Feedback Network, Determined by FB5 Initial Voltage

- RTC LDO : Fixed Output Voltage 3.1V

- Power Good Indicator to Monitor Output Voltage Status of CH2, CH3, and CH4

- 32-Lead Package

- RoHS Compliant and Halogen Free

### Applications

- CMOS DV

- Gaming

### **Marking Information**

ES=YM DNN ES= : Product Code YMDNN : Date Code

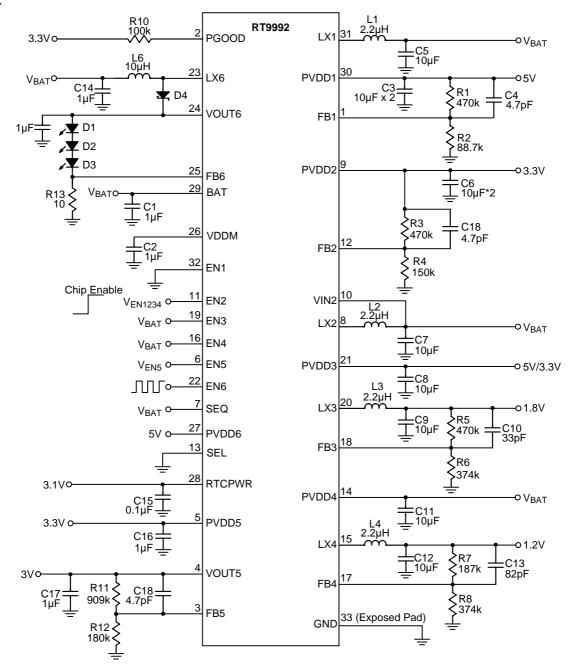

### **Typical Application Circuit**

For 2AA :

For above circuit, the power sequence is CH1  $\rightarrow$  CH3  $\rightarrow$  CH4  $\rightarrow$  CH2, while CH5 remains independent. For other power sequence combinations, refer to the power on/ff sequence section in application information.

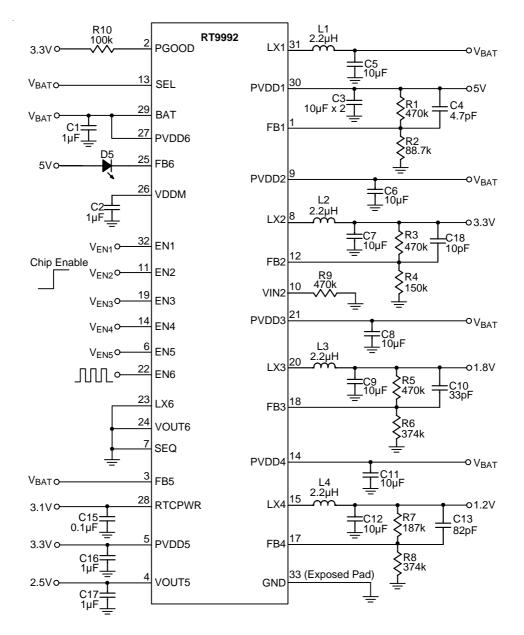

For Li+ :

For above circuit, all channels are independently enable/disable.

For other power sequence combinations, refer to the power on/ff sequence section in application information.

| Channel     | CH3 |                                         |     |     |     |      |  |  |

|-------------|-----|-----------------------------------------|-----|-----|-----|------|--|--|

| Calculation |     | V <sub>OUT_CH3</sub> = (1+R5/R6) x 0.8V |     |     |     |      |  |  |

| Vout(V)     | 2.5 | 1.8                                     | 1.5 | 1.3 | 1.2 | 1    |  |  |

| L3 (μH)     | 2.2 | 2.2                                     | 2.2 | 2.2 | 2.2 | 2.2  |  |  |

| R5 (kΩ)     | 768 | 470                                     | 330 | 237 | 187 | 23.2 |  |  |

| R6 (kΩ)     | 360 | 374                                     | 374 | 374 | 374 | 93.1 |  |  |

| C9 (µF)     | 10  | 10                                      | 10  | 10  | 10  | 10   |  |  |

| C10 (pF)    | 22  | 33                                      | 47  | 68  | 82  | 47   |  |  |

#### Table 1. Recommended Components for the Typical Application Circuit

| Channel              |     | CH4                                     |     |     |     |      |  |

|----------------------|-----|-----------------------------------------|-----|-----|-----|------|--|

| Calculation          |     | V <sub>OUT_CH4</sub> = (1+R7/R8) x 0.8V |     |     |     |      |  |

| V <sub>OUT</sub> (V) | 2.5 | 1.8                                     | 1.5 | 1.3 | 1.2 | 1    |  |

| L4 (μH)              | 2.2 | 2.2                                     | 2.2 | 2.2 | 2.2 | 2.2  |  |

| R7 (kΩ)              | 768 | 470                                     | 330 | 237 | 187 | 23.2 |  |

| R8 (kΩ)              | 360 | 374                                     | 374 | 374 | 374 | 93.1 |  |

| C12 (µF)             | 10  | 10                                      | 10  | 10  | 10  | 10   |  |

| C13 (pF)             | 22  | 33                                      | 47  | 68  | 82  | 47   |  |

Where C9, C12 are  $C_{OUT}$ ,

C10, C13 are feedforward cap between output and FB

R5, R7 are the feedback resistor between output and FB

R6, R8 are the feedback resistor between GND and FB

4

## **Functional Pin Description**

| Pin No.             | Pin Name | Pin Function                                                                                                                          |

|---------------------|----------|---------------------------------------------------------------------------------------------------------------------------------------|

| 1                   | FB1      | Feedback Input Pin of CH1. High impedance in shutdown.                                                                                |

| 2                   | PGOOD    | Power Good Indicator Output Pin (Open Drain).                                                                                         |

| 3                   | FB5      | Feedback Input Pin of CH5. High Impedance in Shutdown.                                                                                |

| 4                   | VOUT5    | Output Pin for CH5. High Impedance in Shutdown.                                                                                       |

| 5                   | PVDD5    | Power Input Pin of CH5.                                                                                                               |

| 6                   | EN5      | Enable Pin of CH5.                                                                                                                    |

| 7                   | SEQ      | SEQ = H to use preset power on/off sequence. SEQ = L to independently enable CH1 to 5. Logic state can't be changed during operation. |

| 8                   | LX2      | Switch Node of CH2. High Impedance in Shutdown.                                                                                       |

| 9                   | PVDD2    | Power Input Pin of CH2 in Step-Down or Power Output Pin of CH2 in Step-Up.                                                            |

| 10                  | VIN2     | Power Input Node of CH2 in Step-Up.                                                                                                   |

| 11                  | EN2      | Enable Pin of CH2 or Enable Pin of Preset On/Off Sequence.                                                                            |

| 12                  | FB2      | Feedback Input Pin of CH2. High Impedance in Shutdown.                                                                                |

| 13                  | SEL      | Select Pin to Define CH2 in Step-Down (SEL = H) or Step-Up (SEL = L)<br>Mode. Logic state can't be changed during operation.          |

| 14                  | PVDD4    | Power Input Pin of CH4.                                                                                                               |

| 15                  | LX4      | Switch Node of CH4. High Impedance in Shutdown.                                                                                       |

| 16                  | EN4      | Enable Pin of CH4 or Select which Preset On/Off Sequence.                                                                             |

| 17                  | FB4      | Feedback Input Pin of CH4. High Impedance in Shutdown.                                                                                |

| 18                  | FB3      | Feedback Input Pin of CH3. High Impedance in Shutdown.                                                                                |

| 19                  | EN3      | Enable Pin of CH3 or Select which Preset On/Off Sequence.                                                                             |

| 20                  | LX3      | Switch Node of CH3. High Impedance in Shutdown.                                                                                       |

| 21                  | PVDD3    | Power Input Pin of CH3.                                                                                                               |

| 22                  | EN6      | Enable Pin of CH6 and PWM Dimming Input Signal Pin.                                                                                   |

| 23                  | LX6      | Switch Node of CH6 in Step-Up Mode. High Impedance in Shutdown.                                                                       |

| 24                  | VOUT6    | Sense Pin for CH6 Output Voltage in Step-Up Mode and CH6 Mode Selection Pin.                                                          |

| 25                  | FB6      | Feedback Input Pin of CH6 in Step-Up Mode or Current Sink Pin of CH6 in Current Source Mode.                                          |

| 26                  | VDDM     | Internal Control Circuit Power Pin. That must connect to a bypass capacitor for better noise rejection.                               |

| 27                  | PVDD6    | Power Input Pin of CH6 NMOS Driver.                                                                                                   |

| 28                  | RTCPWR   | RTC Power Output Pin.                                                                                                                 |

| 29                  | BAT      | Battery Power Input Pin and CH1 Step-Up Power Input Node.                                                                             |

| 30                  | PVDD1    | Power Output Pin of CH1.                                                                                                              |

| 31                  | LX1      | Switch Node of CH1. High Impedance in Shutdown.                                                                                       |

| 32                  | EN1      | Enable Pin of CH1.                                                                                                                    |

| 33<br>(Exposed pad) | GND      | Ground. The exposed pad must be soldered to a large PCB and connected to GND for maximum power dissipation.                           |

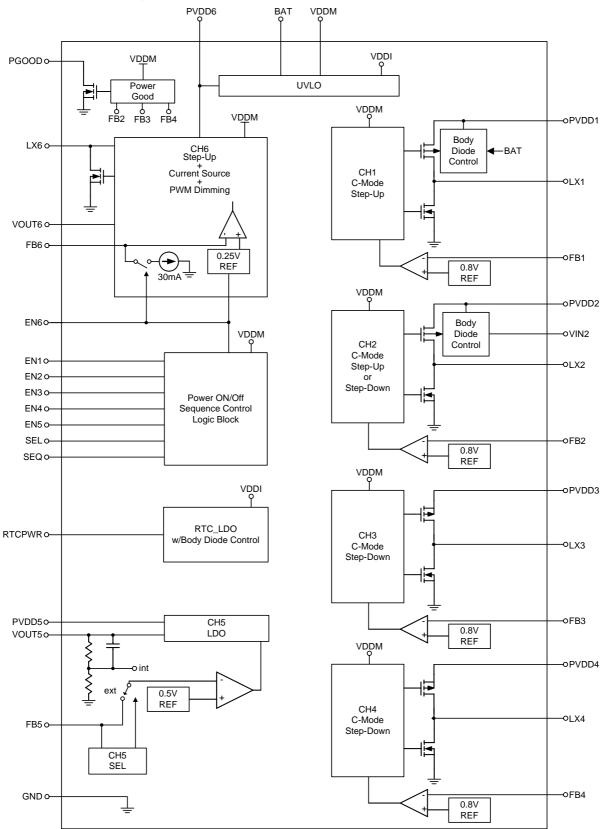

## **Function Block Diagram**

## Absolute Maximum Ratings (Note 1)

| <ul> <li>Supply Voltage, VDDM</li></ul>        | 0.3V to 7V<br>0.3V to 10V |

|------------------------------------------------|---------------------------|

| < 20ns                                         | 8V to 24V                 |

| Other Pins                                     | - –0.3V to 7V             |

| • Power Dissipation, $P_D @ T_A = 25^{\circ}C$ |                           |

| WQFN-32L 4x4                                   | - 1.923W                  |

| Package Thermal Resistance (Note 2)            |                           |

| WQFN-32L 4x4, θ <sub>JA</sub>                  | - 52°C/W                  |

| WQFN-32L 4x4, θ <sub>JC</sub>                  |                           |

| Junction Temperature                           |                           |

| Lead Temperature (Soldering, 10 sec.)          | - 260°C                   |

| Storage Temperature Range                      | - –65°C to 150°C          |

| ESD Susceptibility (Note 3)                    |                           |

| HBM (Human Body Mode)                          | - 2kV                     |

| MM (Machine Mode)                              | - 200V                    |

## Recommended Operating Conditions (Note 4)

| Supply Voltage VDDM        | - 2.7V to 5.5V   |

|----------------------------|------------------|

| Junction Temperature Range | - –40°C to 125°C |

| Ambient Temperature Range  | 40°C to 85°C     |

### **Electrical Characteristics**

(V<sub>DDM</sub> = 3.3V,  $T_A$  = 25°C, unless otherwise specified)

| Parameter                                                                    | Symbol          | Test Conditions                                                        | Min | Тур | Max | Unit |

|------------------------------------------------------------------------------|-----------------|------------------------------------------------------------------------|-----|-----|-----|------|

| Supply Voltage                                                               |                 | •                                                                      |     |     |     |      |

| VDDM Startup Voltage                                                         | V <sub>ST</sub> | For Bootstrap, First Rising                                            | 1.5 |     |     | V    |

| Supply Current                                                               |                 |                                                                        |     | -   |     |      |

| Shutdown Supply Current into<br>BAT (including RTC LDO<br>quiescent current) |                 | $V_{BAT} = 4.2$ V, $V_{PVDD6} = 3$ V                                   |     | 7   | 20  | μA   |

| Shutdown Supply Current into PVDD6                                           |                 | $V_{BAT} = 4.2V, V_{PVDD6} < V_{BAT}$                                  |     |     | 1   | μA   |

| Shutdown Supply Current into VDDM                                            | IOFF            | ENx = 0, V <sub>SEQ</sub> = 0V, SEL = 0V                               |     | 1   | 10  | μA   |

| CH1 (Synchronous Step-Up)<br>Supply Current into VDDM                        | I <sub>Q1</sub> | Non Switching, $V_{EN1} = 3.3V$ , $V_{FB1} = 0.9V$ , $V_{SEQ} = 0V$    |     |     | 800 | μA   |

| CH2 (Synchronous Step-Up or<br>Step-Down) Supply Current<br>into VDDM        | I <sub>Q2</sub> | Non Switching, $V_{EN2} = 3.3V$ ,<br>$V_{FB2} = 0.9V$ , $V_{SEQ} = 0V$ |     |     | 800 | μA   |

| CH3 (Synchronous<br>Step-Down)<br>Supply Current into VDDM                   | I <sub>Q3</sub> | Non Switching, $V_{EN3} = 3.3V$ ,<br>$V_{FB3} = 0.9V$ , $V_{SEQ} = 0V$ |     |     | 800 | μA   |

To be continued

Preliminary

| Devery stor                                                                                  | Cumhal              | Test Canditions                                                        | Min   | True | Max   | 1.1  |

|----------------------------------------------------------------------------------------------|---------------------|------------------------------------------------------------------------|-------|------|-------|------|

| Parameter                                                                                    | Symbol              | Test Conditions                                                        | Min   | Тур  | Max   | Unit |

| CH4 (Synchronous Step-Down)<br>Supply Current into VDDM                                      | I <sub>Q4</sub>     | Non Switching, $V_{EN4} = 3.3V$ ,<br>$V_{FB4} = 0.9V$ , $V_{SEQ} = 0V$ |       |      | 800   | μA   |

| CH6 (WLED) in Current Source Mode Supply Current into VDDM                                   | I <sub>Q6c</sub>    | V <sub>EN6</sub> = 3.3V, V <sub>OUT6</sub> = 0V                        |       |      | 600   | μΑ   |

| CH6 (WLED) in Asynchronous<br>Step-Up Mode Supply Current into<br>VDDM                       | I <sub>Q6b</sub>    | Non switching,<br>$V_{EN6} = 3.3V$ , $V_{FB6} = 0.35V$ ,<br>VOUT6 = 1V |       |      | 800   | μΑ   |

| Oscillator                                                                                   |                     |                                                                        |       | -    |       |      |

| CH1, 2, 3, 4 Operation Frequency                                                             | fosc                |                                                                        | 1800  | 2000 | 2200  | kHz  |

| CH6 Operation Frequency                                                                      | fosc6               |                                                                        | 900   | 1000 | 1100  | kHz  |

| CH1 Maximum Duty Cycle (Step-Up)                                                             |                     | V <sub>FB1</sub> = 0.7V                                                | 80    | 83.5 | 87    | %    |

| CH2 Maximum Duty Cycle (Step-Up)                                                             |                     | $V_{FB2} = 0.7 V$                                                      | 80    | 83.5 | 87    | %    |

| CH2 Maximum Duty Cycle<br>(Step-Down)                                                        |                     | V <sub>FB2</sub> = 0.7V                                                |       |      | 100   | %    |

| CH3 Maximum Duty Cycle<br>(Step-Down)                                                        |                     | V <sub>FB3</sub> = 0.7V                                                |       |      | 100   | %    |

| CH4 Maximum Duty Cycle<br>(Step-Down)                                                        |                     | $V_{FB4} = 0.7V$                                                       |       |      | 100   | %    |

| CH6 Maximum Duty Cycle (Step-Up)                                                             |                     | $V_{FB6} = 0.15V, V_{OUT6} = 1V$                                       | 91    | 93   | 97    | %    |

| Feedback and output Regulation Vo<br>Feedback Regulation Voltage @ FB1,<br>FB2, FB3, and FB4 | Itage               |                                                                        | 0.788 | 0.8  | 0.812 | V    |

| Sink Current into FB6 (CS mode)                                                              |                     | $V_{OUT6} = 0V$ , Current Source                                       | 28.5  | 30   | 31.5  | mA   |

| Dropout Voltage @ FB6 (CS mode)                                                              |                     | $V_{OUT6} = 0V, V_{DDM} = 3.3V,$<br>Current Source                     |       |      | 0.6   | V    |

| Feedback Regulation Voltage @ FB6                                                            | V <sub>FB6</sub>    | V <sub>OUT6</sub> = 1V. Step-Up                                        | 0.237 | 0.25 | 0.263 | V    |

| Power Switch                                                                                 | ·                   |                                                                        |       | -    |       |      |

|                                                                                              |                     | P-MOSFET, V <sub>PVDD1</sub> = 3.3V                                    |       | 200  | 300   | mΩ   |

| CH1 On Resistance of MOSFET                                                                  | R <sub>DS(ON)</sub> | N-MOSFET,<br>V <sub>PVDD1</sub> = 3.3V                                 |       | 130  | 250   | mΩ   |

| CH1 Current Limitation (Step-Up)                                                             | I <sub>LIM1</sub>   |                                                                        | 2.2   | 3    | 4     | Α    |

|                                                                                              |                     | P-MOSFET, V <sub>PVDD2</sub> = 3.3V                                    |       | 400  | 550   | mΩ   |

| CH2 On Resistance of MOSFET                                                                  | R <sub>DS(ON)</sub> | N-MOSFET,                                                              |       | 260  | 400   | mΩ   |

| CH2 Current Limitation (Step-Down)                                                           | I <sub>LIM2_D</sub> | V <sub>PVDD2</sub> = 3.3V                                              | 1     | 1.5  | 2     | A    |

| CH2 Current Limitation (Step-Up)                                                             | I <sub>LIM2_U</sub> |                                                                        | 1.5   | 2.1  | 3.0   | А    |

|                                                                                              |                     | P-MOSFET, V <sub>PVDD3</sub> = 3.3V                                    |       | 370  | 500   | mΩ   |

| CH3 On Resistance of MOSFET                                                                  | R <sub>DS(ON)</sub> | N-MOSFET,<br>V <sub>PVDD3</sub> = 3.3V                                 |       | 300  | 400   | mΩ   |

| CH3 Current Limitation (Step-Down)                                                           | I <sub>LIM3</sub>   |                                                                        | 1     | 1.5  | 2     | А    |

| CH4 On Resistance of MOSFET                                                                  | R <sub>DS(ON)</sub> | P-MOSFET, V <sub>PVDD4</sub> = 3.3V                                    |       | 240  | 400   | mΩ   |

|                                                                                              |                     | N-MOSFET, $V_{PVDD4} = 3.3V$                                           |       | 140  | 250   | mΩ   |

| CH4 Current Limitation (Step-Down)                                                           | I <sub>LIM4</sub>   |                                                                        | 1.5   | 2    | 2.4   | А    |

| CH6 On Resistance of MOSFET                                                                  | R <sub>DS(ON)</sub> | N-MOSFET                                                               |       | 0.75 | 1.1   | Ω    |

| CH6 Current Limitation                                                                       | I <sub>LIM6</sub>   | N-MOSFET                                                               | 0.6   | 0.8  | 1     | А    |

To be continued

| Param                                  | eter                                                    | Symbol               | Test Conditions                                                                         | Min   | Тур  | Мах   | Unit |

|----------------------------------------|---------------------------------------------------------|----------------------|-----------------------------------------------------------------------------------------|-------|------|-------|------|

| Protection                             |                                                         |                      | •                                                                                       |       |      |       |      |

|                                        | Over Voltage Protection<br>PVDD1,PVDD2 (CH2 in Step-Up) |                      |                                                                                         | 5.9   | 6.15 | 6.4   | V    |

| Over Voltage Protect                   | ction @ VOUT6                                           | V <sub>OVP6</sub>    | Step-Up                                                                                 | 17    | 19   | 21    | V    |

| Under Voltage Prote<br>FB2, FB3, FB4   | ection @ FB1,                                           | V <sub>UVP1234</sub> |                                                                                         |       | 0.4  |       | V    |

| Under Voltage Prote                    | ection @ FB5                                            | VUVP5                |                                                                                         |       | 0.3  |       | V    |

| VDDM Over Voltage                      | e Protection                                            |                      |                                                                                         | 5.9   | 6.15 | 6.4   | V    |

| VDDM UVLO Thres                        | bold                                                    |                      | VDDM Rising                                                                             |       | 2.4  | 2.7   | V    |

| VDDM OVEO THes                         |                                                         |                      | VDDM Falling                                                                            | 1.7   | 2.1  | 2.4   | V    |

| BAT UVLO Thresho                       | ld                                                      |                      | BAT Rising                                                                              | 1.3   | 1.4  | 1.5   | V    |

| BAT OVEO THESHO                        | nu -                                                    |                      | BAT Falling                                                                             | 1.2   | 1.3  | 1.4   | V    |

| Protection Fault De                    | lay                                                     |                      | Except OVP1/2                                                                           |       | 100  |       | ms   |

| Control                                |                                                         |                      | ·                                                                                       |       |      |       |      |

| EN1 to 6,                              | Logic-High                                              | VIH                  |                                                                                         | 1.3   |      |       | V    |

| SEL,SEQ<br>Threshold Voltage           | Logic-Low                                               | VIL                  |                                                                                         |       |      | 0.4   | V    |

| EN1 to 5, SEL, SEC                     | Q Sink Current                                          |                      |                                                                                         |       | 1    | 6     | μΑ   |

| EN6 Sink Current                       |                                                         |                      |                                                                                         |       | 4    | 20    | μA   |

| EN6 Low Time for S                     | Shutdown                                                | t <sub>SHDN</sub>    |                                                                                         |       | 32.7 |       | ms   |

| EN6 High Time for CH6 Enable           |                                                         |                      |                                                                                         |       | 1.2  | 5     | μS   |

| Thermal Protection                     | n                                                       |                      |                                                                                         |       |      |       |      |

| Thermal Shutdown                       |                                                         | T <sub>SD</sub>      |                                                                                         | 125   | 160  |       | °C   |

| Thermal Shutdown                       | Hysteresis                                              | $\Delta T_{SD}$      |                                                                                         |       | 20   |       | °C   |

| CH5 LDO (C <sub>OUT</sub> =            | 1μF for Better S                                        | tability)            |                                                                                         |       |      |       |      |

| Input Voltage Rang                     | e (PVDD5)                                               | V <sub>PVDD5</sub>   |                                                                                         | 2.7   |      | 5.5   | V    |

| Output Voltage Ran                     | ige                                                     | V <sub>OUT5</sub>    | By external feedback                                                                    | 1.5   |      | 3.3   | V    |

| Feedback Regulation                    | on Voltage @                                            | V <sub>FB5</sub>     | Using external feedback loop                                                            | 0.493 | 0.5  | 0.507 | V    |

| Regulated Output V<br>VOUT5            | oltage @                                                | V <sub>REG5</sub>    | Using internal feedback loop                                                            | 2.45  | 2.5  | 2.55  | V    |

| FB5 Threshold to S<br>Feedback Network | elect Internal                                          |                      | (Note : before enabled, V <sub>FB5</sub> ><br>0.8V. Then CH5 uses internal<br>feedback) | 0.8   |      |       | V    |

| Max Current Limit                      |                                                         | I <sub>LIM5</sub>    | $V_{PVDD5} = 3.3V$                                                                      | 200   | 300  | 400   | mA   |

| Dropout Voltage                        |                                                         |                      | I <sub>OUT</sub> = 100mA                                                                | 60    | 100  | 120   | mV   |

| Soft-Start Time                        |                                                         | tss5                 | V <sub>FB5</sub> = 0 to 0.5V                                                            |       | 2.4  |       | ms   |

| PSRR+                                  |                                                         |                      | $I_{OUT} = 10$ mA, $V_{PVDD5} = 3.3$ V,<br>$V_{OUT} = 2.5$ V, 1kHz                      |       | -55  |       | db   |

| Parameter                                     | Symbol           | Test Conditions                    | Min  | Тур  | Max  | Unit |  |

|-----------------------------------------------|------------------|------------------------------------|------|------|------|------|--|

| RTC LDO for RTCPWR (Keep On Once Bat Connect) |                  |                                    |      |      |      |      |  |

| Input Voltage Range                           | V <sub>DDI</sub> | Max of BAT and PVDD6               |      |      | 5.5  | V    |  |

| Quiescent Current                             | lq               | $V_{DDI} = 4.2V$                   |      | 5    | 8    | μA   |  |

| Regulated Output Voltage @<br>RTCPWR          |                  | I <sub>OUT</sub> = 0mA             | 3.0  | 3.1  | 3.2  | V    |  |

| Max Output Current<br>(Current Limit)         |                  | $V_{DDI} = 4.2V$                   | 60   | 105  | 200  | mA   |  |

|                                               |                  | I <sub>OUT</sub> = 50mA            |      |      | 700  | mV   |  |

| Dropout Voltage                               | VDROP            | I <sub>OUT</sub> = 10mA            |      | 40   | 120  | mV   |  |

|                                               |                  | I <sub>OUT</sub> = 3mA             |      |      | 40   | mV   |  |

| Power Good Indicator                          |                  |                                    |      |      |      |      |  |

| FB2 Regulation Threshold                      |                  | For PGOOD Go Low                   | 0.64 | 0.68 | 0.72 | V    |  |

| FB2 Hysteresis                                |                  |                                    |      | 40   |      | mV   |  |

| FB3 Regulation Threshold                      |                  | For PGOOD Go Low                   | 0.64 | 0.68 | 0.72 | V    |  |

| FB3 Hysteresis                                |                  |                                    |      | 40   |      | mV   |  |

| FB4 Regulation Threshold                      |                  | For PGOOD Go Low                   | 0.64 | 0.68 | 0.72 | V    |  |

| FB4 Hysteresis                                |                  |                                    |      | 40   |      | mV   |  |

| PGOOD Rising Delay Time                       |                  |                                    |      | 10   |      | ms   |  |

| PGOOD Sink Capability                         |                  | $V_{DDM} = 3.3V, V_{PGOOD} = 0.5V$ | 4    |      |      | mA   |  |

| Soft-Start Time                               |                  |                                    |      |      |      |      |  |

| CH1 Soft-Start Time                           | t <sub>SS1</sub> | $V_{FB1} = 0$ to 0.8V              | 2.8  | 3.5  | 4.2  | ms   |  |

| CH2 Soft-Start Time                           | t <sub>SS2</sub> | $V_{FB2} = 0$ to 0.8V              | 2.8  | 3.5  | 4.2  | ms   |  |

| CH3 Soft-Start Time                           | t <sub>SS3</sub> | V <sub>FB3</sub> = 0 to 0.8V       | 2.8  | 3.5  | 4.2  | ms   |  |

| CH4 Soft-Start Time                           | t <sub>SS4</sub> | V <sub>FB4</sub> = 0 to 0.8V       | 2.8  | 3.5  | 4.2  | ms   |  |

**Note 1.** Stresses listed as the above "Absolute Maximum Ratings" may cause permanent damage to the device. These are for stress ratings. Functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may remain possibility to affect device reliability.

Note 2.  $\theta_{JA}$  is measured in natural convection at  $T_A = 25^{\circ}C$  on a high-effective thermal conductivity four-layer test board of JEDEC 51-7 thermal measurement standard. The measurement case position of  $\theta_{JC}$  is on the exposed pad of the package.

Note 3. Devices are ESD sensitive. Handling precaution is recommended.

Note 4. The device is not guaranteed to function outside its operating conditions.

### **Application Information**

The RT9992 includes the following four DC/DC converter channels, two LDOs, and one WLED driver to build a multiple-output power-supply system.

CH1 : Step-up synchronous current mode DC/DC converter with internal power MOSFETs and compensation network. The P-MOSFET body can be controlled to disconnect the load.

CH2 : Selectable step-up or step-down synchronous current mode DC/DC converter with internal power MOSFETs and compensation network. The P-MOSFET body can be controlled to disconnect the load.

CH3 : Step-down synchronous current mode DC/DC converter with internal power MOSFETs and internal compensation network.

CH4 : Step-down synchronous current mode DC/DC converter with internal power MOSFETs and internal compensation network.

CH5 : Generic LDO that provides either fixed 2.5V output or adjustable output voltage via external feedback network, depending on initial by FB5 voltage prior to becoming enabled.

CH6: WLED driver operable in either current source mode or asynchronous step-up mode with internal power MOSFET and compensation network.

CH1 to CH4 operate in PWM mode with 2MHz, while CH6 operates in step-up mode with 1MHz switching frequency under moderate to heavy loading.

RTC\_LDO : 3.1V output LDO with low quiescent current and high output voltage accuracy.

Power Good Indicator : Monitors FB2, FB3, and FB4 status.

#### CH1 : Synchronous Step-Up DC/DC Converter

CH1 is a synchronous step-up converter for motor driver power in DSC system. The converter operates at fixed frequency and under PWM Current Mode. The converter integrates internal MOSFETs, compensation network and

synchronous rectifier for up to 95% efficiency. It also disconnects the load when CH1 is turned off. Connect BAT to the power input node in front of CH1 inductor.

The output voltage can be set by the following equation :

$V_{OUT\_CH1} = (1+R1/R2) \times V_{FB1}$ where  $V_{FB1}$  is 0.8V typically.

# CH2 : Synchronous Step-Up / Step-Down Selectable DC/DC Converter

CH2 is a synchronous step-up / step-down selectable converter for system I/O power.

#### Mode setting

CH2 of the RT9992 features flexible step-up/step-down topology setting for 2AA / Li-ion battery. If CH2 operates in step-up mode, the SEL pin should be connected to GND. If CH2 operates in step-down mode, the SEL pin should be connected to  $V_{BAT}$ . In addition, please note that the logic state can not be changed during operation.

| Table 2. C | H2 Mode | Stting |

|------------|---------|--------|

|------------|---------|--------|

| CH2 Operating<br>Mode | Connection                         |

|-----------------------|------------------------------------|

| Step-Up               | Connect the SEL pin to GND.        |

| Step-Down             | Connect the SEL pin to $V_{BAT}$ . |

#### Step-Up

The converter operates in fixed frequency PWM Mode, continuous current mode (CCM), and discontinuous current mode (DCM) with internal MOSFETs, compensation network and synchronous rectifier for up to 95% efficiency. In step-up mode, CH2 also disconnects the load when it is turned off. Connect VIN2 to the power input node in front of CH2 inductor.

#### Step-Down

The converter operates in fixed frequency PWM mode and continuous current mode (CCM) with internal MOSFETs, compensation network and synchronous

rectifier for up to 95% efficiency. The CH2 step-down converter can be operated at 100% maximum duty cycle to extend the input operating voltage range. When the input voltage is close to the output voltage, the converter enters low dropout mode. In step-down mode, connect the VIN2 pin to GND via a 470k $\Omega$  pull-down resistor.

The output voltage can be set by the following equation :

$V_{OUT_{CH2}} = (1+R3/R4) \times V_{FB2}$

where  $V_{FB2}$  is 0.8V typically

#### CH3 : Synchronous Step-Down DC/DC Converter

CH3 is suitable for DRAM power in DSC system. The converter operates in fixed frequency PWM mode and CCM with integrated internal MOSFETs and compensation network. The CH3 step-down converter can be operated at 100% maximum duty cycle to extend battery operating voltage range. When the input voltage is close to the output voltage, the converter enters low dropout mode with low output ripple.

The output voltage can be set by the following equation :

$V_{OUT\_CH3} = (1+R5/R6) \times V_{FB3}$

where  $V_{\text{FB3}}$  is 0.8V typically.

#### CH4 : Synchronous Step-Down DC/DC Converter

CH4 is suitable for processor core power in DSC system. The converter operates in fixed frequency PWM mode and CCM with integrated internal MOSFETs and compensation network. The CH4 step-down converter can be operated at 100% maximum duty cycle to extend battery operating voltage range. When the input voltage is close to the output voltage, the converter enters low dropout mode with low output ripple.

The output voltage can be set by the following equation :

$V_{OUT\_CH4} = (1+R7/R8) \times V_{FB4}$

Where  $V_{\mathsf{FB4}}$  is 0.8V typically.

#### CH5 : Generic LDO

The RT9992 provides a generic LDO with high output voltage accuracy. The LDO outputs either a fixed 2.5V voltage or an adjustable voltage with external feedback network, depending on the initial FB5 voltage. The CH5 adjustable output voltage can be set by the following equation :

$V_{OUT\_CH5} = (1+R11/R12) \times V_{FB5}$

Where  $V_{\text{FB5}}$  is 0.5V typically.

#### CH6: WLED Driver

CH6 is a WLED driver that can operate in either current source mode or asynchronous step-up mode, depending on the initial VOUT6 voltage level. In addition, if CH4 soft-

start does not finish, CH6 can not be turned on.

| Table 3. CH6 WLED Setting |       |  |  |  |

|---------------------------|-------|--|--|--|

| CH6 Operating Mode        | VOUT6 |  |  |  |

| Current Source            | <0.3V |  |  |  |

| Asynchronous<br>Step-Up   | >0.7V |  |  |  |

When CH6 works in current source mode, it sinks an accurate LED current modulated by EN6 high duty such that it is easily dimmed from 0mA to 30mA. If CH6 works in asynchronous step-up mode, it integrates asynchronous step-up mode with an internal MOSFET and internal compensation, and requires an external schottky diode to output a voltage up to 19V. The LED current is set via an external resistor and controlled via the PWM duty on the EN6 pin. Kegardless of the mode, holding EN6 low for more than 32.7ms will turn off CH6.

#### CH6 WLED Current Dimming Control

If CH6 is in asynchronous step-up mode, the WLED current is set by an external resistor. And the dimming is controlled by the duty of pulse width modulated signal on the EN6 pin.

The average current through WLED can be set by the following equations :

$I_{LED}$  (mA) = [250mV/R( $\Omega$ )] x Duty (%) ......for step-up mode Or  $I_{LED}$  (mA) = 30mA x Duty (%)...... for current source mode

R : Current sense resistor from FB6 to GND.

Duty : PWM dimming via the EN6 pin. Dimming frequency range is from 1kHz to 100kHz but 2kHz to 20kHz should be avoided to prevent audio noise distraction.

#### **VDDM Power Path**

To support bootstrap function, the RT9992 includes a power selection circuit which selects between BAT and PVDD6 for the higher voltage to be used as the internal node, VDDI, that connects to the external decoupling capacitor at the VDDM pin. VDDM is the main power for the RT9992 control circuit. VDDI is the power input for the RTC LDO. To bootstrap VDDM, PVDD6 must connect to the output of the first enabled low voltage synchronous step-up channel (CH1 or CH2). Furthermore, PVDD6 also

provides power to the N-MOSFET driver in CH6. The RT9992 includes UVLO circuits to check VDDM and BAT voltage status.

#### **RTC LDO**

The RT9992 provides a 3.1V output LDO for real time clock. The LDO features low quiescent current (5 $\mu$ A) and high output voltage accuracy. The RTC LDO is always on, even when the system is shut down. For better stability, it is recommended to connect a 0.1 $\mu$ F capacitor to the RTCPWR pin. The RTC LDO includes pass transistor body

diode control to avoid the RTCPWR node from back charging into the input node VDDI.

#### Power Good

The RT9992 provides a power good indicator to monitor FB2, FB3, and FB4 voltage status. After CH2, CH3, and CH4 are turned on, if any one of them becomes lower than 0.68V (typically), PGOOD will be pulled low. If all are higher than 0.72V, PGOOD will be released and pulled high after 10ms.

#### Power On/Off Sequence

SEQ = 0: CH1 to 5 are independently enabled by EN1 to EN5

SEQ = 1 : CH2 to 5, or CH1 to 4 is enabled in preset on/off sequence. The order is chosen by EN3 and EN4

| SEQ | EN2    | EN3    | EN4    | EN5    | EN1    | Power On Sequence |     |     |     |

|-----|--------|--------|--------|--------|--------|-------------------|-----|-----|-----|

| 0   | indept | indept | indept | indept | indept | independent       |     |     |     |

| 1   | EN2345 | 1      | 0      | Х      | indept | CH2               | СНЗ | CH4 | CH5 |

| 1   | EN2345 | 0      | 0      | 0      | indept | CH2               | CH5 | СНЗ | CH4 |

| 1   | EN1234 | 1      | 1      | indept | х      | CH1               | CH3 | CH4 | CH2 |

| 1   | EN1234 | 0      | 1      | indept | х      | CH1               | CH4 | CH3 | CH2 |

X : don't care but suggested to be LOW (0).

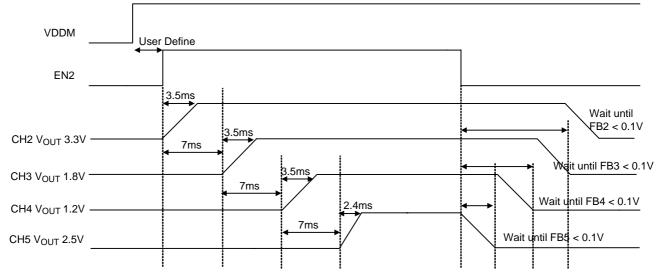

#### Power On/Off Sequence Example for CH2 to CH5

Sequence 1: SEQ is high, EN3 is high, EN4 is low.

EN2 will turn on/off CH2 to CH5 in preset sequence. CH1 will be turned on by EN1 independently.

CH2 to CH5 Power On Sequence is :

When EN2 goes high, CH2 will be turned on . 7ms after CH2 is turned on, CH3 will be turned on. 7ms after CH3 is turned on, CH4 will be turned on. 7ms after CH4 is turned on, CH5 will be turned on.

CH2 to CH5 Power-Off Sequence is :

When EN2 goes low, CH5 will be turned off and VOUT5 will be internally discharged. when VOUT5 discharging finishes, CH4 will turn off and internally discharge output via LX4 pin. When FB4 < 0.1V, CH3 will turn off and internally discharge output via LX3 pin. Likewise when FB3 < 0.1V, CH2 will turn off and discharge output via LX2 pin. After FB2 < 0.1V, CH2 to 5 shutdown sequence will be completed.

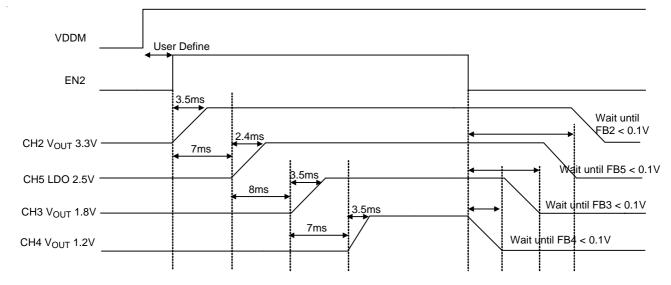

Sequence 2 : SEQ is high, EN3 is low, EN4 is low, EN5 is low.

EN2 will turn on/off CH2 to CH5 in preset sequence. CH1 will be turned on by EN1 independently.

CH2 to CH5 Power On Sequence is :

When EN2 goes high, CH2 will be turned on . 7ms after CH2 is turned on, CH5 will be turned on. About 1ms after Ch5 is turned on, CH3 will be turned on. 7ms after CH3 is turned on, CH4 will be turned on.

CH2 to CH5 Power-Off Sequence is :

When EN2 goes low, CH4 will turn off first and internally discharge output via LX4 pin. When FB4 < 0.1V, CH3 will turn off and internally discharge output via LX3 pin. Likewise, when FB3 < 0.1V, CH5 will turn off and VOUT5 will be internally discharged. When VOUT5 discharging finishes, CH2 will turn off and discharge output via LX2 pin. After FB2 < 0.1V, CH2 to 5 shut down sequence will be completed.

| EN3 to EN5 Setting        | Power On Sequence  |

|---------------------------|--------------------|

| EN3 = H, EN4 = L, EN5 = X | CH2→CH3→CH4→CH5    |

| EN3 = L, EN4 = L, EN5 = L | CH2→CH5→CH3→CH4    |

| EN3 to EN5 Setting        | Power Off Sequence |

| EN3 = H, EN4 = L, EN5 = X | CH5→CH4→CH3→CH2    |

| EN3 = L, EN4 = L, EN5 = L | CH4→CH3→CH5→CH2    |

#### Table 4. CH2 to CH5 Power On/Off Sequence

#### Timing Diagram for CH2 to CH5

Power On Sequence : CH2 Step-Down 3.3V $\rightarrow$ CH3 Step-Down 1.8V $\rightarrow$ CH4 Step-Down 1.2V $\rightarrow$ CH5 LDO 2.5V Power Off Sequence : CH5 LDO 2.5V $\rightarrow$ CH4 Step-Down 1.2V $\rightarrow$ CH3 Step-Down 1.8V $\rightarrow$ CH2 Step-Down 3.3V SEL = H, SEQ = H, EN3 = H, EN4 = L

Power On Sequence : CH2 Step-Down 3.3V→CH5 LDO 2.5V →CH3 Step-Down 1.8V→CH4 Step-Down 1.2V Power Off Sequence : CH4 Step-Down 1.2V→CH3 Step-Down 1.8V→CH5 LDO 2.5V →CH2 Step-Down 3.3V SEL = H, SEQ = H, EN3 = H, EN4 = L, EN5 = L

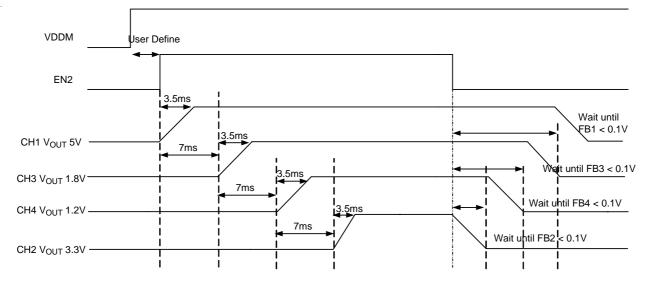

#### Power on/off sequence for CH1 to CH4

Sequence 3 : SEQ is high, EN3 is high, EN4 is high.

EN2 will turn on/off CH1 to CH4 in preset sequence. CH5 will be turned on by EN5 independently.

CH1 to CH4 Power On Sequence is :

When EN2 goes high, CH1 will be turned on. 7ms after CH1 is turned on, CH3 will be turned on. 7ms after CH3 is turned on, CH4 will be turned on. 7ms after CH4 is turned on, CH2 will be turned on.

CH1 to CH4 Power-Off Sequence is :

When EN2 goes low, CH2 will turn off first and internally discharge output. When FB2 < 0.1V, CH4 will turn off and also internally discharge output via LX4 pin. When FB4 < 0.1V, CH3 will turn off and internally discharge output via LX3 pin. Likewise, when FB3 < 0.1V, CH1 will turn off and discharge output via LX1 pin. After FB1 < 0.1V, CH1 to 4 shutdown sequence will be completed.

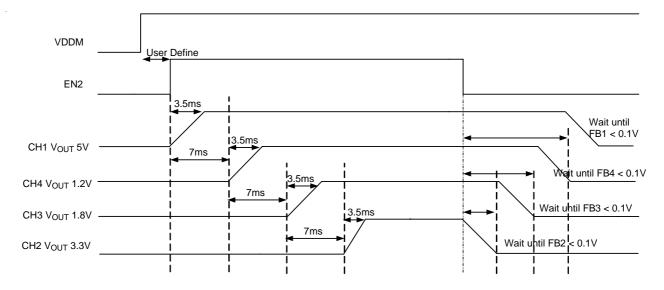

Sequence 4 : SEQ is high, EN3 is low, EN4 is high.

EN2 will turn on/off CH1 to CH4 in preset sequence. CH5 will be turned on by EN5 independently.

CH1 to CH4 Power On Sequence is :

When EN2 goes high, CH1 will be turned on first. 7ms after CH1 is turned on, CH4 will be turned on. 7ms after CH4 is turned on, CH3 will be turned on. 7ms after CH3 is turned on, CH2 will be turned on.

CH1 to CH4 Power Off Sequence is :

When EN2 goes low, CH2 will turn off first and internally discharge output. When FB2 < 0.1V, CH3 will turn off and internally discharge output via LX3 pin. When FB3 < 0.1V, CH4 will turn off and internally discharge output via LX4 pin. Likewise when FB4 < 0.1V, CH1 will turn off and internally discharge output via LX1 pin. After FB1 < 0.1V, Ch1 to 4 shutdown sequence is completed.

| Enable Setting            | Power On Sequence                                     |

|---------------------------|-------------------------------------------------------|

| EN3 = H, EN4 = H, EN1 = X | $CH1 \rightarrow CH3 \rightarrow CH4 \rightarrow CH2$ |

| EN3 = L, EN4 = H, EN5 = X | $CH1 \rightarrow CH4 \rightarrow CH3 \rightarrow CH2$ |

| Enable Setting            | Power Off Sequence                                    |

|                           |                                                       |

| EN3 = H, EN4 = H, EN5 = X | CH2→CH4→CH3→CH1                                       |

#### Table 5. CH1 to CH4 Power On/Off Sequence

#### Timing Diagram for CH1 to CH4

Power On Sequence : CH1 Step-Up 5V $\rightarrow$ CH3 Step-Down 1.8V $\rightarrow$ CH4 Step-Down 1.2V $\rightarrow$ CH2 Step-Up 3.3V Power Off Sequence : CH2 Step-Up 3.3V $\rightarrow$ CH4 Step-Down 1.2V $\rightarrow$ CH3 Step-Down 1.8V $\rightarrow$ CH1 Step-Up 5V SEL = L, SEQ = H, EN3 = H, EN4 = H

Power On Sequence : CH1 Step-Up 5V →CH4 Step-Down 1.2V →CH3 Step-Down 1.8V →CH2 Step-Up 3.3V Power Off Sequence : CH2 Step-Up 3.3V →CH3 Step-Down 1.8V →CH4 Step-Down 1.2V →CH1 Step-Up 5V SEL = L, SEQ = H, EN3 = L, EN4 = H

#### **Thermal Considerations**

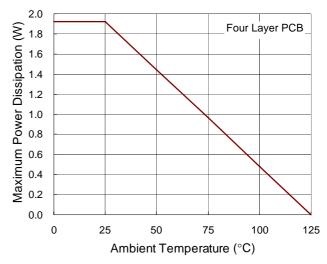

For continuous operation, do not exceed absolute maximum junction temperature. The maximum power dissipation depends on the thermal resistance of the IC package, PCB layout, rate of surrounding airflow, and difference between junction and ambient temperature. The maximum power dissipation can be calculated by the following formula :

#### $\mathsf{P}_{\mathsf{D}(\mathsf{MAX})} = (\mathsf{T}_{\mathsf{J}(\mathsf{MAX})} - \mathsf{T}_{\mathsf{A}}) / \theta_{\mathsf{J}\mathsf{A}}$

where  $T_{J(MAX)}$  is the maximum junction temperature,  $T_A$  is the ambient temperature, and  $\theta_{JA}$  is the junction to ambient thermal resistance.

For recommended operating condition specifications of the RT9992, the maximum junction temperature is 125°C and T<sub>A</sub> is the ambient temperature. The junction to ambient thermal resistance,  $\theta_{JA}$ , is layout dependent. For WQFN-32L 4x4 packages, the thermal resistance,  $\theta_{JA}$ , is 52°C/W on a standard JEDEC 51-7 four-layer thermal test board. The maximum power dissipation at T<sub>A</sub>=25°C can be calculated by the following formula :

$P_{D(MAX)}$  = (125°C - 25°C ) / (52°C/W) = 1.923W for WQFN-32L 4x4 package

The maximum power dissipation depends on the operating ambient temperature for fixed  $T_{J(\text{MAX})}$  and thermal

resistance,  $\theta_{JA}$ . For the RT9992 package, the derating curve in Figure 1 allows the designer to see the effect of rising ambient temperature on the maximum power dissipation.

Figure 1. Derating Curve for the RT9992 Package

|                       | Protection Type | Table 6. Protection A<br>Threshold(typical) Refer                              | Delay Time       | Protection                     |  |

|-----------------------|-----------------|--------------------------------------------------------------------------------|------------------|--------------------------------|--|

|                       | ,,              | to Electrical spec                                                             | ,                | Methods                        |  |

| V <sub>DDM</sub>      | UVLO            | VDDM < 2.1V                                                                    | No delay         | Disable all channels           |  |

| ▼ DDM                 | OVP             | VDDM > 6.15V                                                                   | 100ms            | IC shutdown                    |  |

| BAT                   | UVLO            | V <sub>BAT</sub> < 1.3V                                                        | No delay         | Disable all channels           |  |

| CH1 :<br>Boost        | Current Limit   | N-MOSFET current > 3A                                                          | 100ms            | IC shutdown                    |  |

|                       | PVDD1 UVP       | $V_{FB1} < 0.4V$ , or<br>$V_{PVDD1} < V_{BAT}-0.8V$ or<br>$V_{PVDD1} < 1.3V$   | 100ms            | IC shutdown                    |  |

|                       | PVDD1 OVP       | V <sub>PVDD1</sub> > 6.15V                                                     | No delay         | IC shutdown                    |  |

|                       | Current Limit   | N-MOSFET current > 2.1A                                                        | 100ms            | IC shutdown                    |  |

| CH2 :<br>Boost        | PVDD2 UVP       | $V_{FB2} < 0.4V$ , or<br>$V_{PVDD2} < V_{IN2} - 0.8V$ or<br>$V_{PVDD2} < 1.3V$ | 100ms            | IC shutdown                    |  |

|                       | PVDD2 OVP       | V <sub>PVDD2</sub> > 6.15V                                                     | No delay         | IC shutdown                    |  |

| CH2 : Buck            | OCP             | P-MOSFET current > 1.5A                                                        | 100ms            | IC shutdown                    |  |

| CH2. BUCK             | UVP             | V <sub>FB2</sub> < 0.4V                                                        | 100ms            | IC shutdown                    |  |

| CH3 : Buck            | OCP             | P-MOSFET current > 1.5A                                                        | 100ms            | IC shutdown                    |  |

|                       | UVP             | V <sub>FB3</sub> < 0.4V                                                        | 100ms            | IC shutdown                    |  |

| CH4 : Buck            | OCP             | P-MOSFET current > 2A                                                          | 100ms            | IC shutdown                    |  |

|                       | UVP             | V <sub>FB4</sub> < 0.4V                                                        | 100ms            | IC shutdown                    |  |

| CH5                   | Current Limit   | P-MOSFET current > 0.3A                                                        | 100ms            | IC shutdown                    |  |

|                       | UVP             | V <sub>FB5</sub> < 0.3V                                                        | 100ms            | IC shutdown                    |  |

| CH6 Asyn              | Current Limit   | N-MOSFET current > 0.8A                                                        | Reset each cycle |                                |  |

| Boost                 | OVP             | Voute > 19V                                                                    | 100ms            | IC shutdown                    |  |

| Thermal Thermal Tempe |                 | Temperature > 160°C                                                            | No delay         | All channels stop<br>switching |  |

#### **Table 6. Protection Action**

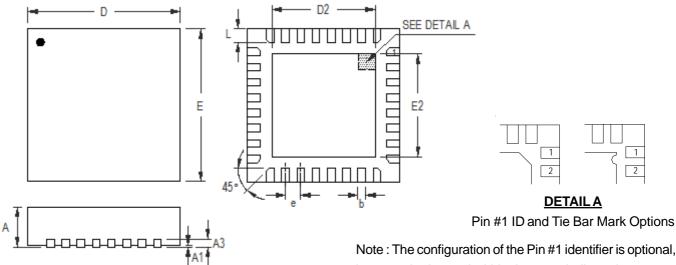

### **Outline Dimension**

Note : The configuration of the Pin #1 identifier is optional, but must be located within the zone indicated.

| Or much a l | Dimensions | In Millimeters | <b>Dimensions In Inches</b> |       |  |

|-------------|------------|----------------|-----------------------------|-------|--|

| Symbol      | Min        | Max            | Min                         | Мах   |  |

| А           | 0.700      | 0.800          | 0.028                       | 0.031 |  |

| A1          | 0.000      | 0.050          | 0.000                       | 0.002 |  |

| A3          | 0.175      | 0.250          | 0.007                       | 0.010 |  |

| b           | 0.150      | 0.250          | 0.006                       | 0.010 |  |

| D           | 3.900      | 4.100          | 0.154                       | 0.161 |  |

| D2          | 2.650      | 2.750          | 0.104                       | 0.108 |  |

| E           | 3.900      | 4.100          | 0.154                       | 0.161 |  |

| E2          | 2.650      | 2.750          | 0.104                       | 0.108 |  |

| е           | 0.4        | 100            | 0.0                         | 020   |  |

| L           | 0.300      | 0.400          | 0.012                       | 0.016 |  |

W-Type 32L QFN 4x4 Package

### **Richtek Technology Corporation**

Headquarter 5F, No. 20, Taiyuen Street, Chupei City Hsinchu, Taiwan, R.O.C. Tel: (8863)5526789 Fax: (8863)5526611

#### **Richtek Technology Corporation**

Taipei Office (Marketing) 8F, No. 137, Lane 235, Paochiao Road, Hsintien City Taipei County, Taiwan, R.O.C. Tel: (8862)89191466 Fax: (8862)89191465 Email: marketing@richtek.com

Information that is provided by Richtek Technology Corporation is believed to be accurate and reliable. Richtek reserves the right to make any change in circuit design, specification or other related things if necessary without notice at any time. No third party intellectual property infringement of the applications should be guaranteed by users when integrating Richtek products into any application. No legal responsibility for any said applications is assumed by Richtek.

### **Datasheet Revision History**

| Version     | Data      | Page No. | ltem                         | Description                            |

|-------------|-----------|----------|------------------------------|----------------------------------------|

| P00         | 2010/2/1  |          |                              | First Edition                          |

|             |           |          | Typical Application Circuit  |                                        |

| P01         | 2010/3/2  |          | Function Block Diagram       | Modify                                 |

|             |           |          | Electrical Characteristics   |                                        |

|             |           |          | General Description          |                                        |

|             |           |          | Typical Application Circuit. |                                        |

| P02         | 2010/3/19 |          | Functional Pin Description   | Modify and add Application Information |

|             |           |          | Absolute Maximum Ratings     |                                        |

|             |           |          | Application Information      |                                        |

| P03         | 2010/4/2  |          | Outline Dimension            | Modify                                 |

| <b>D</b> 04 |           | 010/5/20 | Ordering Information         |                                        |

|             | 2010/5/20 |          | Typical Application Circuit  | Modifi                                 |

| P04         |           |          | Electrical Characteristics   | Modify                                 |

|             |           |          | Application Information      |                                        |