Click to view price, real time Inventory, Delivery & Lifecycle Information ;

# ADS7951QDBTRQ1

## **Texas instruments**

Analog to Digital Converters - ADC Auto 12bit, 1 MSPS 8Ch Sngend, SAR ADC

Any questions, please feel free to contact us. info@kaimte.com

Sample &

Buy

Technical Documents

TEXAS INSTRUMENTS

ADS7950-Q1, ADS7951-Q1, ADS7952-Q1, ADS7953-Q1, ADS7954-Q1 ADS7956-Q1, ADS7957-Q1, ADS7958-Q1, ADS7959-Q1, ADS7960-Q1, ADS7961-Q1

Tools &

Software

SBAS652A - MAY 2014 - REVISED AUGUST 2014

### ADS79xx-Q1 8-, 10-, and 12-Bit, 1-MSPS, 4-, 8-, 12-, and 16-Channel, Single-Ended, Micropower, Serial Interface, Analog-to-Digital Converters

#### 1 Features

- Qualified for Automotive Applications

- AEC-Q100 Tested with the Following Results:

- Device Temperature Grade 1: –40°C to 125°C Ambient Operating Temperature Range

- Device HBM ESD Classification Level H2

- Device CDM ESD Classification Level C4B

- Product Family:

- 8-, 10-, and 12-Bit Resolution

- 4-, 8-, 12-Channel Devices Share 16-Channel Footprint

- 1-MHz Sample-Rate Serial Devices

- Analog Supply Range: 2.7 V to 5.25 V

- I/O Supply Range: 1.7 V to 5.25 V

- Two SW-Selectable Unipolar, Input Ranges:

(0 V to 2.5 V) or (0 V to 5 V)

- Auto and Manual Modes for Channel Selection

- Two Programmable Alarm Levels per Channel

- Four Individually Configurable GPIOs

- Typical Power Dissipation: 14.5 mW (V<sub>(+VA)</sub> = 5 V, V<sub>(+VBD)</sub> = 3 V) at 1 MSPS

- Power-Down Current (1 μA)

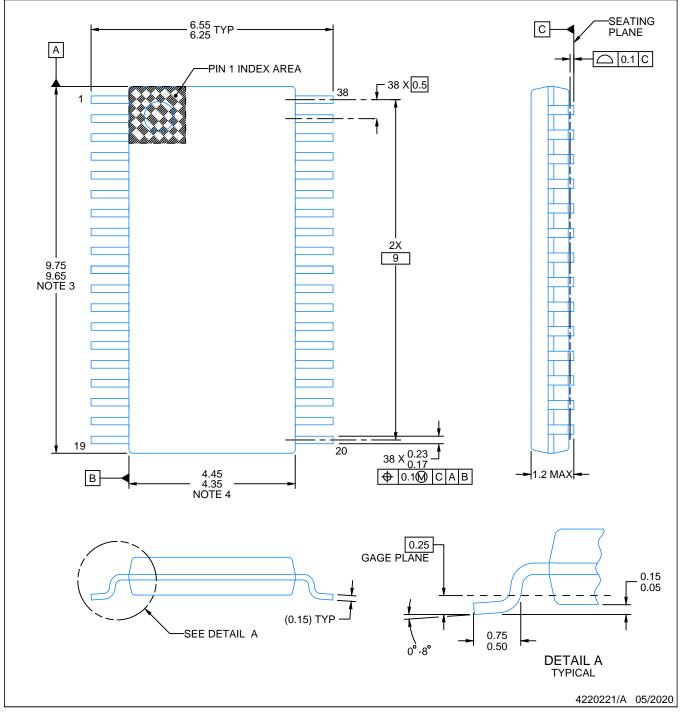

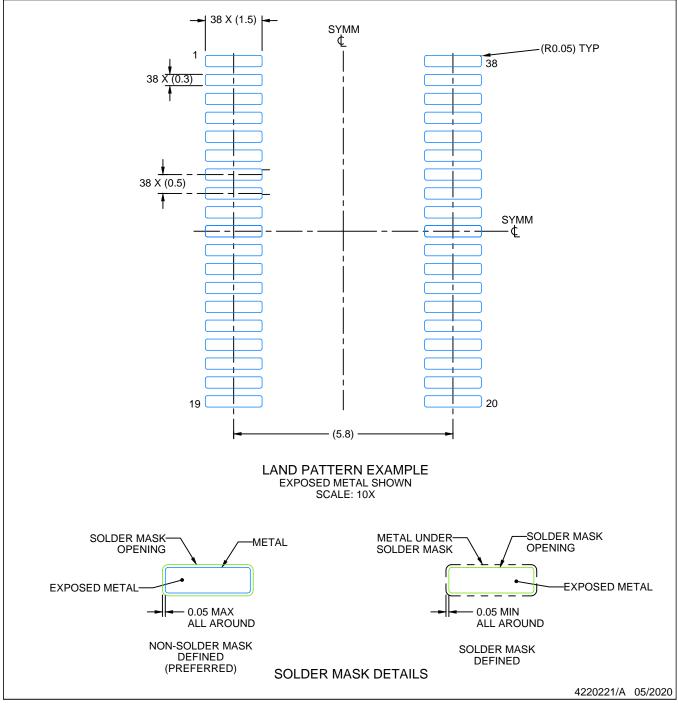

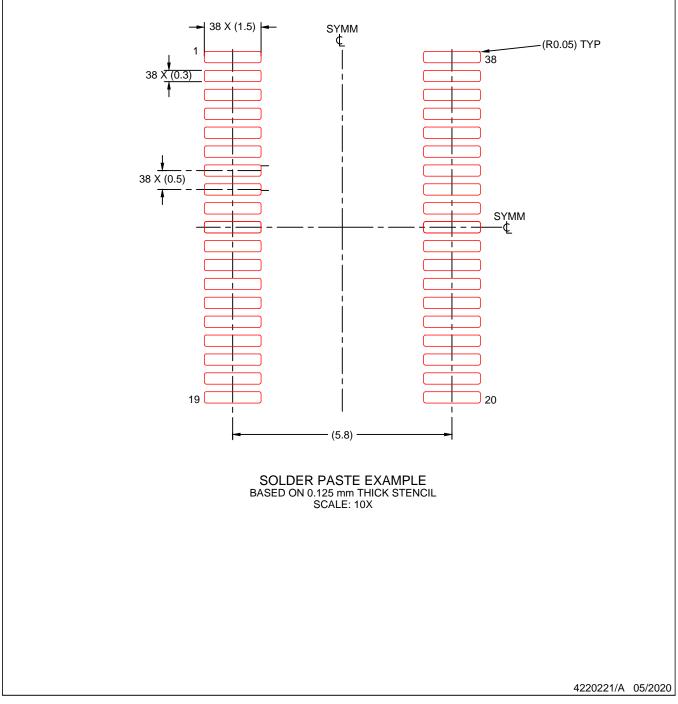

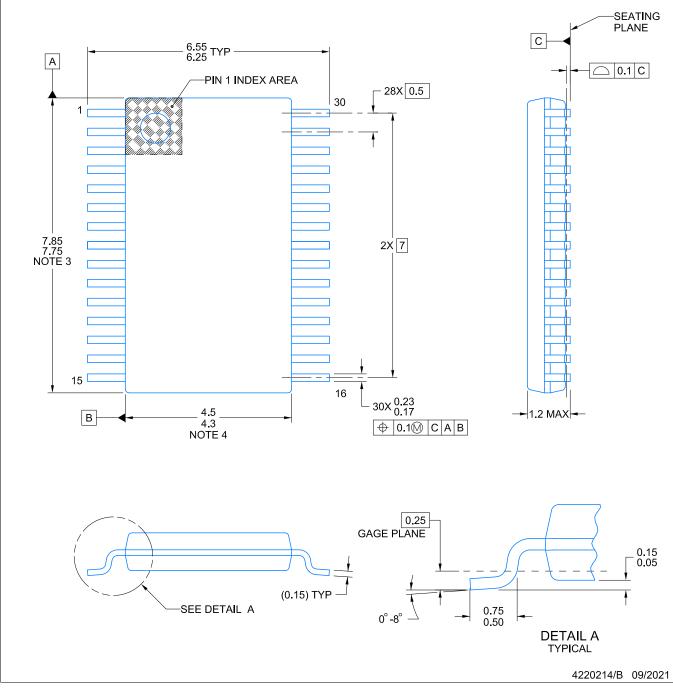

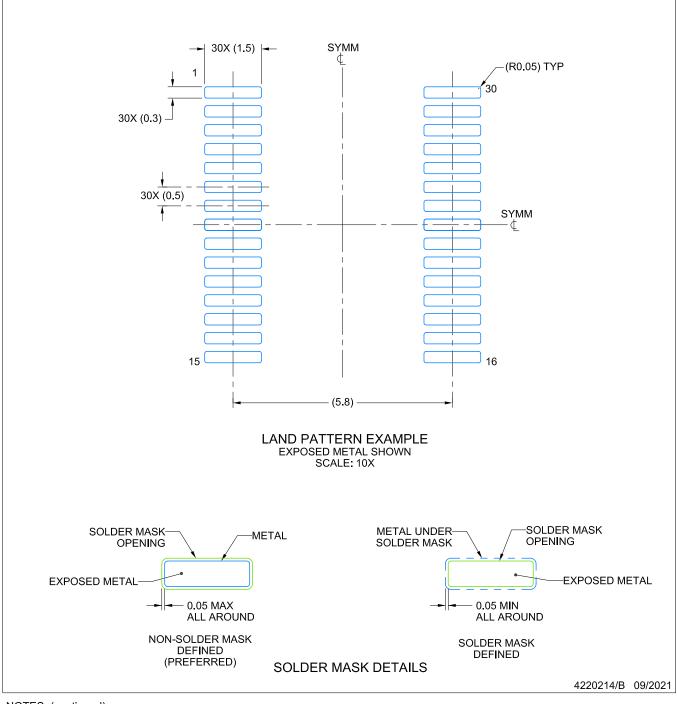

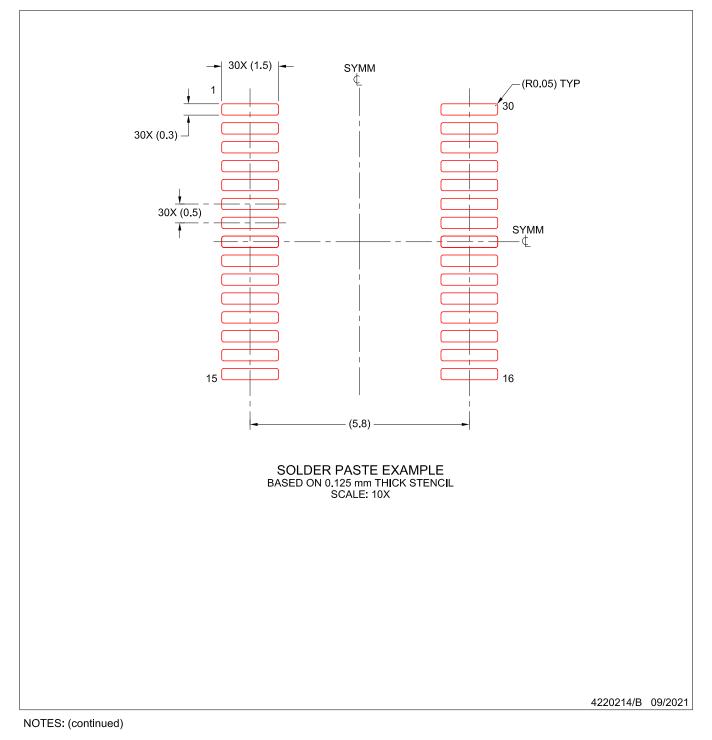

- 30-Pin and 38-Pin TSSOP Package

### 2 Applications

- Automotive Systems

- Power Supply Monitoring

- Battery-Powered Systems

- High-Speed, Data-Acquisition Systems

### 3 Description

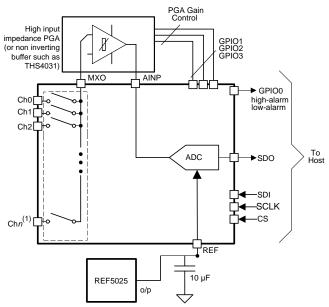

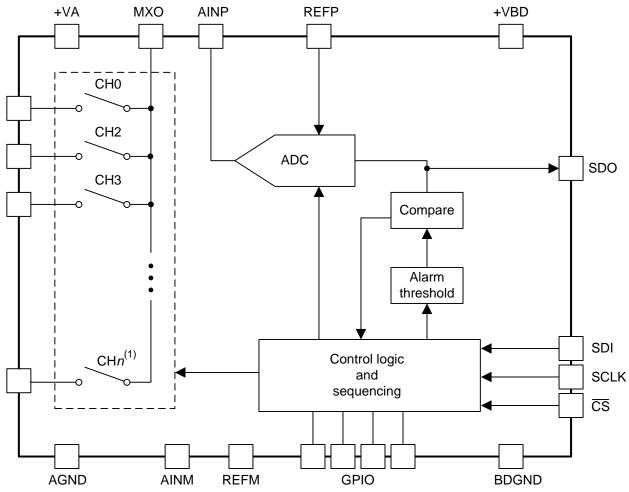

The ADS79xx-Q1 device family consists of multichannel 8-bit, 10-bit and 12-bit analog-to-digital converters (ADCs). The devices include a capacitor-based successive approximation register (SAR) ADC with inherent sample and hold. Multiple features and great performance makes the ADS79xx-Q1 device useful for wide variety of applications where multiple channels should be monitored.

The ADS79xx-Q1 device works on a wide analogsupply range from 2.7 V to 5.25 V. These devices are suitable for battery-powered and isolated powersupply applications because of very-low power consumption.

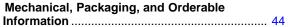

The 4- and 8-channel devices are available in 30-pin TSSOP package. The 12- and 16-channel devices are available in 38-pin TSSOP package.

| DEVICE NAME | PACKAGE    | BODY SIZE         |  |  |

|-------------|------------|-------------------|--|--|

| ADS7950-Q1  |            |                   |  |  |

| ADS7951-Q1  |            |                   |  |  |

| ADS7954-Q1  | TSSOP (30) | 7.80 mm × 4.40 mm |  |  |

| ADS7958-Q1  |            |                   |  |  |

| ADS7959-Q1  |            |                   |  |  |

| ADS7952-Q1  |            |                   |  |  |

| ADS7953-Q1  |            |                   |  |  |

| ADS7956-Q1  |            | 0.70 mm + 4.40 mm |  |  |

| ADS7957-Q1  | TSSOP (38) | 9.70 mm × 4.40 mm |  |  |

| ADS7960-Q1  |            |                   |  |  |

| ADS7961-Q1  |            |                   |  |  |

(1) For all available packages, see the orderable addendum at the end of the datasheet.

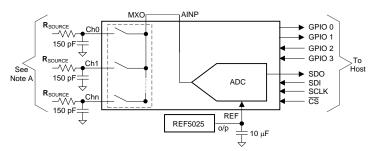

#### **Detailed Block Diagram**

An IMPORTANT NOTICE at the end of this data sheet addresses availability, warranty, changes, use in safety-critical applications, intellectual property matters and other important disclaimers. PRODUCTION DATA.

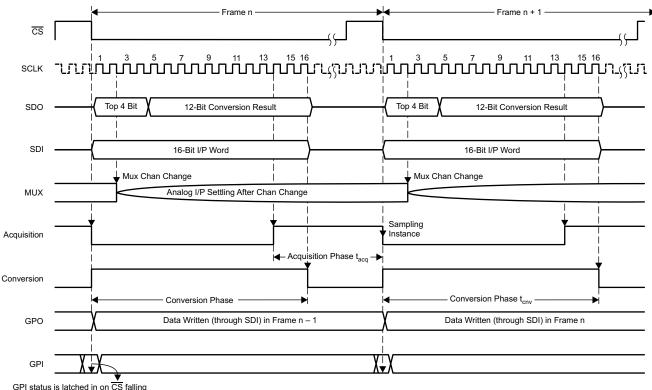

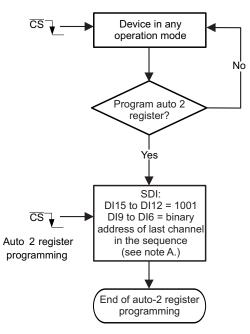

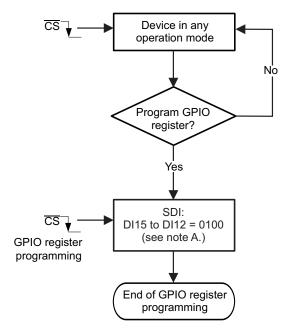

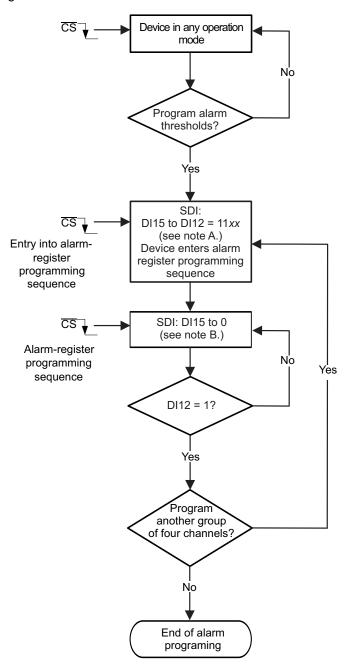

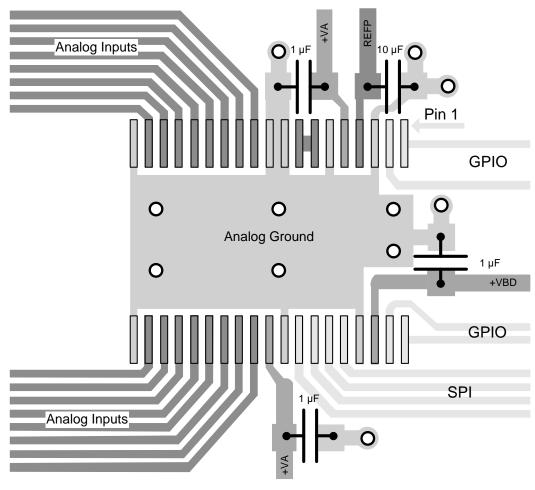

8.2 Functional Block Diagram ...... 20 8.3 Feature Description...... 21 8.5 Digital Output Code...... 35 8.6 Programming: GPIO...... 36

Application and Implementation ...... 40 9.1 Application Information..... 40 9.2 Typical Applications ..... 40 9.3 Do's and Don'ts..... 42 10 Power-Supply Recommendations ...... 42 11 Layout...... 43 11.1 Layout Guidelines ...... 43 11.2 Layout Example ..... 43 12 Device and Documentation Support ...... 44 12.1 Documentation Support ...... 44 12.2 Related Links ...... 44 12.3 Trademarks ...... 44 12.4 Electrostatic Discharge Caution ...... 44 12.5 Glossary ...... 44

13 Mechanical, Packaging, and Orderable

#### www.ti.com

### **Table of Contents**

8.1

9

| 1 | Fea  | tures 1                                                                        |

|---|------|--------------------------------------------------------------------------------|

| 2 | Арр  | lications 1                                                                    |

| 3 | Des  | cription 1                                                                     |

| 4 | Rev  | ision History 2                                                                |

| 5 |      | ice Comparison Table 3                                                         |

| 6 | Pin  | Configurations and Functions 3                                                 |

| 7 | Spe  | cifications5                                                                   |

|   | 7.1  | Absolute Maximum Ratings 5                                                     |

|   | 7.2  | Handling Ratings 5                                                             |

|   | 7.3  | Recommended Operating Conditions 6                                             |

|   | 7.4  | Thermal Information 6                                                          |

|   | 7.5  | Electrical Characteristics: ADS7950-Q1, ADS7951-<br>Q1, ADS7952-Q1, ADS7953-Q1 |

|   | 7.6  | Electrical Characteristics: ADS7954-Q1, ADS7956-<br>Q1, ADS7957-Q1             |

|   | 7.7  | Electrical Characteristics: ADS7958-Q1, ADS7959-<br>Q1, ADS7960-Q1, ADS7961-Q1 |

|   | 7.8  | Timing Requirements 11                                                         |

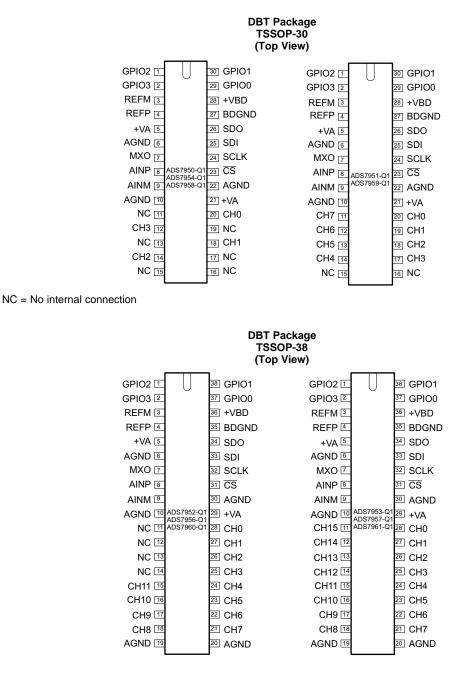

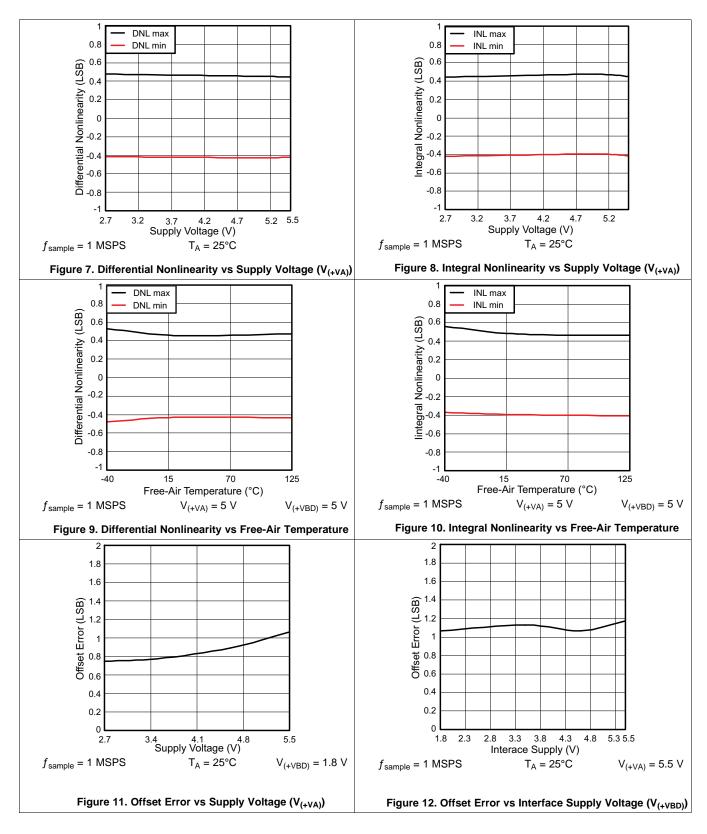

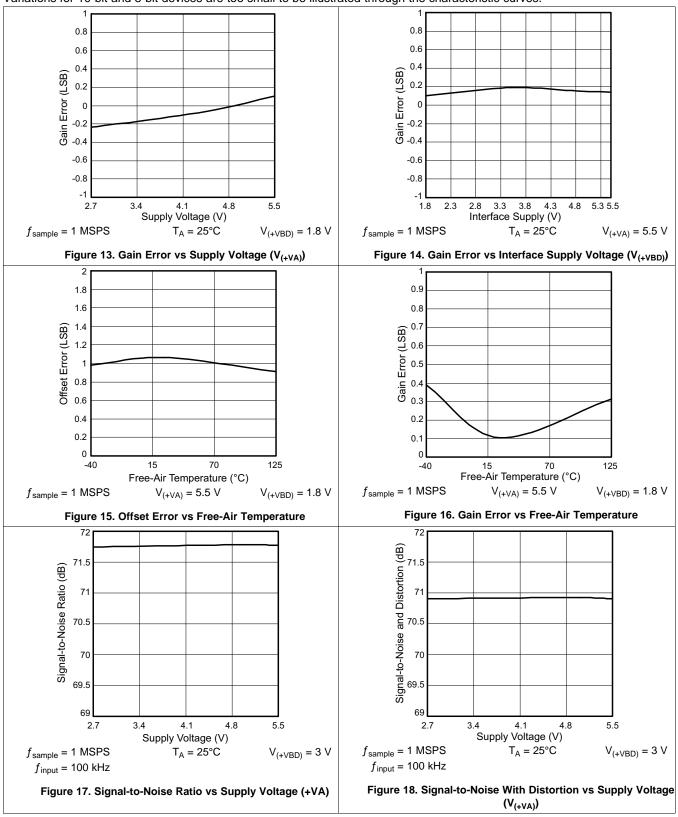

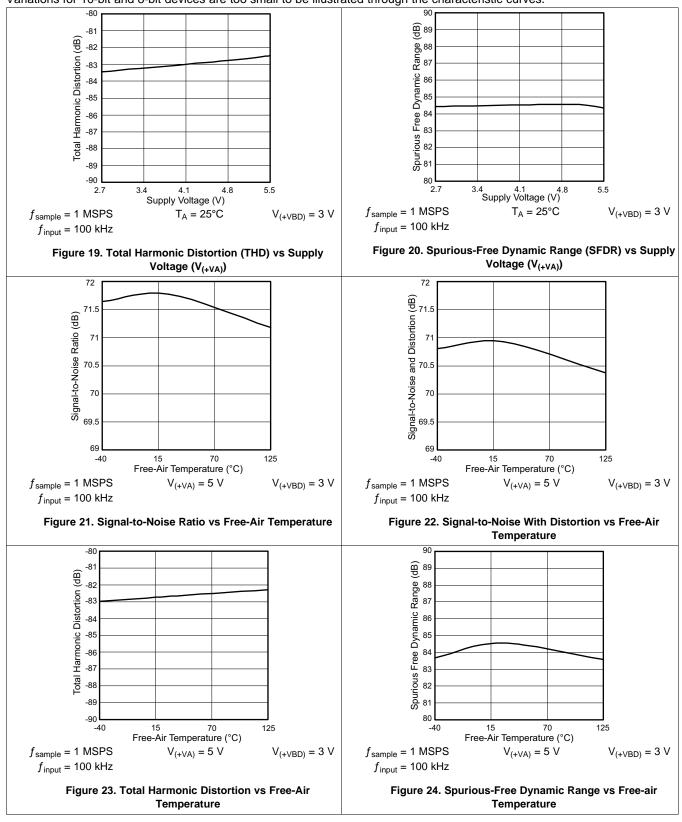

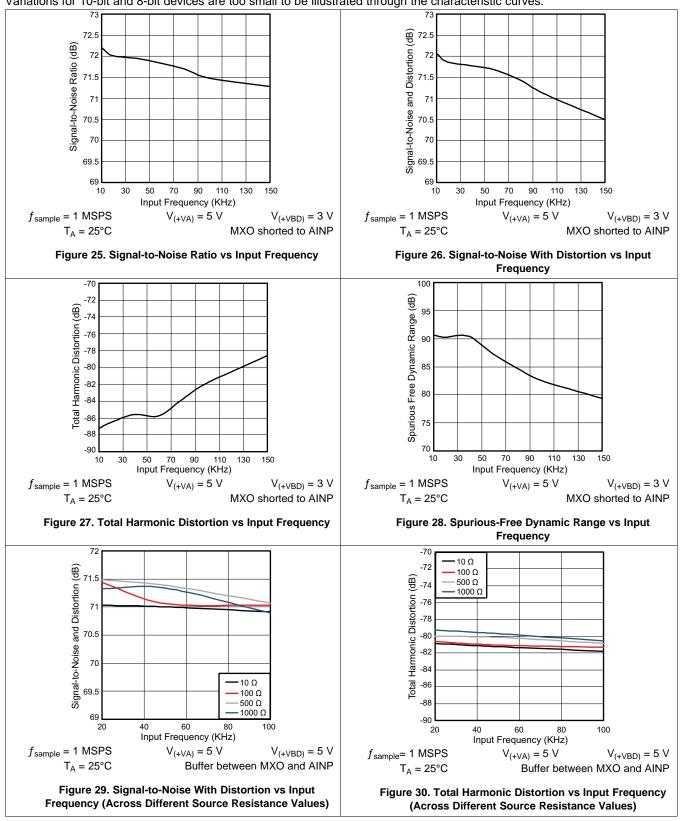

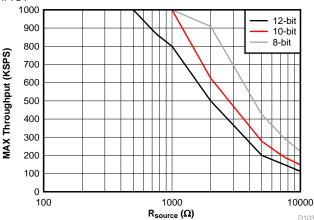

|   | 7.9  | Typical Characteristics (All ADS79xx-Q1 Family Devices)                        |

|   |      | Typical Characteristics (12-Bit Devices Only) 13                               |

| 8 | Deta | ailed Description 20                                                           |

### 4 Revision History

| C | hanges from Original (May 2014) to Revision A         | Page |

|---|-------------------------------------------------------|------|

| • | Added all devices to Device Information table         | 1    |

| • | Deleted Device Comparison Table footnote              | 3    |

| • | Changed entire Application and Implementation section |      |

Submit Documentation Feedback Product Folder Links: ADS7950-Q1 ADS7951-Q1 ADS7952-Q1 ADS7953-Q1 ADS7954-Q1 ADS7956-Q1 ADS7957-Q1 ADS7958-Q1 ADS7959-Q1 ADS7960-Q1 ADS7961-Q1

Copyright © 2014, Texas Instruments Incorporated

#### 5 Device Comparison Table

|                    |                     | RESOLUTION   |            |  |  |  |  |  |

|--------------------|---------------------|--------------|------------|--|--|--|--|--|

| NUMBER OF CHANNELS | 12 BIT 10 BIT 8 BIT |              |            |  |  |  |  |  |

| 4                  | ADS7950-Q1          | ADS7954-Q1   | ADS7958-Q1 |  |  |  |  |  |

| 8                  | ADS7951-Q1          | ADS7951-Q1 — |            |  |  |  |  |  |

| 12                 | ADS7952-Q1          | ADS7956-Q1   | ADS7960-Q1 |  |  |  |  |  |

| 16                 | ADS7953-Q1          | ADS7957-Q1   | ADS7961-Q1 |  |  |  |  |  |

#### 6 Pin Configurations and Functions

Copyright © 2014, Texas Instruments Incorporated

Submit Documentation Feedback

SBAS652A - MAY 2014 - REVISED AUGUST 2014

|                      |                                          |                                          |                           | Pin Fu                                   | incti | ions                                                                                                                              |  |

|----------------------|------------------------------------------|------------------------------------------|---------------------------|------------------------------------------|-------|-----------------------------------------------------------------------------------------------------------------------------------|--|

|                      |                                          | PIN                                      |                           |                                          |       |                                                                                                                                   |  |

|                      |                                          | NUM                                      | MBER                      |                                          |       |                                                                                                                                   |  |

| NAME                 | ADS7953-Q1,<br>ADS7957-Q1,<br>ADS7961-Q1 | ADS7952-Q1,<br>ADS7956-Q1,<br>ADS7960-Q1 | ADS7951-Q1,<br>ADS7959-Q1 | ADS7950-Q1,<br>ADS7954-Q1,<br>ADS7958-Q1 | I/O   | DESCRIPTION                                                                                                                       |  |

| ADC ANALO            | G INPUT                                  |                                          |                           |                                          |       |                                                                                                                                   |  |

| AINM                 | 9                                        | 9                                        | 9                         | 9                                        | Ι     | ADC input ground                                                                                                                  |  |

| AINP                 | 8                                        | 8                                        | 8                         | 8                                        | Ι     | Signal input to ADC                                                                                                               |  |

| DIGITAL CO           | NTROL SIGNAL                             | S                                        |                           |                                          |       |                                                                                                                                   |  |

| CS                   | 31                                       | 31                                       | 23                        | 23                                       | Ι     | Chip-select input                                                                                                                 |  |

| SCLK                 | 32                                       | 32                                       | 24                        | 24                                       | Ι     | Serial clock input                                                                                                                |  |

| SDI                  | 33                                       | 33                                       | 25                        | 25                                       | Ι     | Serial data input                                                                                                                 |  |

| SDO                  | 34                                       | 34                                       | 26                        | 26                                       | 0     | Serial data output                                                                                                                |  |

| GENERAL P            | URPOSE INPUT                             | S AND OUTPU                              | TS <sup>(1)</sup>         |                                          |       |                                                                                                                                   |  |

| GPIO0                |                                          |                                          |                           |                                          | I/O   | General-purpose input or output                                                                                                   |  |

| High or low<br>alarm | 37                                       | 37                                       | 29                        | 29                                       | 0     | Active high output indicating high alarm or low alarm, depending on programming                                                   |  |

| GPIO1                | 38                                       | 38                                       | 30                        | 30                                       | I/O   | General-purpose input or output<br>Active high output indicating low alarm<br>General-purpose input or output                     |  |

| Low alarm            | 30                                       | 30                                       |                           |                                          | 0     | General-purpose input or output                                                                                                   |  |

| GPIO2                | 4                                        |                                          | 1                         | 1                                        | I/O   | General-purpose input or outputSelects range: High $\rightarrow$ Range 2; Low $\rightarrow$ Range 1Genera-purpose input or output |  |

| Range                | 1                                        | 1                                        | 1                         | I                                        | Ι     |                                                                                                                                   |  |

| GPIO3                | 2                                        | 0                                        | 0                         | 2                                        | I/O   |                                                                                                                                   |  |

| PD                   | 2                                        | 2                                        | 2                         | 2                                        | Ι     | Active low power-down input                                                                                                       |  |

| MULTIPLEXE           | ĒR                                       |                                          | •                         | •                                        |       |                                                                                                                                   |  |

| Ch0                  | 28                                       | 28                                       | 20                        | 20                                       | Ι     |                                                                                                                                   |  |

| Ch1                  | 27                                       | 27                                       | 19                        | 18                                       | Ι     |                                                                                                                                   |  |

| Ch2                  | 26                                       | 26                                       | 18                        | 14                                       | Ι     |                                                                                                                                   |  |

| Ch3                  | 25                                       | 25                                       | 17                        | 12                                       | Ι     |                                                                                                                                   |  |

| Ch4                  | 24                                       | 24                                       | 14                        | _                                        | Ι     |                                                                                                                                   |  |

| Ch5                  | 23                                       | 23                                       | 13                        | _                                        | Ι     |                                                                                                                                   |  |

| Ch6                  | 22                                       | 22                                       | 12                        | _                                        | Ι     |                                                                                                                                   |  |

| Ch7                  | 21                                       | 21                                       | 11                        | _                                        | Ι     |                                                                                                                                   |  |

| Ch8                  | 18                                       | 18                                       | —                         | _                                        | Ι     | Analog channels for multiplexer                                                                                                   |  |

| Ch9                  | 17                                       | 17                                       | —                         | _                                        | Ι     |                                                                                                                                   |  |

| Ch10                 | 16                                       | 16                                       | —                         | —                                        | Ι     |                                                                                                                                   |  |

| Ch11                 | 15                                       | 15                                       | —                         | _                                        | Ι     |                                                                                                                                   |  |

| Ch12                 | 14                                       | _                                        | _                         | _                                        | Ι     |                                                                                                                                   |  |

| Ch13                 | 13                                       | -                                        | —                         | _                                        | Ι     |                                                                                                                                   |  |

| Ch14                 | 12                                       | _                                        | _                         | _                                        | Ι     |                                                                                                                                   |  |

| Ch15                 | 11                                       | _                                        | _                         | _                                        | Ι     |                                                                                                                                   |  |

| МХО                  | 7                                        | 7                                        | 7                         | 7                                        | 0     | Multiplexer output                                                                                                                |  |

| NC PINS              |                                          |                                          | ı                         | 1                                        |       |                                                                                                                                   |  |

|                      | _                                        | 11                                       | 15                        | 11                                       |       |                                                                                                                                   |  |

|                      |                                          | 12                                       | 16                        | 13                                       |       |                                                                                                                                   |  |

| 13 — 15              |                                          |                                          |                           |                                          |       |                                                                                                                                   |  |

| NC                   |                                          | 14                                       | _                         | 16                                       | —     | Pins internally not connected, do not float these pins                                                                            |  |

|                      |                                          | _                                        | _                         | 17                                       |       |                                                                                                                                   |  |

|                      |                                          | _                                        | _                         | 19                                       |       |                                                                                                                                   |  |

(1) These pins have programmable dual functionality. See Table 12 for functionality programming.

4

Copyright © 2014, Texas Instruments Incorporated

#### SBAS652A - MAY 2014 - REVISED AUGUST 2014

#### Pin Functions (continued)

|          | PIN                                      |                                          |                           |                                          |                 |                     |  |

|----------|------------------------------------------|------------------------------------------|---------------------------|------------------------------------------|-----------------|---------------------|--|

|          |                                          | NUMBER                                   |                           |                                          |                 |                     |  |

| NAME     | ADS7953-Q1,<br>ADS7957-Q1,<br>ADS7961-Q1 | ADS7952-Q1,<br>ADS7956-Q1,<br>ADS7960-Q1 | ADS7951-Q1,<br>ADS7959-Q1 | ADS7950-Q1,<br>ADS7954-Q1,<br>ADS7958-Q1 | I/O             | DESCRIPTION         |  |

| POWER SU | OWER SUPPLY AND GROUND                   |                                          |                           |                                          |                 |                     |  |

|          | 6                                        | 6                                        | 6                         | 6                                        |                 |                     |  |

|          | 10                                       | 10                                       | 10                        | 10                                       |                 |                     |  |

| AGND     | 19                                       | 19                                       | 22                        | 22                                       | — Analog ground | Analog ground       |  |

|          | 20                                       | 20                                       | —                         | _                                        |                 |                     |  |

|          | 30                                       | 30                                       | —                         | —                                        |                 |                     |  |

| BDGND    | 35                                       | 35                                       | 27                        | 27                                       |                 | Digital ground      |  |

| +VA      | 5                                        | 5                                        | 5                         | 5                                        |                 |                     |  |

| +vA      | 29                                       | 29                                       | 21                        | 21                                       | _               | Analog power supply |  |

| +VBD     | 36                                       | 36                                       | 28                        | 28                                       |                 | Digital I/O supply  |  |

| REFERENC | E                                        |                                          |                           |                                          |                 |                     |  |

| REFM     | 3                                        | 3                                        | 3                         | 3                                        | Ι               | Reference ground    |  |

| REFP     | 4                                        | 4                                        | 4                         | 4                                        | Ι               | Reference input     |  |

#### 7 Specifications

#### 7.1 Absolute Maximum Ratings<sup>(1)</sup>

over operating free-air temperature range (unless otherwise noted).

|                                      |                            | MIN  | MAX                      | UNIT |

|--------------------------------------|----------------------------|------|--------------------------|------|

| Supply voltage to ground             | +VA to AGND, +VBD to BDGND | -0.3 | 7                        | V    |

| Signal input                         | AINP or CHn to AGND        | -0.3 | $V_{(+VA)} + 0.3$        | V    |

| Digital input                        | To BDGND                   | -0.3 | 7                        | V    |

| Digital output                       | To BDGND                   | -0.3 | V <sub>(+VA)</sub> + 0.3 | V    |

| Junction temperature, T <sub>J</sub> |                            |      | 150                      | °C   |

(1) Stresses beyond those listed as *absolute maximum ratings* may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated as *recommended operating conditions* is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

#### 7.2 Handling Ratings

|                    |                         |                                                            |                                                                                                 | MIN  | MAX | UNIT |

|--------------------|-------------------------|------------------------------------------------------------|-------------------------------------------------------------------------------------------------|------|-----|------|

| T <sub>stg</sub>   | Storage temperatu       | re range                                                   |                                                                                                 | -65  | 150 | °C   |

|                    |                         | Human-body model (HBM), per                                | AEC Q100-002 <sup>(1)</sup> , level H2                                                          | -2   | 2   | kV   |

| V <sub>(ESD)</sub> | Electrostatic discharge | Charged-device model (CDM),<br>per AEC Q100-001, level C4B | Corner pins<br>(1, 15, 16, and 30 for 30-pin packages<br>1, 19, 20, and 38 for 38-pin packages) | -750 | 750 | V    |

|                    |                         |                                                            | All pins                                                                                        | -500 | 500 |      |

(1) AEC Q100-002 indicates HBM stressing is done in accordance with the ANSI/ESDA/JEDEC JS-001 specification.

Submit Documentation Feedback

Product Folder Links: ADS7950-Q1 ADS7951-Q1 ADS7952-Q1 ADS7953-Q1 ADS7954-Q1 ADS7956-Q1 ADS7957-Q1 ADS7958-Q1 ADS7959-Q1 ADS7960-Q1 ADS7961-Q1 5

#### TEXAS INSTRUMENTS

www.ti.com

#### ADS7950-Q1, ADS7951-Q1, ADS7952-Q1, ADS7953-Q1, ADS7954-Q1 ADS7956-Q1, ADS7957-Q1, ADS7958-Q1, ADS7959-Q1, ADS7960-Q1, ADS7961-Q1

SBAS652A - MAY 2014 - REVISED AUGUST 2014

#### 7.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

|                     |                             | MIN | NOM | MAX                | UNIT |

|---------------------|-----------------------------|-----|-----|--------------------|------|

| V <sub>(+VA)</sub>  | Analog power-supply voltage | 2.7 | 3.3 | 5.25               | V    |

| V <sub>(+VBD)</sub> | Digital I/O-supply voltage  | 1.7 | 3.3 | V <sub>(+VA)</sub> | V    |

| V <sub>(REF)</sub>  | Reference voltage           | 2   | 2.5 | 3                  | V    |

| $f_{(\rm SCLK)}$    | SCLK frequency              |     |     | 20                 | MHz  |

| T <sub>A</sub>      | Operating temperature range | -40 |     | 125                | °C   |

#### 7.4 Thermal Information

|                       |                                              | ADS7        | ADS79xx-Q1  |       |  |

|-----------------------|----------------------------------------------|-------------|-------------|-------|--|

|                       | THERMAL METRIC <sup>(1)</sup>                | DBT (TSSOP) | DBT (TSSOP) | UNIT  |  |

|                       |                                              | 38 PINS     | 30 PINS     |       |  |

| $R_{\theta JA}$       | Junction-to-ambient thermal resistance       | 83.6        | 89.8        |       |  |

| R <sub>0JC(top)</sub> | Junction-to-case (top) thermal resistance    | 29.8        | 22.9        |       |  |

| $R_{\theta JB}$       | Junction-to-board thermal resistance         | 44.7        | 43.1        | °C/W  |  |

| ΨJT                   | Junction-to-top characterization parameter   | 2.9         | 0.8         | °C/VV |  |

| Ψ <sub>JB</sub>       | Junction-to-board characterization parameter | 44.1        | 42.5        |       |  |

| R <sub>0JC(bot)</sub> | Junction-to-case (bottom) thermal resistance | n/a         | n/a         |       |  |

(1) For more information about traditional and new thermal metrics, see the IC Package Thermal Metrics application report, SPRA953.

#### 7.5 Electrical Characteristics: ADS7950-Q1, ADS7951-Q1, ADS7952-Q1, ADS7953-Q1

$V_{(+VA)} = 2.7$  V to 5.25 V,  $V_{(+VBD)} = 1.7$  V to  $V_{(+VA)}$ ,  $V_{ref} = 2.5$  V ± 0.1 V,  $T_A = -40^{\circ}$ C to 125°C,  $f_{sample} = 1$  MHz (unless otherwise noted)

|        | PARAMETER                            | TEST CONDITIONS                          | MIN  | ТҮР   | MAX                           | UNIT               |

|--------|--------------------------------------|------------------------------------------|------|-------|-------------------------------|--------------------|

| ANALO  | G INPUT                              |                                          | i.   |       |                               |                    |

|        | <b>F</b>                             | Range 1                                  | 0    |       | V <sub>ref</sub>              | V                  |

|        | Full-scale input span <sup>(1)</sup> | Range 2 while 2 × V <sub>ref</sub> ≤ +VA | 0    |       | 2 × V <sub>ref</sub>          | V                  |

|        |                                      | Range 1                                  | -0.2 |       | V <sub>ref</sub> + 0.2        | V                  |

|        | Absolute input range                 | Range 2 while 2 × V <sub>ref</sub> ≤ +VA | -0.2 |       | 2 × V <sub>ref</sub> +<br>0.2 | V                  |

|        | Input capacitance                    |                                          |      | 15    |                               | ρF                 |

|        | Input leakage current                | $T_A = 125^{\circ}C$                     |      | 61    |                               | nA                 |

| SYSTEM | I PERFORMANCE                        |                                          |      |       |                               |                    |

|        | Resolution                           |                                          |      | 12    |                               | Bits               |

|        | No missing codes                     |                                          | 11   |       |                               | Bits               |

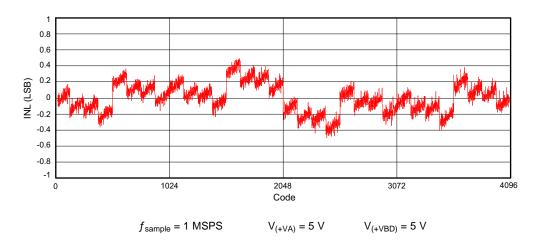

|        | Integral linearity                   |                                          | -1.5 | ±0.75 | 1.5                           | LSB <sup>(2)</sup> |

|        | Differential linearity               |                                          | -2   | ±0.75 | 1.5                           | LSB                |

|        | Offset error <sup>(3)</sup>          |                                          | -3.5 | ±1.1  | 3.5                           | LSB                |

|        |                                      | Range 1                                  | -2   | ±0.2  | 2                             | LSB                |

|        | Gain error                           | Range 2                                  |      | ±0.2  |                               | LSB                |

| TUE    | Total unadjusted error               |                                          |      | ±2    |                               | LSB                |

| SAMPLI | NG DYNAMICS                          |                                          |      |       |                               |                    |

|        | Conversion time                      | 20-MHz SCLK                              |      |       | 800                           | ns                 |

|        | Acquisition time                     |                                          | 325  |       |                               | ns                 |

|        | Maximum throughput rate              | 20-MHz SCLK                              |      |       | 1                             | MHz                |

|        | Aperture delay                       |                                          |      | 5     |                               | ns                 |

|        | Step response                        |                                          |      | 150   |                               | ns                 |

|        | Over voltage recovery                |                                          |      | 150   |                               | ns                 |

(1) Ideal input span; does not include gain or offset error.

(2) LSB means least-significant bit.

6

(3) Measured relative to an ideal full-scale input

Submit Documentation Feedback

Copyright © 2014, Texas Instruments Incorporated

#### EXAS RUMENTS

www.ti.com

#### Electrical Characteristics: ADS7950-Q1, ADS7951-Q1, ADS7952-Q1, ADS7953-Q1 (continued)

$V_{(+VA)} = 2.7 V$  to 5.25 V,  $V_{(+VBD)} = 1.7 V$  to  $V_{(+VA)}$ ,  $V_{ref} = 2.5 V \pm 0.1 V$ ,  $T_A = -40^{\circ}$ C to 125°C,  $f_{sample} = 1 MHz$  (unless otherwise noted)

|                     | PARAMETER                                   | TEST CONDITIONS                                                                                                                     | MIN                          | ТҮР          | MAX                | UNIT |

|---------------------|---------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|------------------------------|--------------|--------------------|------|

| DYNAMIC             | C CHARACTERISTICS                           |                                                                                                                                     |                              |              |                    |      |

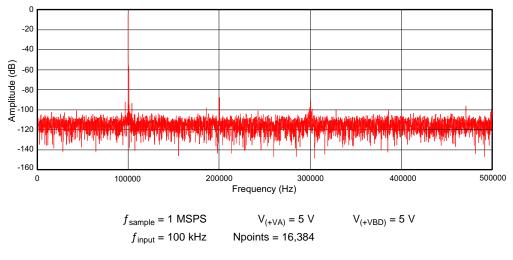

| THD                 | Total harmonic distortion <sup>(4)</sup>    | 100 kHz                                                                                                                             |                              | -82          |                    | dB   |

| SNR                 | Signal-to-noise ratio                       | 100 kHz                                                                                                                             | 70                           | 71.7         |                    | dB   |

| SINAD               | Signal-to-noise + distortion                | 100 kHz                                                                                                                             | 68                           | 71.3         |                    | dB   |

| SFDR                | Spurious-free dynamic range                 | 100 kHz                                                                                                                             |                              | 84           |                    | dB   |

|                     | Small signal bandwidth                      | At –3 dB                                                                                                                            |                              | 47           |                    | MHz  |

|                     |                                             | Any off-channel with 100 kHz. Full-scale input to channel being sampled with DC input (isolation crosstalk).                        |                              | -95          |                    | dB   |

|                     | Channel-to-channel crosstalk                | From previously sampled to channel with 100 kHz. Full-<br>scale input to channel being sampled with DC input<br>(memory crosstalk). |                              | -85          |                    | dB   |

| EXTERN              | AL REFERENCE INPUT                          |                                                                                                                                     |                              |              |                    |      |

| V <sub>ref</sub>    | Reference voltage at REFP <sup>(5)</sup>    |                                                                                                                                     | 2                            | 2.5          | 3                  | V    |

| R <sub>ref</sub>    | Reference resistance                        |                                                                                                                                     |                              | 100          |                    | kΩ   |

| ALARM S             | SETTING                                     |                                                                                                                                     |                              |              |                    |      |

|                     | Higher threshold range                      |                                                                                                                                     | 0                            |              | FFC                | Hex  |

|                     | Lower threshold range                       |                                                                                                                                     | 0                            |              | FFC                | He>  |

| DIGITAL             | INPUT/OUTPUT (CMOS Logic Family)            | •                                                                                                                                   |                              |              |                    |      |

| V <sub>IH</sub>     | High logic-level input voltage              |                                                                                                                                     | 0.7 ×<br>V <sub>(+VBD)</sub> |              |                    | V    |

| VIL                 | Low logic-level input voltage               | V <sub>(+VA)</sub> = 5 V                                                                                                            |                              |              | 0.8                | V    |

| vil                 | Low logic-level input voltage               | $V_{(+VA)} = 3 V$                                                                                                                   |                              |              | 0.4                | V    |

| V <sub>OH</sub>     | High logic-level output voltage             | At source current (I <sub>S</sub> ) = 200 $\mu$ A                                                                                   | V <sub>(+VBD)</sub> –<br>0.2 |              |                    | V    |

| V <sub>OL</sub>     | Low logic-level output voltage              | At I <sub>sink</sub> = 200 µA                                                                                                       | 0.4                          |              |                    | V    |

|                     | Data format MSB first                       |                                                                                                                                     |                              | MSB first    |                    |      |

| POWER \$            | SUPPLY REQUIREMENTS                         |                                                                                                                                     |                              |              |                    |      |

| V <sub>(+VA)</sub>  | Analog power-supply voltage                 |                                                                                                                                     | 2.7                          | 3.3          | 5.25               | V    |

| V <sub>(+VBD)</sub> | Digital I/O-supply voltage                  |                                                                                                                                     | 1.7                          | 3.3          | V <sub>(+VA)</sub> | V    |

|                     |                                             | At $V_{(+VA)} = 2.7$ V to 3.6 V and 1-MHz throughput                                                                                |                              | 1.8          |                    | mA   |

|                     | Supply surrent (normal mode)                | At $V_{(+VA)} = 2.7$ V to 3.6 V static state                                                                                        |                              | 1.05         |                    | mA   |

| I <sub>(+VA)</sub>  | Supply current (normal mode)                | At $V_{(+VA)} = 4.7$ V to 5.25 V and 1-MHz throughput                                                                               |                              | 2.3          | 3                  | mA   |

|                     |                                             | At $V_{(+VA)}$ = 4.7 V to 5.25 V static state                                                                                       |                              | 1.1          | 1.5                | mA   |

|                     | Power-down state supply current             |                                                                                                                                     |                              | 1            |                    | μA   |

| I <sub>(+VBD)</sub> | Digital I/O-supply current                  | $V_{(+VA)} = 5.25 \text{ V}, f_{\text{sample}} = 1 \text{ MHz}$                                                                     |                              | 1            |                    | mA   |

|                     | Power-up time                               |                                                                                                                                     |                              |              | 1                  | μs   |

|                     | Invalid conversions after power up or reset |                                                                                                                                     |                              |              | 1                  | cycl |

|                     | Latch-up                                    |                                                                                                                                     | JE                           | SD78 class I |                    |      |

| TEMPER              | ATURE RANGE                                 |                                                                                                                                     |                              |              |                    |      |

|                     | Specified performance                       |                                                                                                                                     | -40                          |              | 125                | °C   |

(4)

Calculated on the first nine harmonics of the input frequency. The device is designed to operate over  $V_{ref} = 2 V$  to 3 V. However, lower noise performance can be expected at  $V_{ref} < 2.4 V$ , because of (5) SNR degradation resulting from lowered signal range.

Copyright © 2014, Texas Instruments Incorporated

7

#### 7.6 Electrical Characteristics: ADS7954-Q1, ADS7956-Q1, ADS7957-Q1

$V_{(+VA)} = 2.7 \text{ V}$  to 5.25 V,  $V_{(+VBD)} = 1.7 \text{ V}$  to  $V_{(+VA)}$ ,  $V_{ref} = 2.5 \text{ V} \pm 0.1 \text{ V}$ ,  $T_A = -40^{\circ}\text{C}$  to 125°C,  $f_{sample} = 1 \text{ MHz}$  (unless otherwise noted)

|                  | PARAMETER                                | TEST CONDITIONS                                                                                               | MIN                          | TYP       | MAX                       | UNIT               |

|------------------|------------------------------------------|---------------------------------------------------------------------------------------------------------------|------------------------------|-----------|---------------------------|--------------------|

| ANALOG           | S INPUT                                  |                                                                                                               |                              |           |                           |                    |

|                  | Full-scale input span <sup>(1)</sup>     | Range 1                                                                                                       | 0                            |           | V <sub>ref</sub>          | V                  |

|                  | Full-scale input span ??                 | Range 2 while $2 \times V_{ref} \le +VA$                                                                      | 0                            |           | $2 \times V_{ref}$        | V                  |

|                  |                                          | Range 1                                                                                                       | -0.2                         |           | V <sub>ref</sub> + 0.2    | V                  |

|                  | Absolute input range                     | Range 2 while $2 \times V_{ref} \le +VA$                                                                      | -0.2                         |           | 2 × V <sub>ref</sub> +0.2 | V                  |

|                  | Input capacitance                        |                                                                                                               |                              | 15        |                           | ρF                 |

|                  | Input leakage current                    | T <sub>A</sub> = 125°C                                                                                        |                              | 61        |                           | nA                 |

| SYSTEM           | PERFORMANCE                              |                                                                                                               |                              |           | 1                         |                    |

|                  | Resolution                               |                                                                                                               |                              | 10        |                           | Bits               |

|                  | No missing codes                         |                                                                                                               | 10                           |           |                           | Bits               |

|                  | Integral linearity                       |                                                                                                               | -0.5                         | ±0.2      | 0.5                       | LSB <sup>(2)</sup> |

|                  | Differential linearity                   |                                                                                                               | -0.5                         | ±0.2      | 0.5                       | LSB                |

|                  | Offset error <sup>(3)</sup>              |                                                                                                               | -1.5                         | ±0.5      | 1.5                       | LSB                |

|                  |                                          | Range 1                                                                                                       | -1                           | ±0.1      | 1                         | LSB                |

|                  | Gain error                               | Range 2                                                                                                       |                              | ±0.1      |                           | LSB                |

| SAMPLIN          | NG DYNAMICS                              |                                                                                                               |                              |           |                           |                    |

|                  | Conversion time                          | 20-MHz SCLK                                                                                                   |                              |           | 800                       | ns                 |

|                  | Acquisition time                         |                                                                                                               | 325                          |           |                           | ns                 |

|                  | Maximum throughput rate                  | 20-MHz SCLK                                                                                                   |                              |           | 1                         | MHz                |

|                  | Aperture delay                           |                                                                                                               |                              | 5         |                           | ns                 |

|                  | Step response                            |                                                                                                               |                              | 150       |                           | ns                 |

|                  | Over voltage recovery                    |                                                                                                               |                              | 150       |                           | ns                 |

|                  | C CHARACTERISTICS                        |                                                                                                               |                              |           |                           |                    |

| THD              | Total harmonic distortion <sup>(4)</sup> | 100 kHz                                                                                                       |                              | -80       |                           | dB                 |

| SNR              | Signal-to-noise ratio                    | 100 kHz                                                                                                       | 60                           | 00        |                           | dB                 |

| SINAD            | Signal-to-noise + distortion             | 100 kHz                                                                                                       | 60                           |           |                           | dB                 |

| SFDR             | Spurious-free dynamic range              | 100 kHz                                                                                                       | 00                           | 82        |                           | dB                 |

| SI DI            |                                          | At -3 dB                                                                                                      |                              | 47        |                           | MHz                |

|                  | Full-power bandwidth                     |                                                                                                               |                              | 47        |                           | IVITIZ             |

|                  |                                          | Any off-channel with 100 kHz. Full-scale input to channel being sampled with dc input.                        |                              | -95       |                           | dB                 |

|                  | Channel-to-channel crosstalk             | From previously sampled to channel with 100 kHz. Full-<br>scale input to channel being sampled with dc input. |                              | -85       |                           | dB                 |

| EXTERN           | AL REFERENCE INPUT                       |                                                                                                               |                              |           | 1                         |                    |

| V <sub>ref</sub> | Reference voltage at REFP                |                                                                                                               | 2                            | 2.5       | 3                         | V                  |

| R <sub>ref</sub> | Reference resistance                     |                                                                                                               |                              | 100       |                           | kΩ                 |

| ALARM S          | SETTING                                  |                                                                                                               |                              |           | I                         |                    |

|                  | Higher threshold range                   |                                                                                                               | 000                          |           | FFC                       | Hex                |

|                  | Lower threshold range                    |                                                                                                               | 000                          |           | FFC                       | Hex                |

| DIGITAL          | INPUT/OUTPUT (CMOS Logic Famil           | y)                                                                                                            | 1                            |           | -                         |                    |

| V <sub>IH</sub>  | High logic-level input voltage           |                                                                                                               | 0.7 ×<br>V <sub>(+VBD)</sub> |           |                           | V                  |

|                  |                                          | V <sub>(+VBD)</sub> = 5 V                                                                                     | ,,                           |           | 0.8                       | V                  |

| V <sub>IL</sub>  | Low logic-level input voltage            | $V_{(+VBD)} = 3 V$                                                                                            |                              |           | 0.4                       | V                  |

| V <sub>OH</sub>  |                                          | At source current ( $I_S$ ) = 200 µA                                                                          | V <sub>(+VBD)</sub> -        |           |                           |                    |

| - OH             | High logic-level output voltage          |                                                                                                               | 0.2                          |           |                           | V                  |

| V <sub>OL</sub>  | Low logic-level output voltage           | At I <sub>sink</sub> = 200 μA                                                                                 | 0.4                          |           |                           | V                  |

|                  | Data format MSB first                    |                                                                                                               |                              | MSB first |                           |                    |

(1) Ideal input span; does not include gain or offset error.

(2) LSB means least significant bit.

(3) Measured relative to an ideal full-scale input

(4) Calculated on the first nine harmonics of the input frequency.

8 Submit Documentation Feedback

Copyright © 2014, Texas Instruments Incorporated

#### Electrical Characteristics: ADS7954-Q1, ADS7956-Q1, ADS7957-Q1 (continued)

$V_{(+VA)} = 2.7$  V to 5.25 V,  $V_{(+VBD)} = 1.7$  V to  $V_{(+VA)}$ ,  $V_{ref} = 2.5$  V ± 0.1 V,  $T_A = -40^{\circ}$ C to 125°C,  $f_{sample} = 1$  MHz (unless otherwise noted)

|                     | PARAMETER                                   | TEST CONDITIONS                                                 | MIN | TYP          | MAX                | UNIT  |

|---------------------|---------------------------------------------|-----------------------------------------------------------------|-----|--------------|--------------------|-------|

| POWER               | SUPPLY REQUIREMENTS                         |                                                                 |     |              |                    |       |

| V <sub>(+VA)</sub>  | Analog power-supply voltage                 |                                                                 | 2.7 | 3.3          | 5.25               | V     |

| V <sub>(+VBD)</sub> | Digital I/O-supply voltage                  |                                                                 | 1.7 | 3.3          | V <sub>(+VA)</sub> | V     |

|                     |                                             | At $V_{(+VA)} = 2.7$ V to 3.6 V and 1-MHz throughput            |     | 1.8          |                    | mA    |

| I <sub>(+VA)</sub>  |                                             | At $V_{(+VA)} = 2.7$ V to 3.6 V static state                    |     | 1.05         | 1                  | mA    |

|                     | Supply current (normal mode)                | At $V_{(+VA)}$ = 4.7 V to 5.25 V and 1-MHz throughput           |     | 2.3          | 3                  | mA    |

|                     |                                             | At $V_{(+VA)} = 4.7$ V to 5.25 V static state                   |     | 1.1          | 1.5                | mA    |

|                     | Power-down state supply current             |                                                                 |     | 1            |                    | μA    |

| I <sub>(+VBD)</sub> | Digital I/O-supply current                  | V <sub>(+VA)</sub> = 5.25 V, <i>f</i> <sub>sample</sub> = 1 MHz |     | 1            |                    | mA    |

|                     | Power-up time                               |                                                                 |     |              | 1                  | μs    |

|                     | Invalid conversions after power up or reset |                                                                 |     |              | 1                  | cycle |

|                     | Latch-up                                    |                                                                 | JE  | SD78 class I |                    |       |

| TEMPER              | ATURE RANGE                                 | ·                                                               |     |              |                    |       |

|                     | Specified performance                       |                                                                 | -40 |              | 125                | °C    |

#### 7.7 Electrical Characteristics: ADS7958-Q1, ADS7959-Q1, ADS7960-Q1, ADS7961-Q1

$V_{(+VA)} = 2.7$  V to 5.25 V,  $V_{(+VBD)} = 1.7$  V to  $V_{(+VA)}$ ,  $V_{ref} = 2.5$  V ± 0.1 V,  $T_A = -40$ °C to 125°C,  $f_{sample} = 1$  MHz (unless otherwise noted)

| PARAMETER                                       | TEST CONDITIONS                          | MIN   | TYP  | MAX                           | UNIT               |

|-------------------------------------------------|------------------------------------------|-------|------|-------------------------------|--------------------|

| ANALOG INPUT                                    |                                          |       |      |                               |                    |

| <b>F</b> ull <b> :  : - : : : : : : : : : :</b> | Range 1                                  | 0     |      | V <sub>ref</sub>              | V                  |

| Full-scale input span <sup>(1)</sup>            | Range 2 while 2 × V <sub>ref</sub> ≤ +VA | 0     |      | $2 \times V_{ref}$            | V                  |

| Absolute input range                            | Range 1                                  | -0.20 |      | V <sub>ref</sub> + 0.2        | V                  |

| Absolute input range                            | Range 2 while 2 × $V_{ref} \le +VA$      | -0.20 |      | 2 × V <sub>ref</sub><br>+ 0.2 | V                  |

| Input capacitance                               |                                          |       | 15   |                               | ρF                 |

| Input leakage current                           | $T_A = 125^{\circ}C$                     |       | 61   |                               | nA                 |

| SYSTEM PERFORMANCE                              |                                          |       |      |                               |                    |

| Resolution                                      |                                          |       | 8    |                               | Bits               |

| No missing codes                                |                                          | 8     |      |                               | Bits               |

| Integral linearity                              |                                          | -0.3  | ±0.1 | 0.3                           | LSB <sup>(2)</sup> |

| Differential linearity                          |                                          | -0.3  | ±0.1 | 0.3                           | LSB                |

| Offset error <sup>(3)</sup>                     |                                          | -0.5  | ±0.2 | 0.5                           | LSB                |

|                                                 | Range 1                                  | -0.6  | ±0.1 | 0.6                           | LSB                |

| Gain error                                      | Range 2                                  |       | ±0.1 |                               | LSB                |

| SAMPLING DYNAMICS                               |                                          |       |      |                               |                    |

| Conversion time                                 | 20-MHz SCLK                              |       |      | 800                           | ns                 |

| Acquisition time                                |                                          | 325   |      |                               | ns                 |

| Maximum throughput rate                         | 20-MHz SCLK                              |       |      | 1                             | MHz                |

| Aperture delay                                  |                                          |       | 5    |                               | ns                 |

| Step response                                   |                                          |       | 150  |                               | ns                 |

| Over voltage recovery                           |                                          |       | 150  |                               | ns                 |

(1) Ideal input span; does not include gain or offset error.

(2) LSB means least significant bit.

(3) Measured relative to an ideal full-scale input

Copyright © 2014, Texas Instruments Incorporated

<sup>9</sup>

#### Electrical Characteristics: ADS7958-Q1, ADS7959-Q1, ADS7960-Q1, ADS7961-Q1 (continued)

$V_{(+VA)} = 2.7$  V to 5.25 V,  $V_{(+VBD)} = 1.7$  V to  $V_{(+VA)}$ ,  $V_{ref} = 2.5$  V ± 0.1 V,  $T_A = -40^{\circ}$ C to 125°C,  $f_{sample} = 1$  MHz (unless otherwise noted)

|                     | PARAMETER                                   | TEST CONDITIONS                                                                                           | MIN                          | TYP      | MAX                | UNIT  |

|---------------------|---------------------------------------------|-----------------------------------------------------------------------------------------------------------|------------------------------|----------|--------------------|-------|

| DYNAMI              | C CHARACTERISTICS                           |                                                                                                           |                              |          |                    |       |

| THD                 | Total harmonic distortion <sup>(4)</sup>    | 100 kHz                                                                                                   |                              | -75      |                    | dB    |

| SNR                 | Signal-to-noise ratio                       | 100 kHz                                                                                                   | 49                           |          |                    | dB    |

| SINAD               | Signal-to-noise + distortion                | 100 kHz                                                                                                   | 49                           |          |                    | dB    |

| SFDR                | Spurious-free dynamic range                 | 100 kHz                                                                                                   |                              | -78      |                    | dB    |

|                     | Full-power bandwidth                        | At –3 dB                                                                                                  |                              | 47       |                    | MHz   |

|                     | Channel-to-channel crosstalk                | Any off-channel with 100 kHz. Full-scale input to channel being<br>sampled with dc input.                 |                              | -95      |                    | dB    |

|                     | Channel-10-channel Crossiaik                | From previously sampled to channel with 100 kHz. Full-scale input to channel being sampled with dc input. |                              | -85      |                    | dB    |

| EXTERN              | IAL REFERENCE INPUT                         |                                                                                                           |                              |          |                    |       |

| Vref                | reference voltage at REFP                   |                                                                                                           | 2                            | 2.5      | 3                  | V     |

|                     | Reference resistance                        |                                                                                                           |                              | 100      |                    | kΩ    |

| ALARM               | SETTING                                     |                                                                                                           |                              |          |                    |       |

|                     | Higher threshold range                      |                                                                                                           | 000                          |          | FF                 | Hex   |

|                     | Lower threshold range                       |                                                                                                           | 000                          |          | FF                 | Hex   |

| DIGITAL             | . INPUT/OUTPUT (CMOS Logic Family)          |                                                                                                           |                              |          |                    |       |

| V <sub>IH</sub>     | High logic-level input voltage              |                                                                                                           | 0.7 ×<br>V <sub>(+VBD)</sub> |          |                    | V     |

| N/                  |                                             | V <sub>(+VBD)</sub> = 5 V                                                                                 |                              |          | 0.8                | V     |

| V <sub>IL</sub>     | Low logic-level input voltage               | V <sub>(+VBD)</sub> = 3 V                                                                                 |                              |          | 0.4                | V     |

| V <sub>OH</sub>     | High logic-level output voltage             | At source current (I <sub>S</sub> ) = 200 $\mu$ A                                                         | V <sub>(+VBD)</sub> -<br>0.2 |          |                    | V     |

| V <sub>OL</sub>     | Low logic-level output voltage              | At I <sub>sink</sub> = 200 μA                                                                             | 0.4                          |          |                    | V     |

|                     | Data format                                 |                                                                                                           | MS                           | SB first |                    |       |

| POWER               | SUPPLY REQUIREMENTS                         |                                                                                                           |                              |          |                    |       |

| V <sub>(+VA)</sub>  | Analog power-supply voltage                 |                                                                                                           | 2.7                          | 3.3      | 5.25               | V     |

| V <sub>(+VBD)</sub> | Digital I/O-supply voltage                  |                                                                                                           | 1.7                          | 3.3      | V <sub>(+VA)</sub> | V     |

|                     |                                             | At $V_{(+VA)} = 2.7$ V to 3.6 V and 1-MHz throughput                                                      |                              | 1.8      |                    | mA    |

|                     | Supply surrent (normal mode)                | At $V_{(+VA)} = 2.7$ V to 3.6 V static state                                                              |                              | 1.05     |                    | mA    |

| I <sub>(+VA)</sub>  | Supply current (normal mode)                | At $V_{(+VA)} = 4.7$ V to 5.25 V and 1-MHz throughput                                                     |                              | 2.3      | 3                  | mA    |

|                     |                                             | At $V_{(+VA)} = 4.7$ V to 5.25 V static state                                                             |                              | 1.1      | 1.5                | mA    |

|                     | Power-down state supply current             |                                                                                                           |                              | 1        |                    | μA    |

| I <sub>(+VBD)</sub> | Digital I/O-supply current                  | $V_{(+VA)} = 5.25 \text{ V}, f_{\text{sample}} = 1 \text{ MHz}$                                           |                              | 1        |                    | mA    |

|                     | Power-up time                               |                                                                                                           |                              |          | 1                  | μs    |

|                     | Invalid conversions after power up or reset |                                                                                                           |                              |          | 1                  | cycle |

|                     | Latch-up                                    |                                                                                                           | JESD                         | 78 class | 1                  |       |

| TEMPER              | ATURE RANGE                                 |                                                                                                           |                              |          |                    |       |

|                     | Specified performance                       |                                                                                                           | -40                          |          | 125                | °C    |

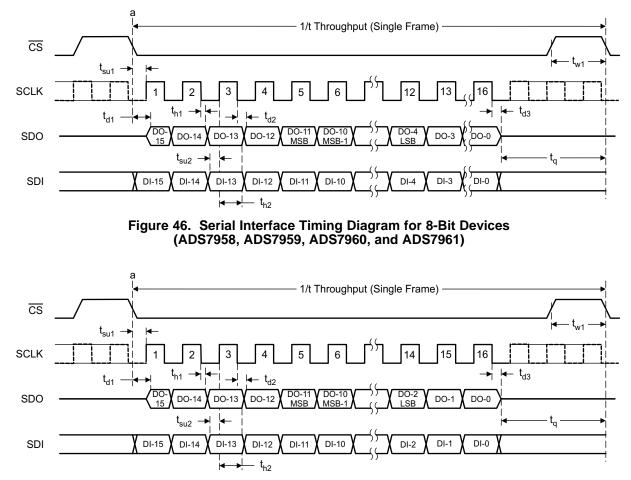

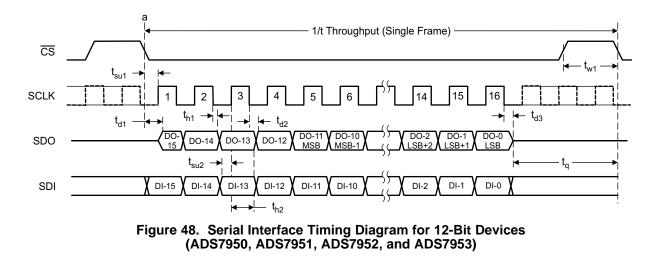

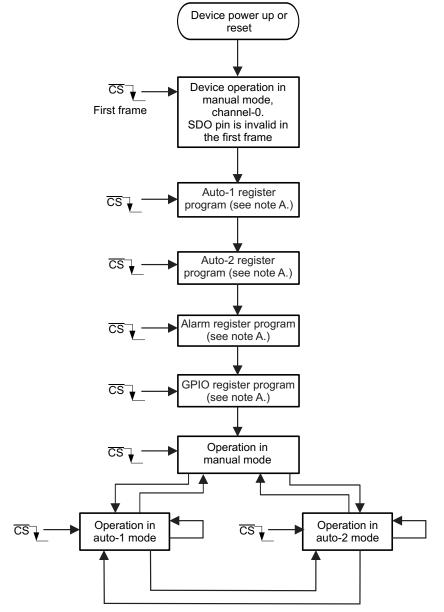

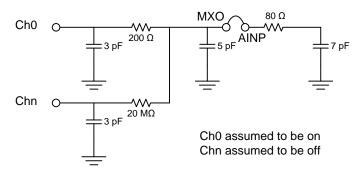

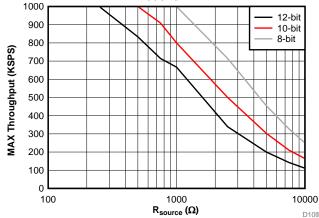

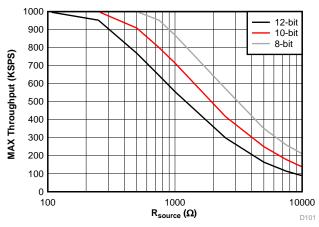

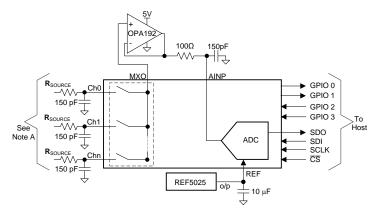

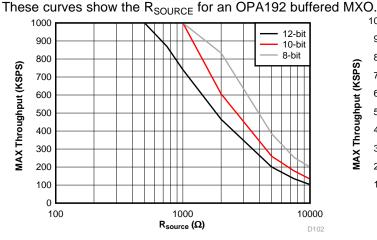

(4) Calculated on the first nine harmonics of the input frequency.