# Octal low-side driver for bulb, resistive and inductive loads with serial input control, output protection and diagnostic

Datasheet - production data

#### **Features**

- Outputs current capability up to 0.5 A

- · Cascadable SPI control for outputs

- Reset function with reset signal or undervoltage at V<sub>DD</sub>

- Programmable intrinsic output voltage clamping at typ. 50 V for inductive switching

- Overcurrent shutdown with latch-off for every write cycle (SFPD = low)

- Independent thermal shutdown of outputs (SOA Protection)

- Output status data available on the SPI using 8-bit I/O protocol up to 3.0 MHz

- Low standby current with reset = low (typ. 35 μA @ VDD)

- Open load detection (outputs off)

- Single V<sub>DD</sub> logic supply

- High EMS immunity and low EME (controlled output slopes)

- Full functionality of the remaining device at negative voltage drop on outputs (-1.5 V or -3.0 A)

- Output mode programmable for sustained current limit or shutdown

## **Description**

L9823 is a octal low-side driver circuit, dedicated for automotive applications.

Output voltage clamping is provided for flyback current recirculation, when inductive loads are driven.

Chip select and cascadable serial 8-bit Interface for outputs control and diagnostic data transfer.

**Table 1. Device summary**

| Order code | Package | Packing |

|------------|---------|---------|

| L9823      | SO24    | Tube    |

| E-L9823    | SO24    | Tube    |

Contents L9823

## **Contents**

| 1 | Bloc | Block diagram and pins description 5                                                                |    |  |

|---|------|-----------------------------------------------------------------------------------------------------|----|--|

|   | 1.1  | Block diagram                                                                                       | 5  |  |

|   | 1.2  | Pins description                                                                                    | 5  |  |

| 2 | Elec | trical specifications                                                                               | 8  |  |

|   | 2.1  | Absolute maximum ratings                                                                            | 8  |  |

|   | 2.2  | Thermal data                                                                                        | 8  |  |

|   | 2.3  | Electrical characteristics                                                                          | 9  |  |

|   | 2.4  | Power outputs characteristics for flyback current, outputs short circuit protection and diagnostics | 2  |  |

| 3 | Fun  | ctional description1                                                                                | 3  |  |

|   | 3.1  | General                                                                                             | 13 |  |

|   | 3.2  | Output stages control                                                                               | 13 |  |

|   | 3.3  | Diagnostics                                                                                         | 4  |  |

| 4 | Арр  | lications information1                                                                              | 6  |  |

| 5 | Pacl | kage information                                                                                    | 7  |  |

| 6 | Revi | ision history                                                                                       | 8  |  |

DocID7791 Rev 7

L9823 List of tables

# List of tables

| Table 1. | Device summary             | 1 |

|----------|----------------------------|---|

| Table 2. | Pins description           | 6 |

| Table 3. | Absolute maximum ratings   | 8 |

|          | Thermal data               | 8 |

| Table 5. | Electrical characteristics | 9 |

| Table 6. | Outputs Control            | 1 |

| Table 7. | Diagnostic for outputs     | 4 |

| Table 8. | Document revision history  | 8 |

List of figures L9823

# List of figures

| Figure 1. | Block diagram                                             | . 5 |

|-----------|-----------------------------------------------------------|-----|

| Figure 2. | Pins connection (top view)                                |     |

| Figure 3. | Output control register structure                         |     |

| Figure 4. | Timing of the serial interface                            |     |

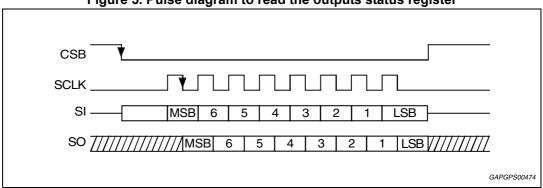

| Figure 5. | Pulse diagram to read the outputs status register         | 14  |

| Figure 6. | Structure of the outputs status register                  | 15  |

| Figure 7. | Typical application circuit diagram for the L9823 circuit | 16  |

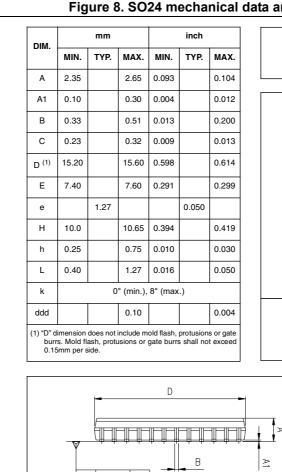

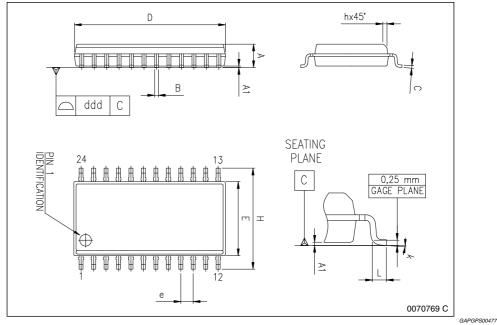

| Figure 8. | SO24 mechanical data and package dimensions               | 17  |

#### Block diagram and pins description 1

#### 1.1 **Block diagram**

Figure 1. Block diagram SFPD OUT0 OL0 PloL Gate Interface Q0 Output Latch Q0 Q1 Q2 Q3 Q4 Q4 Q5 Q6 Q6 Control SPI I<sub>SCB</sub>0 Over Temperature OT0 Detect √— Diag0 CH0 Shift Register Diag0 OUT1 Q1 Diag1 CH1 Diag1 23 Diag2 OUT2 Diag3 CH2 Diag2 Diag4 OUT3 Diag5 СНЗ Diag6 Diag3 13 Diag7 OUT4 Ω4 CH4 Diag4 OUT5 Q5 CH5 Diag5 OUT6 Q6 Reset CH7 Reset Diag6 OUT7 Q7 CH7 Diag7 Undervoltage RESET GND 5-8 GAPGPS00470

1.2 **Pins description**

OUT7 D OUTO 24 OUT1 OUT6 2 23 SCLK  $\square$ RESET 3 22 SI  $\square$ N.C. 4 21 **GND** GND 20 19 **GND** GND 18 **GND** GND □ 8 17 **GND** SO 16 VDD **CSB** 10 15 **SFPD** OUT2 OUT5 [T 11 14 D OUT3 OUT4  $\square$ 12 13 GAPGPS00471

Figure 2. Pins connection (top view)

Table 2. Pins description

| N# | Pin  | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|----|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1  | OUT7 | Output 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 2  | OUT6 | Output 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 3  | SCLK | The system clock pin (SCLK) clocks the internal shift registers of the L9823. The serial input pin (SI) accepts data into the input shift register on the falling edge of the SCLK signal while the serial output pin (SO) shifts data information out of the shift register on the rising edge of the SCLK signal. False clocking of the shift register must be avoided to guarantee validity of data. It is essential that the SCLK pin be in a logic low state whenever chip select bar pin (CSB) makes any transition. For this reason, it is recommended though not necessary, that the SCLK pin be kept in a low logic state as long as the device is not accessed (CSB in logic high state). When CSB is in a logic high state, any signal at the SCLK and SI pin is ignored and SO is tri-stated (high-impedance).                                                                                                                                                                                                                                     |

| 4  | SI   | This pin is for the input of serial instruction data. SI information is read in on the falling edge of SCLK. A logic high state present on this pin when the SCLK signal rises will program a specific output OFF, and in turn, turns OFF the specific output on the rising edge of the CSB signal. Conversely, a logic low state present on the SI pin will program the output ON, and in turn, turns ON the specific output on the rising edge of the CSB signal. To program the eight outputs of the L9823 ON or OFF, an eight bit serial stream of data is required to be entered into the SI pin starting with Output 7, followed by Output 6, Output 5, etc., to Output 0. For each rise of the SCLK signal, with CSB held in a logic low state, a databyte instruction (ON or OFF) is loaded into the shift register per the databyte SI state. The shift register is full after eight bits of information have been entered. To preserve data integrity, care should be taken to not transition SI as SCLK transitions from a low-to-high logic state. |

| 5  | GND  | GND                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 6  | GND  | GND                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 7  | GND  | GND                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 8  | GND  | GND                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 9  | SO   | The serial output (SO) pin is the tri-stateable output from the shift register. The SO pin remains in a high impedance state until the CSB pin goes to a logic low state. The SO data reports the drain status, either high or low. The SO pin changes state on the rising edge of SCLK and reads out on the falling edge of SCLK. When an output is OFF and not faulted, the corresponding SO databyte is a high state. When SO an output is ON, and there is no fault, the corresponding databyte on the SO pin will be a low logic state. The SI / SO shifting of data follows a first-in-first-out protocol with both input and output words transferring the Most Significant Bit (MSB) first. The SO pin is not affected by the status of the Reset pin.                                                                                                                                                                                                                                                                                                 |

| 10 | CSB  | The system MCU selects the L9823 to be communicated with through the use of the CSB pin. Whenever the pin is in a logic low state, data can be transferred from the MCU to the L9823 and vise versa. Clocked-in data from the MCU is transferred from the L9823 shift register and latched into the power outputs on the rising edge of the CSB signal. On the falling edge of the CSB signal, drain status information is transferred from the power outputs and loaded into the device's shift register. The CSB pin also controls the output driver of the serial output pin. Whenever the CSB pin goes to a logic low state, the SO pin output driver is enabled allowing information to be transferred from the L9823 to the MCU. To avoid any spurious data, it is essential that the high-to-low transition of the CSB signal occur only when SCLK is in a logic low state.                                                                                                                                                                             |

| 11 | OUT5 | Output 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 12 | OUT4 | Output 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 13 | OUT3 | Output 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

Table 2. Pins description (continued)

| N# | Pin   | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |

|----|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 14 | OUT2  | Output 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |

| 15 | SFPD  | The Short Fault Protect Disable (SFPD) pin is used to disable the overcurrent latch-OFF. This feature allows control of incandescent loads where in-rush currents exceed the device's analog current limits. Essentially the SFPD pin determines whether the L9823 output(s) will instantly shutdown upon sensing an output short or remain ON in a current limiting mode of operation until the output short is removed or thermal shutdown is reached. If the SFPD pin is tied to $V_{\rm DD}$ the L9823 output(s) will remain ON in a current limited mode of operation upon encountering a load short to supply. If the SFPD pin is grounded, a short circuit will immediately shutdown only the output affected. Other outputs not having a fault condition will operate normally.                                                       |  |  |

| 16 | VDD   | VDD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |

| 17 | GND   | GND                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |

| 18 | GND   | GND                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |

| 19 | GND   | GND                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |

| 20 | GND   | GND                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |

| 21 | N.C.  | Not Connected                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |

| 22 | RESET | The Reset pin is active low and used to clear the SPI shift register and in doing so sets all output switches OFF. With the device in a system with an MCU; upon initial system power up, the MCU holds the Reset pin of the device in a logic low state ensuring all outputs to be OFF until the VDD pin voltages are adequate for predictable operation. After the L9823 is Reset, the MCU is ready to assert system control with all output switches initially OFF. The Reset pin is active low and has an internal pull-down incorporated to ensure operational predictability should the external pull-down of the MCU open circuit. The internal pull-up is to afford safe and easy interfacing to the MCU. The Reset pin of the L9823 should be pulled to a logic low state for a duration of at least 160ns to ensure reliable Reset. |  |  |

| 23 | OUT1  | Output 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |

| 24 | OUT0  | Output 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |

## 2 Electrical specifications

## 2.1 Absolute maximum ratings

For voltages and currents applied externally to the device. Exceeding limits may cause damage to the device.

Table 3. Absolute maximum ratings

| Symbol                | Parameter                                              | Value                        | Unit |  |  |  |

|-----------------------|--------------------------------------------------------|------------------------------|------|--|--|--|

| $V_{DD}$              | Supply voltage                                         | -0.3 to 7                    | V    |  |  |  |

| Inputs and            | Inputs and data lines (CSB, SCLK, SI, Reset, SFPD, SO) |                              |      |  |  |  |

| V <sub>IN</sub>       | Voltage (CSB, SCLK, SI, Reset, SFPD)                   | -0.3 to 7                    |      |  |  |  |

| V <sub>SDO</sub>      | Voltage (SO)                                           | -0.3 to V <sub>DD</sub> +0.3 | V    |  |  |  |

| I <sub>IN</sub>       | Protection diodes current <sup>(1)</sup> T ≤ 1ms       | -20 to 20 <sup>(1)</sup>     | mA   |  |  |  |

| Outputs (0            | OUT0 to OUT7)                                          |                              |      |  |  |  |

| V <sub>OUT Cont</sub> | Continuous output voltage                              | -1.5 to 45                   | V    |  |  |  |

| V <sub>OUT Cont</sub> | Continuous output current                              | -3 to I <sub>OUT LIM</sub>   | Α    |  |  |  |

| I <sub>OUT PEAK</sub> | Output current                                         | -10 <sup>(2)</sup> to 2      | Α    |  |  |  |

| E <sub>OUTclamp</sub> | Output clamp energy <sup>(3)</sup>                     | 50                           | mJ   |  |  |  |

| I <sub>OUT LIM</sub>  | Output current (self limit)                            | 2                            | Α    |  |  |  |

<sup>1.</sup> All inputs are protected against ESD according to MIL 883C; tested with HBM C = 100 pF, R = 1500  $\Omega$  at  $\pm 2$ kV. It corresponds to a dissipated energy E  $\leq$  0.2mJ (data available upon request).

#### 2.2 Thermal data

Table 4. Thermal data

| Symbol                | Parameter                                                   | Value                  | Unit |  |  |  |

|-----------------------|-------------------------------------------------------------|------------------------|------|--|--|--|

| Thermal s             | Thermal shutdown                                            |                        |      |  |  |  |

| T <sub>LIM</sub>      | Thermal shutdown threshold                                  | 155 (Min.), 180 (Typ.) | °C   |  |  |  |

| Thermal re            | Thermal resistance (junction-to-lead)                       |                        |      |  |  |  |

| R <sub>thjL-one</sub> | Single output (junction lead)                               | 25 (Max.)              | °C/W |  |  |  |

| R <sub>thjL-all</sub> | R <sub>thjL-all</sub> All outputs (junction lead) 20 (Max.) |                        | °C/W |  |  |  |

| T <sub>stg</sub>      | Storage temperature                                         | -55 to 150             | °C   |  |  |  |

<sup>2.</sup> Transient pulses in accordance to DIN40839 part 1, 3 and ISO 7637 Part 1, 3.

<sup>3.</sup> Max. output clamp energy at  $T_j$  = 150°C, using single non-repetitive pulse of 500 mA

## 2.3 Electrical characteristics

4.5 V  $\leq$  V  $_{DD} \leq$  5.5 V; -40  $^{\circ}C \leq$  T  $_{J} \leq$  150  $^{\circ}C;$  unless otherwise specified.

**Table 5. Electrical characteristics**

|                                           | Parameter                                                             | Test condition                                                                                                                                       | Min.                 | Тур.     | Max.                | Unit |

|-------------------------------------------|-----------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|----------|---------------------|------|

| Supply voltage                            |                                                                       |                                                                                                                                                      |                      |          |                     |      |

| I <sub>DDSTB</sub><br>I <sub>DDleak</sub> | Standby current leakage current                                       | Reset = LOW and / or $V_{DDRES} > V_{DD} > 0.5V$ $V_{DD} < 0.5V$                                                                                     | -                    | 35<br><1 | 70<br>10            | μA   |

| I <sub>DDOPM</sub>                        | Operating mode                                                        | I <sub>OUT0 to 7</sub> = 500 mA<br>SPI - SCLK = 3 MHz<br>CSB = Low<br>SO no load                                                                     | -                    | -        | 6                   | mA   |

| Δl <sub>DD rev</sub>                      | $\Delta I_{DD}$ during reverse output current                         | I <sub>out rev</sub> = -2.5 A                                                                                                                        | -                    | -        | 10                  | mA   |

| V <sub>DD RES</sub>                       | Undervoltage reset                                                    | Reset of all registers and disable of all outputs                                                                                                    | 2.5                  | -        | 3.95                | V    |

| Inputs (C                                 | SB, SCLK, SI, Reset, SFPD)                                            |                                                                                                                                                      |                      |          |                     |      |

| V <sub>INL</sub>                          | Low level                                                             | -                                                                                                                                                    | -0.3                 | -        | 0.2·V <sub>DD</sub> | V    |

| V <sub>INH</sub>                          | High level                                                            | -                                                                                                                                                    | 0.7·V <sub>DD</sub>  | -        | V <sub>DD</sub> +0. | V    |

| V <sub>hyst</sub>                         | Hysteresis voltage                                                    | -                                                                                                                                                    | 0.5                  | 1.2      | 0.5·V <sub>DD</sub> | V    |

| I <sub>IN</sub>                           | Input current                                                         | $V_{IN} = V_{DD}$                                                                                                                                    | -10                  | -        | 10                  | μA   |

| R <sub>IN</sub>                           | Pull-up resistance (CSB, SI) Pull-down resistance (SFPD, Reset, SCLK) | -                                                                                                                                                    | 50                   | -        | 250                 | kΩ   |

| C <sub>IN</sub>                           | Input capacitance                                                     | -                                                                                                                                                    | -                    | -        | 10                  | pF   |

| Serial dat                                | a outputs                                                             |                                                                                                                                                      |                      |          |                     |      |

| V <sub>SOH</sub>                          | High output level                                                     | I <sub>SO</sub> = -4 mA                                                                                                                              | V <sub>DD</sub> -0.4 | -        |                     | V    |

| V <sub>SOL</sub>                          | Low output level                                                      | I <sub>SO</sub> = 3.2 mA                                                                                                                             | -                    | -        | 0.4                 | V    |

| I <sub>SOL</sub>                          | Tristate leakage current                                              | CSB = high; $0 \text{ V} \le \text{V}_{SO} \le \text{V}_{DD}$                                                                                        | -10                  | -        | 10                  | μΑ   |

| $C_{SO}$                                  | Output capacitance                                                    | $f_{SO}$ = 300 kHz, 0 V $\leq$ V <sub>SO</sub> $\leq$ V <sub>DD</sub>                                                                                | -                    | -        | 20                  | pF   |

| Outputs OUT 0 to 7                        |                                                                       |                                                                                                                                                      |                      |          |                     |      |

| I <sub>OUTL0 - 7</sub>                    | Leakage current                                                       | OUTx = OFF; $V_{OUTx}$ = 16V; $V_{DD} \le V_{DD RES}$ and / or Reset = Low Tj $\le 85^{\circ}$ C                                                     | -10                  | <1μA     | 10                  | μΑ   |

| V <sub>OUT</sub><br>clamp                 | Output clamp voltage                                                  | $\begin{aligned} &2\text{mA} \leq I_{\text{OUT clamp}} \leq I_{\text{OUT LIM}} \\ &I_{\text{OUT test}} = 20\text{mA with correlation} \end{aligned}$ | 45                   | -        | 60                  | V    |

| R <sub>DSon</sub>                         | On resistance OUT 0 7                                                 | $I_{OUT} = 500 \text{mA}; T_j = +150^{\circ}\text{C}$<br>$T_j = +25^{\circ}\text{C}$                                                                 | -                    | 1<br>0.8 | 1.5<br>1.25         | Ω    |

Table 5. Electrical characteristics (continued)

| Symbol                | Parameter                                     | Test condition                                                                                                 | Min.                | Тур.                 | Max.                | Unit |

|-----------------------|-----------------------------------------------|----------------------------------------------------------------------------------------------------------------|---------------------|----------------------|---------------------|------|

| C <sub>OUT</sub>      | Output capacitance                            | V <sub>OUT</sub> = 16 V; f = 1 MHz                                                                             | -                   | -                    | 300                 | pF   |

| Outputs               | short circuit protection                      |                                                                                                                |                     |                      |                     |      |

| I <sub>SCB</sub>      | Overcurrent shutoff threshold                 | SFPD = Low, $V_{OUT} \ge V_{DG}$                                                                               | 0.5                 | 1.6                  | 2.5                 | Α    |

| I <sub>OUT LIM</sub>  | Short circuit current limitation              | -                                                                                                              | 0.5                 | 1.6                  | 2.5                 | Α    |

| t <sub>dly SCB</sub>  | Short circuit shutdown delay                  | SFPD = Low, $V_{OUT} \ge V_{DG}$<br>CSB = 50% to<br>$I_{OUT} \le 1/2 I_{OUT LIM}$                              | 70                  | 150                  | 250                 | μs   |

| Diagnost              | ics                                           |                                                                                                                |                     |                      |                     |      |

| V <sub>DG</sub>       | Diagnostic threshold voltage                  | -                                                                                                              | 0.5·V <sub>DD</sub> | 0.55·V <sub>DD</sub> | 0.6·V <sub>DD</sub> | V    |

| I <sub>OUT OL</sub>   | Open load detection sink current              | V <sub>out</sub> = V <sub>DG</sub><br>Output programmed OFF                                                    | 30                  | 60                   | 100                 | μΑ   |

| t <sub>dly SFPD</sub> | Diagnostic detection filter time              | SFPD = Low, $V_{OUT} \ge V_{DG}$<br>CSB = 50% to valid data at SO                                              | 70                  | 150                  | 250                 | μs   |

| Outputs t             | timing                                        |                                                                                                                |                     |                      |                     | •    |

| t <sub>don</sub>      | Turn-on delay                                 | CSB = 50% to R <sub>L</sub> = 50 $\Omega$<br>V <sub>OUT</sub> = 0.9 V <sub>bat</sub> , V <sub>bat</sub> = 16 V | -                   | -                    | 20                  | μs   |

| t <sub>doff</sub>     | Turn-off delay                                | CSB = 50% to R <sub>L</sub> = 50 $\Omega$<br>V <sub>OUT</sub> = 0.1·V <sub>bat</sub> , V <sub>bat</sub> = 16 V | -                   | -                    | 20                  | μs   |

| dV <sub>on/dt</sub>   | Turn-on voltage slew-rate                     | 90% to 30% of V <sub>bat</sub> ;<br>R <sub>L</sub> = 50 Ω; V <sub>bat</sub> = 16 V                             | 0.7                 | 2.1                  | 3.5                 | V/µs |

| dV <sub>off/dt</sub>  | Turn-off voltage slew-rate                    | 30% to 90% of V <sub>bat</sub> ;<br>R <sub>L</sub> = 50 Ω; V <sub>bat</sub> = 16 V                             | 0.7                 | 2.1                  | 3.5                 | V/µs |

| dV <sub>off</sub>     | Turn-off voltage clamp slew-<br>rate          | 30% to 80% of $V_{OUT\ clamp}$ R <sub>L</sub> = 500 $\Omega$                                                   | 0.7                 | 2.1                  | 5.5                 | V/µs |

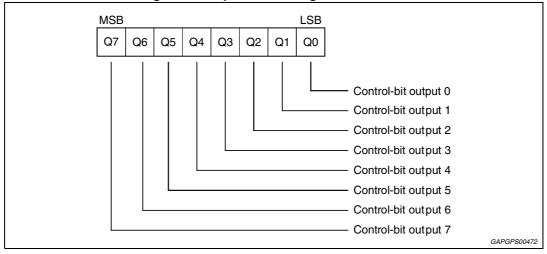

| Serial dia            | ignostic link (Load capacitor a               | t SO = 200 pF)                                                                                                 |                     |                      |                     |      |

| f <sub>sclk</sub>     | Clock frequency                               | 50% duty cycle                                                                                                 | 3                   | _                    | -                   | MHz  |

| t <sub>clh</sub>      | Minimum time SCLK = HIGH                      | -                                                                                                              | 160                 | -                    | -                   | ns   |

| t <sub>cll</sub>      | Minimum time SCLK = LOW                       | -                                                                                                              | 160                 | -                    | -                   | ns   |

| t <sub>pcld</sub>     | Propagation delay<br>SCLK to data at SO valid | 4.9 V ≤ V <sub>DD</sub> ≤ 5.1 V                                                                                | -                   | -                    | 100                 | ns   |

| t <sub>csdv</sub>     | CSB = LOW to data at SO active                | -                                                                                                              | -                   | -                    | 100                 | ns   |

| t <sub>sclch</sub>    | SCLK low before CSB low                       | Setup time SCLK to CSB change H/L                                                                              | 100                 | -                    | -                   | ns   |

| t <sub>hclcl</sub>    | SCLK change L/H after CSB = Low               | Setup time CSB to SCLK change L/H                                                                              | 100                 | -                    | -                   | ns   |

| t <sub>scld</sub>     | SI input setup time                           | SCLK change H/L after SI data valid                                                                            | 20                  | -                    | -                   | ns   |

10/19 DocID7791 Rev 7

Table 5. Electrical characteristics (continued)

| Symbol             | Parameter                      | Test condition                     | Min. | Тур. | Max. | Unit |

|--------------------|--------------------------------|------------------------------------|------|------|------|------|

| t <sub>hcld</sub>  | SI input hold time             | SI data hold after SCLK change H/L | -    | -    | 20   | ns   |

| t <sub>sclcl</sub> | SCLK low before CSB high       | -                                  | 150  | -    | -    | ns   |

| t <sub>hclch</sub> | SCLK high after CSB high       | -                                  | 15,  | -    | -    | ns   |

| t <sub>pchdz</sub> | CSB L/H to output data float   | -                                  | -    | -    | 100  | ns   |

| t <sub>Reset</sub> | Minimum Reset time Reset = Low | -                                  | -    | -    | 160  | ns   |

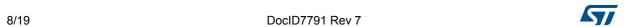

**Table 6. Outputs Control**

| Description | Value |     |  |

|-------------|-------|-----|--|

| SI-bit      | 0     | 1   |  |

| Output      | on    | off |  |

Figure 3. Output control register structure

# 2.4 Power outputs characteristics for flyback current, outputs short circuit protection and diagnostics

For output currents flowing into the circuit the output voltages are limited. The typical value of this voltage is 50V. This function allows that the flyback current of a inductive load recirculates into the circuit; the flyback energy is absorbed in the chip.

Output short circuit protection SFPD = Low (dedicated for loads without inrush current): when the output current exceeds the short circuit threshold, the corresponding output overload latch is set after a delay time  $t_{\text{dly SCB}}$  and the output is switched off. The delay timer is started after each rise of CSB and valid datas are transferred to the output control register. If the short takes place after the delay time has elapsed the shutdown is immediate (within 15  $\mu$ s).

Output short circuit protection SFPD = High (dedicated for loads with inrush current, as lamps): when the load current would exceed the short circuit limit value, the corresponding output goes in a current regulation mode. The output current is determined by the output characteristics and the output voltage depends on the load resistance. In this mode high power is dissipated in the output transistor and its temperature increases rapidly. When the power transistor temperature exceeds the thermal shutdown threshold, the overload latch is set and the corresponding output switched off.

For the load diagnostic in output off condition each output features a diagnostic current sink, of typ  $60 \, \mu A$ .

12/19 DocID7791 Rev 7

## 3 Functional description

### 3.1 General

The L9823 integrated circuit features 8 power low-side-driver outputs. Data is transmitted to the device using the Serial Peripheral Interface = SPI protocol. The power outputs features voltage clamping function for flyback current recirculation and are protected against short circuit to Vbat.

The diagnostics recognizes two outputs fault conditions: 1) overcurrent and thermal overload in switch-ON condition and 2) open load or short to GND in switch-OFF condition for all outputs. The outputs status can be read out via the serial interface.

The chip internal Reset is a OR function of the external Reset signal and internally generated undervoltage Reset signal.

## 3.2 Output stages control

Each output is controlled with its latch and with a common Reset line, which enables all outputs.

The control data are transmitted via the SI input, the timing of the serial interface is shown in *Figure 4*.

The device is selected with low CSB signal and the input data are transferred into the 8 bit shift register at every falling SCLK edge. The rising edge of the CSB latches the new data from the shift register to the drivers.

Figure 4. Timing of the serial interface

The SPI register data are transferred to the output latch at rising CSB edge. The digital filter between CSB and the output latch ensures that the data are transferred only after 8 SCLK cycles or multiple of 8 SCLK cycles since the last CSB falling edge. The CSB changes only at low SCLK.

### 3.3 Diagnostics

The output voltage at all outputs is compared with the diagnostic threshold, typ 0,55  $\bullet$  V<sub>DD</sub> = V<sub>DG</sub>.

| Output | Output voltage | Status bit | Output mode        |  |

|--------|----------------|------------|--------------------|--|

| off    | > DG-threshold | high       | correct operation  |  |

| off    | < DG-threshold | low        | fault condition 2) |  |

| on     | < DG-threshold | low        | correct operation  |  |

| on     | > DG-threshold | high       | fault condition 1) |  |

**Table 7. Diagnostic for outputs**

#### Fault condition 1

Output short circuit to Vbat:

- For SFPD = Low the output was switched on and the voltage at the output exceeded

the diagnostics threshold due to overcurrent, the output overload latch was set and the

output has been switched off. The diagnostic bit is high.

- For SFPD = high the output was switched on and the voltage at the output exceeds the diagnostics threshold. The output operates in current regulation mode or has been switched off due to thermal shutdown. The status bit is high.

#### Fault condition 2

Open load or output short circuit to GND:

- The output is switched off and the voltage at the output drops below the diagnostics threshold, because the load current is lower than the output diagnostic current source, the load is interrupted. The diagnostic bit is low.

- At the falling edge of CSB the output status data are transferred to the shift register.

When SCB is low, data bits contained in the shift register are transferred to SO output at every rising SCLK edge.

Figure 5. Pulse diagram to read the outputs status register

57

MSB

Diag7 Diag6 Diag5 Diag4 Diag3 Diag2 Diag1 Diag0

Diagnostic-bit output 0

Diagnostic-bit output 1

Diagnostic-bit output 2

Diagnostic-bit output 3

Diagnostic-bit output 4

Diagnostic-bit output 5

Diagnostic-bit output 6

Diagnostic-bit output 7

Figure 6. Structure of the outputs status register

## 4 Applications information

The typical application diagram for parallel Input SPI control is shown in Figure 7.

V<sub>BAT</sub> VOLT AGE REGULATOR OUT0 Over ото Te mperature Shift Register OUT2 Q3 СНЗ Q4 CH4 CH7 Reset Q7 CH7 μΡ Diag7 L9823 R, L loads Reset SO GND 5-8 17-20 L9823 GAPGPS00476

Figure 7. Typical application circuit diagram for the L9823 circuit.

For higher current driving capability more outputs of the same kind can be paralleled. In this case the maximum flyback energy should not exceed the limit value for single output.

The immunity of the circuit with respect to the transients at the output is verified during the characterization for Test Pulses 1, 2 and 3a, 3b, DIN40839 or ISO7637 part 3. The Test Pulses are coupled to the outputs with 200pF series capacitor. The correct function of the circuit with the Test Pulses coupled to the outputs is verified during the characterization for the typical application with R =  $16\Omega$  to  $200\Omega$ , L= 0 to 600mH loads. All outputs withstand test pulses without damage.

L9823 Package information

#### **Package information** 5

In order to meet environmental requirements, ST offers these devices in different grades of ECOPACK® packages, depending on their level of environmental compliance. ECOPACK® specifications, grade definitions and product status are available at: www.st.com.

ECOPACK® is an ST trademark.

Figure 8. SO24 mechanical data and package dimensions

#### **OUTLINE AND MECHANICAL DATA**

Revision history L9823

# 6 Revision history

**Table 8. Document revision history**

| Date        | Revision | Changes                                                                                                                            |  |

|-------------|----------|------------------------------------------------------------------------------------------------------------------------------------|--|

| 16-Apr-2003 | 4        | Initial release.                                                                                                                   |  |

| 13-Apr-2011 | 5        | Document reformatted. Added new order code in <i>Table 1: Device summary on page 1</i> .                                           |  |

| 17-Jun-2013 | 6        | Updated: Figure 3: Output control register structure on page 11 and Figure 6: Structure of the outputs status register on page 15. |  |

| 19-Sep-2013 | 7        | Updated Disclaimer.                                                                                                                |  |

#### Please Read Carefully:

Information in this document is provided solely in connection with ST products. STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, modifications or improvements, to this document, and the products and services described herein at any time, without notice.

All ST products are sold pursuant to ST's terms and conditions of sale.

Purchasers are solely responsible for the choice, selection and use of the ST products and services described herein, and ST assumes no liability whatsoever relating to the choice, selection or use of the ST products and services described herein.

No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted under this document. If any part of this document refers to any third party products or services it shall not be deemed a license grant by ST for the use of such third party products or services, or any intellectual property contained therein or considered as a warranty covering the use in any manner whatsoever of such third party products or services or any intellectual property contained therein.

UNLESS OTHERWISE SET FORTH IN ST'S TERMS AND CONDITIONS OF SALE ST DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY WITH RESPECT TO THE USE AND/OR SALE OF ST PRODUCTS INCLUDING WITHOUT LIMITATION IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE (AND THEIR EQUIVALENTS UNDER THE LAWS OF ANY JURISDICTION), OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT.

ST PRODUCTS ARE NOT DESIGNED OR AUTHORIZED FOR USE IN: (A) SAFETY CRITICAL APPLICATIONS SUCH AS LIFE SUPPORTING, ACTIVE IMPLANTED DEVICES OR SYSTEMS WITH PRODUCT FUNCTIONAL SAFETY REQUIREMENTS; (B) AERONAUTIC APPLICATIONS; (C) AUTOMOTIVE APPLICATIONS OR ENVIRONMENTS, AND/OR (D) AEROSPACE APPLICATIONS OR ENVIRONMENTS. WHERE ST PRODUCTS ARE NOT DESIGNED FOR SUCH USE, THE PURCHASER SHALL USE PRODUCTS AT PURCHASER'S SOLE RISK, EVEN IF ST HAS BEEN INFORMED IN WRITING OF SUCH USAGE, UNLESS A PRODUCT IS EXPRESSLY DESIGNATED BY ST AS BEING INTENDED FOR "AUTOMOTIVE, AUTOMOTIVE SAFETY OR MEDICAL" INDUSTRY DOMAINS ACCORDING TO ST PRODUCT DESIGN SPECIFICATIONS. PRODUCTS FORMALLY ESCC, QML OR JAN QUALIFIED ARE DEEMED SUITABLE FOR USE IN AEROSPACE BY THE CORRESPONDING GOVERNMENTAL AGENCY.

Resale of ST products with provisions different from the statements and/or technical features set forth in this document shall immediately void any warranty granted by ST for the ST product or service described herein and shall not create or extend in any manner whatsoever, any liability of ST.

ST and the ST logo are trademarks or registered trademarks of ST in various countries.

Information in this document supersedes and replaces all information previously supplied.

The ST logo is a registered trademark of STMicroelectronics. All other names are the property of their respective owners.

© 2013 STMicroelectronics - All rights reserved

STMicroelectronics group of companies

Australia - Belgium - Brazil - Canada - China - Czech Republic - Finland - France - Germany - Hong Kong - India - Israel - Italy - Japan - Malaysia - Malta - Morocco - Philippines - Singapore - Spain - Sweden - Switzerland - United Kingdom - United States of America

www.st.com

DocID7791 Rev 7 19/19

# **Mouser Electronics**

**Authorized Distributor**

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

## STMicroelectronics:

L9823 L9823013TR E-L9823 E-L9823013TR