Kaimeite Electronic (HK) Co., Limited

First choice One-Stop Mixed Distributor for World-Class manufacturer Email: info@kaimte.com Website: www.kaimte.com

## Click to view price, real time Inventory, Delivery & Lifecycle Information;

# CY7C68013A-100AXC

**Infineon Technologies**

USB Interface IC EZ USB FX2LP LO PWR Hi COM

Any questions, please feel free to contact us. info@kaimte.com

## Please note that Cypress is an Infineon Technologies Company.

The document following this cover page is marked as "Cypress" document as this is the company that originally developed the product. Please note that Infineon will continue to offer the product to new and existing customers as part of the Infineon product portfolio.

## **Continuity of document content**

The fact that Infineon offers the following product as part of the Infineon product portfolio does not lead to any changes to this document. Future revisions will occur when appropriate, and any changes will be set out on the document history page.

## **Continuity of ordering part numbers**

Infineon continues to support existing part numbers. Please continue to use the ordering part numbers listed in the datasheet for ordering.

www.infineon.com

## CY7C68013A/CY7C68014A CY7C68015A/CY7C68016A

# EZ-USB<sup>®</sup> FX2LP™ USB Microcontroller High-Speed USB Peripheral Controller

#### **Features**

- USB 2.0 USB IF Hi-Speed certified (TID # 40460272)

- Single-chip integrated USB 2.0 transceiver, smart SIE, and enhanced 8051 microprocessor

- Fit-, form-, and function-compatible with the FX2

- □ Pin-compatible0

- □ Object-code-compatible

- □ Functionally compatible (FX2LP is a superset)

- Ultra-low power: I<sub>CC</sub> no more than 85 mA in any mode □ Ideal for bus- and battery-powered applications

- Software: 8051 code runs from:

- □ Internal RAM, which is downloaded through USB

- □ Internal RAM, which is loaded from EEPROM

- □ External memory device (128-pin package)

- 16 KB of on-chip code/data RAM

- Four programmable BULK, INTERRUPT, and ISOCHRONOUS endpoints

- ☐ Buffering options: Double, triple, and quad

- Additional programmable (BULK/INTERRUPT) 64-byte endpoint

- 8-bit or 16-bit external data interface

- Smart media standard ECC generation

- GPIF™ (general programmable interface)

- □ Enables direct connection to most parallel interfaces

- □ Programmable waveform descriptors and configuration registers to define waveforms

- □ Supports multiple ready (RDY) inputs and control (CTL) outputs

- Integrated, industry-standard, enhanced 8051

- □ 48-MHz, 24-MHz, or 12-MHz CPU operation

- □ Four clocks per instruction cycle

- ☐ Two USARTs

- □ Three counter/timers

- □ Expanded interrupt system

- □ Two data pointers

- 3.3-V operation with 5-V tolerant inputs

- Vectored USB interrupts and GPIF/FIFO interrupts

- Separate data buffers for the setup and data portions of a CONTROL transfer

- Integrated I<sup>2</sup>C controller; runs at 100 or 400 kHz<sup>[1]</sup>

- Four integrated FIFOs

- □ Integrated glue logic and FIFOs lower system cost

- □ Automatic conversion to and from 16-bit buses

- Master or slave operation

- Uses external clock or asynchronous strobes

- □ Easy interface to ASIC and DSP ICs

- Available in commercial and industrial temperature grades (all packages except VFBGA)

#### Features (CY7C68013A/14A only)

- CY7C68014A: Ideal for battery-powered applications

□ Suspend current: 100 μA (typ)

- CY7C68013A: Ideal for nonbattery-powered applications

□ Suspend current: 300 μA (typ)

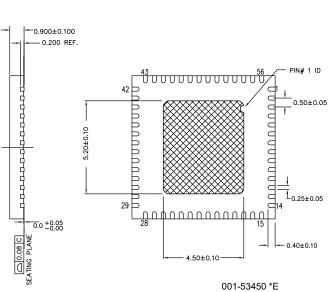

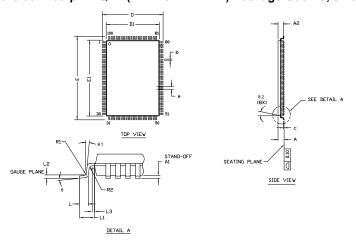

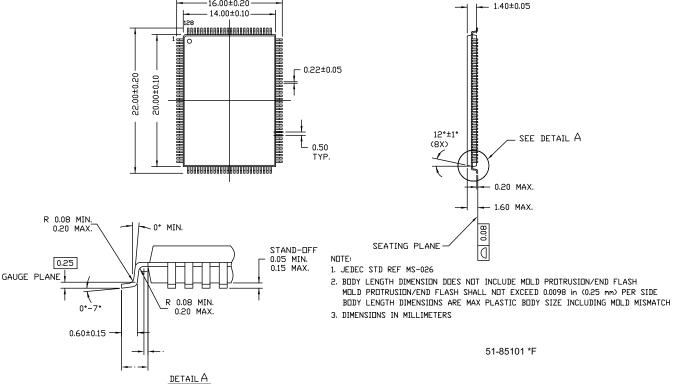

- Available in five Pb-free packages with up to 40 GPIOs

□ 128-pin TQFP (40 GPIOs), 100-pin TQFP (40 GPIOs), 56-pin

QFN (24 GPIOs), 56-pin SSOP (24 GPIOs), and 56-pin

VFBGA (24 GPIOs)

#### Features (CY7C68015A/16A only)

- CY7C68016A: Ideal for battery-powered applications

□ Suspend current: 100 µA (typ)

- CY7C68015A: Ideal for nonbattery-powered applications

□ Suspend current: 300 μA (typ)

- Available in Pb-free 56-pin QFN package (26 GPIOs)

- Two more GPIOs than CY7C68013A/14A enabling additional features in the same footprint

## **Functional Description**

For a complete list of related resources, click here.

Errata: For information on silicon errata, see "Errata" on page 68. Details include trigger conditions, devices affected, and proposed workaround.

#### Note

1. The actual I<sup>2</sup>C clock frequency will be different. The measured I<sup>2</sup>C clock frequency when set for 100 kHz and 400 kHz is around 85 kHz and 300 kHz respectively.

Cypress Semiconductor Corporation

Document Number: 38-08032 Rev. AC

#### **More Information**

Cypress provides a wealth of data at www.cypress.com to help you to select the right device for your design, and to help you to quickly and effectively integrate the device into your design. For a comprehensive list of resources, see the application note AN65209 - Getting Started with FX2LP.

- Overview: USB Portfolio, USB Roadmap

- USB 2.0 Product Selectors: FX2LP, AT2LP, NX2LP-Flex, SX2

- Application notes: Cypress offers a large number of USB application notes covering a broad range of topics, from basic to advanced level. Recommended application notes for getting started with FX2LP are:

- □ AN65209 Getting Started with FX2LP

- □ AN15456 Guide to Successful EZ-USB<sup>®</sup> FX2LP™ and EZ-USB FX1™ Hardware Design and Debug

- □ AN50963 EZ-USB® FX1™/FX2LP™ Boot Options

- □ AN66806 EZ-USB® FX2LP™ GPIF Design Guide

- □ AN61345 Implementing an FX2LP™- FPGA Interface

- □ AN57322 Interfacing SRAM with FX2LP over GPIF

- □ AN4053 Streaming Data through Isochronous/Bulk Endpoints on EZ-USB® FX2 and EZUSB FX2LP

- ¬ AN63787 EZ-USB<sup>®</sup> FX2LP™ GPIF and Slave FIFO Configuration Examples using 8-bit Asynchronous Interface

For complete list of Application notes, click here.

- Code Examples:

- □ USB Hi-Speed

- Technical Reference Manual (TRM):

- □ EZ-USB FX2LP Technical Reference Manual

- Reference Designs:

- CY4661 External USB Hard Disk Drives (HDD) with Fingerprint Authentication Security

- □ FX2LP DMB-T/H TV Dongle reference design

- Models: IBIS

#### **EZ-USB FX2LP Development Kit**

The CY3684 EZ-USB FX2LP Development Kit is a complete development resource for FX2LP. It provides a platform to develop and test custom projects using FX2LP. The development kit contains collateral materials for the firmware, hardware, and software aspects of a design using FX2LP.

#### **GPIF™** Designer

FX2LP™ General Programmable Interface (GPIF) provides an independent hardware unit, which creates the data and control signals required by an external interface. FX2LP GPIF Designer allows users to create and modify GPIF waveform descriptors for EZ-USB FX2/ FX2LP family of chips using a graphical user interface. Extensive discussion of general GPIF discussion and programming using GPIF Designer is included in FX2LP Technical Reference Manual and GPIF Designer User Guide, distributed with GPIF Designer. AN66806 - Getting Started with EZ-USB® FX2LP™ GPIF can be a good starting point.

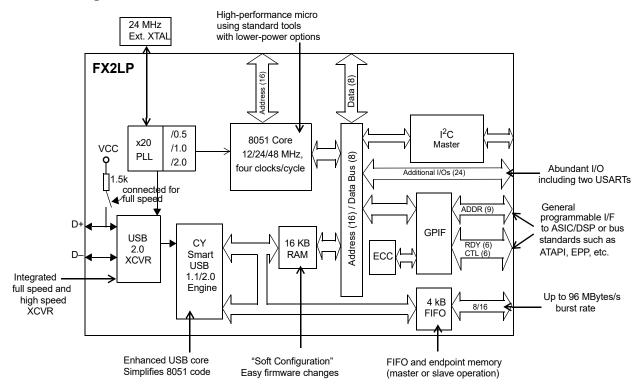

## **Logic Block Diagram**

Cypress's EZ-USB<sup>®</sup> FX2LP<sup>TM</sup> (CY7C68013A/14A) is a low-power version of the EZ-USB FX2<sup>TM</sup> (CY7C68013), which is a highly integrated, low-power USB 2.0 microcontroller. By integrating the USB 2.0 transceiver, serial interface engine (SIE), enhanced 8051 microcontroller, and a programmable peripheral interface in a single chip, Cypress has created a cost-effective solution that provides superior time-to-market advantages with low power to enable bus-powered applications.

The ingenious architecture of FX2LP results in data transfer rates of over 53 Mbytes per second (the maximum allowable USB 2.0 bandwidth), while still using a low-cost 8051 microcontroller in a package as small as a 56 VFBGA (5 mm × 5 mm). Because it incorporates the USB 2.0 transceiver, the FX2LP is more economical, providing a smaller-footprint solution than a USB 2.0 SIE or external transceiver implementations.

With EZ-USB FX2LP, the Cypress Smart SIE handles most of the USB 1.1 and 2.0 protocol in hardware, freeing the embedded microcontroller for application-specific functions and decreasing the development time to ensure USB compatibility.

The general programmable interface (GPIF) and Master/Slave Endpoint FIFO (8-bit or 16-bit data bus) provide an easy and glueless interface to popular interfaces such as ATA, UTOPIA, EPP, PCMCIA, and most DSP/processors.

The FX2LP draws less current than the FX2 (CY7C68013), has double the on-chip code/data RAM, and is fit, form, and function compatible with the 56-, 100-, and 128-pin FX2.

Five packages are defined for the family: 56-ball VFBGA, 56-pin SSOP, 56-pin QFN, 100-pin TQFP, and 128-pin TQFP.

Document Number: 38-08032 Rev. AC Page 3 of 75

## **Contents**

| Applications                        | 5  |

|-------------------------------------|----|

| Functional Overview                 | 5  |

| USB Signaling Speed                 | 5  |

| 8051 Microprocessor                 | 5  |

| I <sup>2</sup> C Bus                |    |

| Buses                               |    |

| USB Boot Methods                    | 6  |

| ReNumeration                        | 6  |

| Bus-Powered Applications            | 6  |

| Interrupt System                    | 6  |

| Reset and Wakeup                    |    |

| Program/Data RAM                    | 10 |

| Register Addresses                  | 12 |

| Endpoint RAM                        |    |

| External FIFO Interface             | 15 |

| GPIF                                | 15 |

| ECC Generation                      | 16 |

| USB Uploads and Downloads           | 16 |

| Autopointer Access                  | 16 |

| I <sup>2</sup> C Controller         | 16 |

| Compatible                          |    |

| with Previous Generation EZ-USB FX2 | 17 |

| CY7C68013A/14A                      |    |

| and CY7C68015A/16A Differences      | 17 |

| Pin Assignments                     | 18 |

| CY7C68013A/15A Pin Descriptions     | 25 |

| Register Summary                    | 34 |

| Absolute Maximum Ratings            | 41 |

| Operating Conditions                |    |

| Thermal Characteristics             |    |

| DC Electrical Characteristics       | 42 |

| USB Transceiver                     |    |

| AC Electrical Characteristics       | 43 |

| USB Transceiver                     |    |

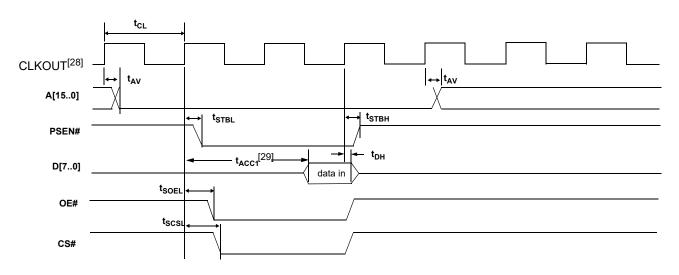

| Program Memory Read                 | 43 |

| Data Memory Read                    | 44 |

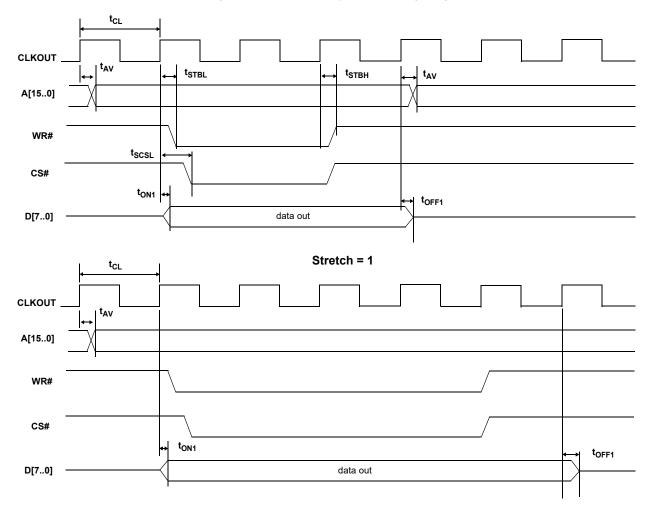

| Data Memory Write                                                                                                                                                                                                                                                                                                                             | 45                                        |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------|

| PORTC Strobe Feature Timings                                                                                                                                                                                                                                                                                                                  | 46                                        |

| GPIF Synchronous Signals                                                                                                                                                                                                                                                                                                                      |                                           |

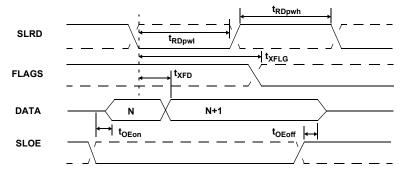

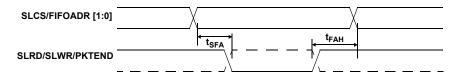

| Slave FIFO Synchronous Read                                                                                                                                                                                                                                                                                                                   |                                           |

| Slave FIFO Asynchronous Read                                                                                                                                                                                                                                                                                                                  |                                           |

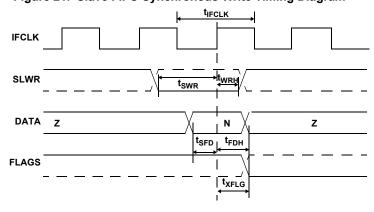

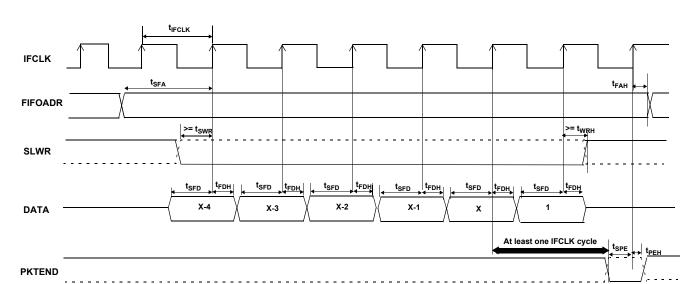

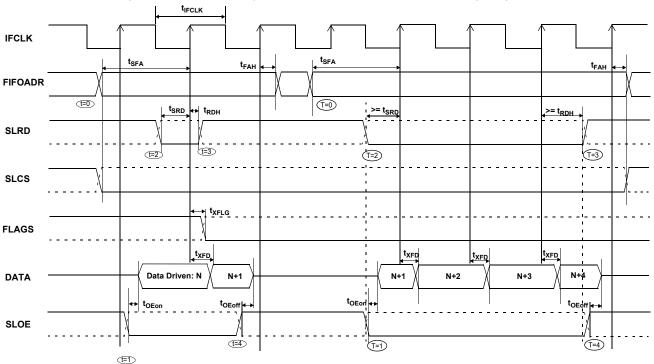

| Slave FIFO Synchronous Write                                                                                                                                                                                                                                                                                                                  |                                           |

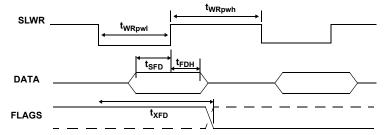

| Slave FIFO Asynchronous Write                                                                                                                                                                                                                                                                                                                 |                                           |

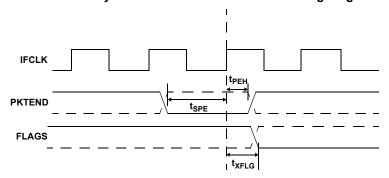

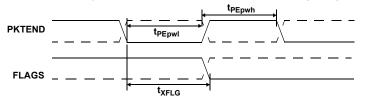

| Slave FIFO Synchronous Packet End Strobe                                                                                                                                                                                                                                                                                                      |                                           |

| Slave FIFO Asynchronous Packet End Strobe                                                                                                                                                                                                                                                                                                     |                                           |

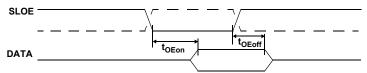

| Slave FIFO Output Enable                                                                                                                                                                                                                                                                                                                      |                                           |

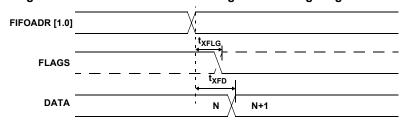

| Slave FIFO Address to Flags/Data                                                                                                                                                                                                                                                                                                              |                                           |

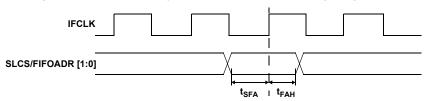

| Slave FIFO Synchronous Address                                                                                                                                                                                                                                                                                                                |                                           |

| Slave FIFO Asynchronous Address                                                                                                                                                                                                                                                                                                               |                                           |

| Sequence Diagram                                                                                                                                                                                                                                                                                                                              |                                           |

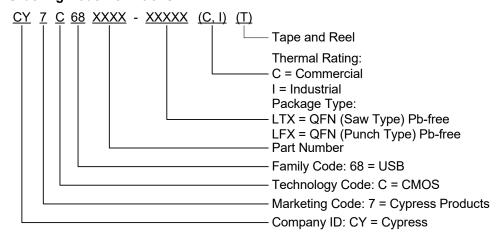

| Ordering Information                                                                                                                                                                                                                                                                                                                          |                                           |

| Ordering Code Definitions                                                                                                                                                                                                                                                                                                                     |                                           |

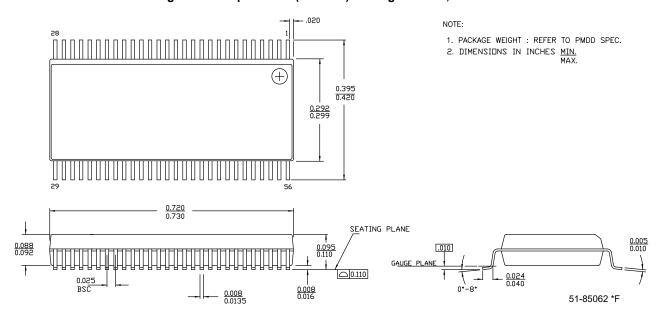

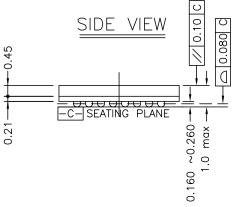

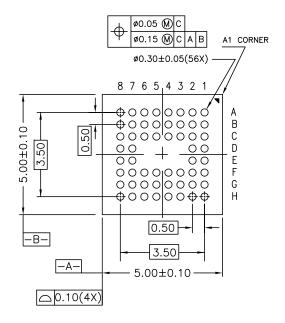

| Package Diagrams                                                                                                                                                                                                                                                                                                                              | 61                                        |

|                                                                                                                                                                                                                                                                                                                                               |                                           |

| PCB Layout Recommendations                                                                                                                                                                                                                                                                                                                    |                                           |

| Quad Flat Package No Leads (QFN) Package                                                                                                                                                                                                                                                                                                      | 65                                        |

| Quad Flat Package No Leads (QFN) Package<br>Design Notes                                                                                                                                                                                                                                                                                      | 65<br>66                                  |

| Quad Flat Package No Leads (QFN) Package<br>Design Notes<br>Acronyms                                                                                                                                                                                                                                                                          | 65<br>66<br>67                            |

| Quad Flat Package No Leads (QFN) Package Design Notes Acronyms Document Conventions                                                                                                                                                                                                                                                           | 65<br>66<br>67                            |

| Quad Flat Package No Leads (QFN) Package Design Notes Acronyms Document Conventions Units of Measure                                                                                                                                                                                                                                          | <b>65</b><br><b>66</b><br><b>67</b><br>67 |

| Quad Flat Package No Leads (QFN) Package Design Notes Acronyms Document Conventions Units of Measure                                                                                                                                                                                                                                          | 65 66 67 67 68                            |

| Quad Flat Package No Leads (QFN) Package Design Notes                                                                                                                                                                                                                                                                                         | 65 66 67 67 68                            |

| Quad Flat Package No Leads (QFN) Package Design Notes  Acronyms  Occument Conventions  Units of Measure  Errata  Part Numbers Affected  CY7C68013A/14A/15A/16A Qualification Status                                                                                                                                                           | 65 66 67 67 67 68 68                      |

| Quad Flat Package No Leads (QFN) Package Design Notes  Acronyms  Occument Conventions  Units of Measure  Errata  Part Numbers Affected  CY7C68013A/14A/15A/16A Qualification Status  CY7C68013A/14A/15A/16A Errata Summary                                                                                                                    | 65 66 67 67 67 68 68 68                   |

| Quad Flat Package No Leads (QFN) Package Design Notes  Acronyms  Occument Conventions  Units of Measure  Errata  Part Numbers Affected  CY7C68013A/14A/15A/16A Qualification Status  CY7C68013A/14A/15A/16A Errata Summary  Occument History Page                                                                                             | 65 66 67 67 68 68 68                      |

| Quad Flat Package No Leads (QFN) Package Design Notes  Acronyms  Document Conventions  Units of Measure  Errata  Part Numbers Affected  CY7C68013A/14A/15A/16A Qualification Status  CY7C68013A/14A/15A/16A Errata Summary  Document History Page  Sales, Solutions, and Legal Information                                                    | 65 66 67 67 68 68 68 68 75                |

| Quad Flat Package No Leads (QFN) Package Design Notes  Acronyms  Document Conventions  Units of Measure  Errata  Part Numbers Affected  CY7C68013A/14A/15A/16A Qualification Status  CY7C68013A/14A/15A/16A Errata Summary  Document History Page  Sales, Solutions, and Legal Information  Worldwide Sales and Design Support                | 65 66 67 67 68 68 68 69 75                |

| Quad Flat Package No Leads (QFN) Package Design Notes  Acronyms  Document Conventions  Units of Measure  Errata  Part Numbers Affected  CY7C68013A/14A/15A/16A Qualification Status  CY7C68013A/14A/15A/16A Errata Summary  Document History Page  Sales, Solutions, and Legal Information  Worldwide Sales and Design Support  Products      | 65 66 67 67 68 68 68 69 75                |

| Quad Flat Package No Leads (QFN) Package Design Notes Acronyms Document Conventions Units of Measure Errata Part Numbers Affected CY7C68013A/14A/15A/16A Qualification Status CY7C68013A/14A/15A/16A Errata Summary Document History Page Sales, Solutions, and Legal Information Worldwide Sales and Design Support Products PSoC® Solutions | 65 66 67 67 68 68 68 69 75 75             |

| Quad Flat Package No Leads (QFN) Package Design Notes  Acronyms  Document Conventions  Units of Measure  Errata  Part Numbers Affected  CY7C68013A/14A/15A/16A Qualification Status  CY7C68013A/14A/15A/16A Errata Summary  Document History Page  Sales, Solutions, and Legal Information  Worldwide Sales and Design Support  Products      | 65 66 67 68 68 68 69 75 75                |

## **Applications**

- Portable video recorder

- MPEG/TV conversion

- DSL modems

- ATA interface

- Memory card readers

- Legacy conversion devices

- Cameras

- Scanners

- Wireless LAN

- MP3 players

- Networking

The "Reference Designs" section of the Cypress web site provides additional tools for typical USB 2.0 applications. Each reference design comes complete with firmware source and object code, schematics, and documentation. Visit www.cypress.com for more information.

## **Functional Overview**

#### **USB Signaling Speed**

FX2LP operates at two of the three rates defined in the USB Specification Revision 2.0, dated April 27, 2000:

- Full speed, with a signaling bit rate of 12 Mbps

- High speed, with a signaling bit rate of 480 Mbps

FX2LP does not support the Low Speed signaling mode of 1.5 Mbps.

#### **8051 Microprocessor**

The 8051 microprocessor embedded in the FX2LP family has 256 bytes of register RAM, an expanded interrupt system, three timer/counters, and two USARTs.

#### 8051 Clock Frequency

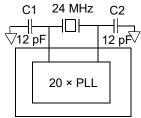

FX2LP has an on-chip oscillator circuit that uses an external 24-MHz (±100 ppm) crystal with the following characteristics:

- Parallel resonant

- Fundamental mode

- 500-µW drive level

- 12-pF (5% tolerance) load capacitors

An on-chip PLL multiplies the 24-MHz oscillator up to 480 MHz, as required by the transceiver/PHY; internal counters divide it down for use as the 8051 clock. The default 8051 clock frequency is 12 MHz. The clock frequency of the 8051 can be changed by the 8051 through the CPUCS register, dynamically.

#### Figure 1. Crystal Configuration

12-pF capacitor values assume a trace capacitance of 3 pF per side on a four-layer FR4 PCA

The CLKOUT pin, which can be three-stated and inverted using internal control bits, outputs the 50% duty cycle 8051 clock, at the selected 8051 clock frequency: 48 MHz, 24 MHz, or 12 MHz.

#### **USARTs**

FX2LP contains two standard 8051 USARTs, addressed through Special Function Register (SFR) bits. The USART interface pins are available on separate I/O pins, and are not multiplexed with port pins.

UART0 and UART1 can operate using an internal clock at 230 KBaud with no more than 1% baud rate error. 230 KBaud operation is achieved by an internally derived clock source that generates overflow pulses at the appropriate time. The internal clock adjusts for the 8051 clock rate (48 MHz, 24 MHz, and 12 MHz) such that it always presents the correct frequency for the 230-KBaud operation<sup>[2]</sup>.

## Special Function Registers

Certain 8051 SFR addresses are populated to provide fast access to critical FX2LP functions. These SFR additions are shown in Table 1 on page 6. Bold type indicates nonstandard, enhanced 8051 registers. The two SFR rows that end with "0" and "8" contain bit-addressable registers. The four I/O ports A to D use the SFR addresses used in the standard 8051 for ports 0 to 3, which are not implemented in FX2LP. Because of the faster and more efficient SFR addressing, the FX2LP I/O ports are not addressable in external RAM space (using the MOVX instruction).

#### I<sup>2</sup>C Bus

FX2LP supports the I<sup>2</sup>C bus as a master only at 100/400 kHz<sup>[3]</sup>. SCL and SDA pins have open-drain outputs and hysteresis inputs. These signals must be pulled up to 3.3 V, even if no I<sup>2</sup>C device is connected.

#### **Buses**

All packages, 8-bit or 16-bit "FIFO" bidirectional data bus, multiplexed on I/O ports B and D. 128-pin package: adds 16-bit output-only 8051 address bus, 8-bit bidirectional data bus.

#### Notes

- 2. 115-KBaud operation is also possible by programming the 8051 SMOD0 or SMOD1 bits to a "1" for UART0, UART1, or both respectively.

- 3. The actual I<sup>2</sup>C clock frequency will be different. The measured I<sup>2</sup>C clock frequency when set for 100 kHz and 400 kHz is around 85 kHz and 300 kHz respectively.

**Table 1. Special Function Registers**

| X | 8x    | 9x        | Ax            | Вх             | Сх     | Dx    | Ex  | Fx  |

|---|-------|-----------|---------------|----------------|--------|-------|-----|-----|

| 0 | IOA   | IOB       | IOC           | IOD            | SCON1  | PSW   | ACC | В   |

| 1 | SP    | EXIF      | INT2CLR       | IOE            | SBUF1  | -     | _   | -   |

| 2 | DPL0  | MPAGE     | INT4CLR       | OEA            | _      | _     | _   | _   |

| 3 | DPH0  | _         | _             | OEB            | _      | _     | _   | _   |

| 4 | DPL1  | _         | _             | OEC            | _      | -     | _   | -   |

| 5 | DPH1  | _         | _             | OED            | _      | _     | _   | _   |

| 6 | DPS   | _         | _             | OEE            | _      | _     | _   | _   |

| 7 | PCON  | _         | _             | _              | _      | -     | _   | -   |

| 8 | TCON  | SCON0     | IE            | IP             | T2CON  | EICON | EIE | EIP |

| 9 | TMOD  | SBUF0     | _             | _              | _      | _     | _   | _   |

| Α | TL0   | AUTOPTRH1 | EP2468STAT    | EP01STAT       | RCAP2L | _     | _   | _   |

| В | TL1   | AUTOPTRL1 | EP24FIFOFLGS  | GPIFTRIG       | RCAP2H | _     | _   | _   |

| С | TH0   | reserved  | EP68FIFOFLGS  |                | TL2    | _     | _   | _   |

| D | TH1   | AUTOPTRH2 | -             | GPIFSGLDATH    | TH2    | _     | _   | _   |

| Е | CKCON | AUTOPTRL2 | -             | GPIFSGLDATLX   | _      | _     | _   | _   |

| F | _     | reserved  | AUTOPTRSET-UP | GPIFSGLDATLNOX | _      | _     | _   | _   |

#### **USB Boot Methods**

During the power-up sequence, internal logic checks the I<sup>2</sup>C port for the connection of an EEPROM whose first byte is either 0xC0 or 0xC2. If found, it uses the VID/PID/DID values in the EEPROM in place of the internally stored values (0xC0), or it boot-loads the EEPROM contents into internal RAM (0xC2). If no EEPROM is detected, FX2LP enumerates using internally stored descriptors. The default ID values for FX2LP are VID/PID/DID (0x04B4, 0x8613, 0xAxxx where xxx = Chip revision)<sup>[4]</sup>.

Table 2. Default ID Values for FX2LP

| Default VID/PID/DID |        |                                                                                |  |

|---------------------|--------|--------------------------------------------------------------------------------|--|

| Vendor ID           | 0x04B4 | Cypress Semiconductor                                                          |  |

| Product ID          | 0x8613 | EZ-USB FX2LP                                                                   |  |

| Device release      | 0xAnnn | Depends on chip revision<br>(nnn = chip revision where first<br>silicon = 001) |  |

#### ReNumeration

Because the FX2LP's configuration is soft, one chip can take on the identities of multiple distinct USB devices.

When first plugged into USB, the FX2LP enumerates automatically and downloads firmware and USB descriptor tables over the USB cable. Next, the FX2LP enumerates again, this time as a device defined by the downloaded information. This patented two step process called ReNumeration \*\*M\* happens instantly when the device is plugged in, without a hint that the initial download step has occurred.

Two control bits in the USBCS (USB Control and Status) register control the ReNumeration process: DISCON and RENUM. To simulate a USB disconnect, the firmware sets DISCON to 1. To reconnect, the firmware clears DISCON to 0.

Before reconnecting, the firmware sets or clears the RENUM bit to indicate whether the firmware or the Default USB Device handles device requests over endpoint zero: if RENUM = 0, the Default USB Device handles device requests; if RENUM = 1, the firmware services the requests.

#### **Bus-Powered Applications**

The FX2LP fully supports bus-powered designs by enumerating with less than 100 mA as required by the USB 2.0 specification.

#### **Interrupt System**

INT2 Interrupt Request and Enable Registers

FX2LP implements an autovector feature for INT2 and INT4. There are 27 INT2 (USB) vectors, and 14 INT4 (FIFO/GPIF) vectors. See EZ-USB Technical Reference Manual (TRM) for more details.

#### USB Interrupt Autovectors

The main USB interrupt is shared by 27 interrupt sources. To save the code and processing time that is required to identify the individual USB interrupt source, the FX2LP provides a second level of interrupt vectoring, called Autovectoring. When a USB interrupt is asserted, the FX2LP pushes the program counter to its stack, and then jumps to the address 0x0043 where it expects to find a "jump" instruction to the USB interrupt service routine.

#### Note

4. The I<sup>2</sup>C bus SCL and SDA pins must be pulled up, even if an EEPROM is not connected. Otherwise this detection method does not work properly.

Document Number: 38-08032 Rev. AC Page 6 of 75

The FX2LP jump instruction is encoded as follows:

Table 3. INT2 USB Interrupts

|          | USB INTERRUPT TABLE FOR INT2 |           |                                            |  |  |  |

|----------|------------------------------|-----------|--------------------------------------------|--|--|--|

| Priority | INT2VEC Value                | Source    | Notes                                      |  |  |  |

| 1        | 00                           | SUDAV     | Setup data available                       |  |  |  |

| 2        | 04                           | SOF       | Start of frame (or microframe)             |  |  |  |

| 3        | 08                           | SUTOK     | Setup token received                       |  |  |  |

| 4        | 0C                           | SUSPEND   | USB suspend request                        |  |  |  |

| 5        | 10                           | USB RESET | Bus reset                                  |  |  |  |

| 6        | 14                           | HISPEED   | Entered high speed operation               |  |  |  |

| 7        | 18                           | EP0ACK    | FX2LP ACK'd the CONTROL Handshake          |  |  |  |

| 8        | 1C                           |           | reserved                                   |  |  |  |

| 9        | 20                           | EP0-IN    | EP0-IN ready to be loaded with data        |  |  |  |

| 10       | 24                           | EP0-OUT   | EP0-OUT has USB data                       |  |  |  |

| 11       | 28                           | EP1-IN    | EP1-IN ready to be loaded with data        |  |  |  |

| 12       | 2C                           | EP1-OUT   | EP1-OUT has USB data                       |  |  |  |

| 13       | 30                           | EP2       | IN: buffer available. OUT: buffer has data |  |  |  |

| 14       | 34                           | EP4       | IN: buffer available. OUT: buffer has data |  |  |  |

| 15       | 38                           | EP6       | IN: buffer available. OUT: buffer has data |  |  |  |

| 16       | 3C                           | EP8       | IN: buffer available. OUT: buffer has data |  |  |  |

| 17       | 40                           | IBN       | IN-Bulk-NAK (any IN endpoint)              |  |  |  |

| 18       | 44                           |           | reserved                                   |  |  |  |

| 19       | 48                           | EP0PING   | EP0 OUT was pinged and it NAK'd            |  |  |  |

| 20       | 4C                           | EP1PING   | EP1 OUT was pinged and it NAK'd            |  |  |  |

| 21       | 50                           | EP2PING   | EP2 OUT was pinged and it NAK'd            |  |  |  |

| 22       | 54                           | EP4PING   | EP4 OUT was pinged and it NAK'd            |  |  |  |

| 23       | 58                           | EP6PING   | EP6 OUT was pinged and it NAK'd            |  |  |  |

| 24       | 5C                           | EP8PING   | EP8 OUT was pinged and it NAK'd            |  |  |  |

| 25       | 60                           | ERRLIMIT  | Bus errors exceeded the programmed limit   |  |  |  |

| 26       | 64                           | _         | -                                          |  |  |  |

| 27       | 68                           | _         | Reserved                                   |  |  |  |

| 28       | 6C                           | _         | Reserved                                   |  |  |  |

| 29       | 70                           | EP2ISOERR | ISO EP2 OUT PID sequence error             |  |  |  |

| 30       | 74                           | EP4ISOERR | ISO EP4 OUT PID sequence error             |  |  |  |

| 31       | 78                           | EP6ISOERR | ISO EP6 OUT PID sequence error             |  |  |  |

| 32       | 7C                           | EP8ISOERR | ISO EP8 OUT PID sequence error             |  |  |  |

If Autovectoring is enabled (AV2EN = 1 in the INTSET-UP register), the FX2LP substitutes its INT2VEC byte. Therefore, if the high byte ("page") of a jump table address is preloaded at the location 0x0044, the automatically inserted INT2VEC byte at 0x0045 directs the jump to the correct address out of the 27 addresses within the page.

Document Number: 38-08032 Rev. AC Page 7 of 75

#### FIFO/GPIF Interrupt (INT4)

Just as the USB Interrupt is shared among 27 individual USB interrupt sources, the FIFO/GPIF interrupt is shared among 14 individual FIFO/GPIF sources. The FIFO/GPIF Interrupt, similar to the USB Interrupt, can employ autovectoring.

Table 4 shows the priority and INT4VEC values for the 14 FIFO/GPIF interrupt sources.

Table 4. Individual FIFO/GPIF Interrupt Sources

| Priority | INT4VEC Value | Source   | Notes                                |

|----------|---------------|----------|--------------------------------------|

| 1        | 80            | EP2PF    | Endpoint 2 programmable flag         |

| 2        | 84            | EP4PF    | Endpoint 4 programmable flag         |

| 3        | 88            | EP6PF    | Endpoint 6 programmable flag         |

| 4        | 8C            | EP8PF    | Endpoint 8 programmable flag         |

| 5        | 90            | EP2EF    | Endpoint 2 empty flag <sup>[5]</sup> |

| 6        | 94            | EP4EF    | Endpoint 4 empty flag                |

| 7        | 98            | EP6EF    | Endpoint 6 empty flag                |

| 8        | 9C            | EP8EF    | Endpoint 8 empty flag                |

| 9        | A0            | EP2FF    | Endpoint 2 full flag                 |

| 10       | A4            | EP4FF    | Endpoint 4 full flag                 |

| 11       | A8            | EP6FF    | Endpoint 6 full flag                 |

| 12       | AC            | EP8FF    | Endpoint 8 full flag                 |

| 13       | В0            | GPIFDONE | GPIF operation complete              |

| 14       | B4            | GPIFWF   | GPIF waveform                        |

If Autovectoring is enabled (AV4EN = 1 in the INTSET-UP register), the FX 2LP substitutes its INT4VEC byte. Therefore, if the high byte ("page") of a jump-table address is preloaded at location 0x0054, the automatically inserted INT4VEC byte at 0x0055 directs the jump to the correct address out of the 14 addresses within the page. When the ISR occurs, the FX2LP pushes the program counter to its stack then jumps to address 0x0053, where it expects to find a "jump" instruction to the interrupt service routine (ISR).

#### Note

Document Number: 38-08032 Rev. AC Page 8 of 75

Errata: In Slave FIFO Asynchronous Word Wide mode, if a single word data is transferred from the USB host to EP2, configured as OUT Endpoint (EP) in the first transaction, then the Empty flag behaves incorrectly. This does not happen if the data size is more than one word in the first transaction. For more information, see the "Errata" on page 68.

#### **Reset and Wakeup**

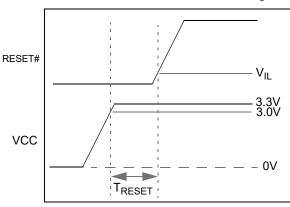

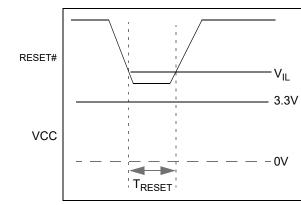

#### Reset Pin

The input pin, RESET#, resets the FX2LP when asserted. This pin has hysteresis and is active LOW. When a crystal is used with the CY7C680xxA, the reset period must enable stabilization of the crystal and the PLL. This reset period must be approximately 5 ms after VCC reaches 3.0 V. If the crystal input pin is driven by a clock signal, the internal PLL stabilizes in 200  $\mu s$  after VCC has reached 3.0  $V^{[6]}$ .

Figure 2 shows a power-on reset condition and a reset applied during operation. A power-on reset is defined as the time reset that is asserted while power is being applied to the circuit. A powered reset is when the FX2LP is powered on and operating and the RESET# pin is asserted.

Cypress provides an application note which describes and recommends power-on reset implementation. For more information about reset implementation for the FX2 family of products, visit <a href="http://www.cypress.com">http://www.cypress.com</a>.

Figure 2. Reset Timing Plots

Power on Reset

Powered Reset

Table 5. Reset Timing Values

| Condition                          | T <sub>RESET</sub>            |

|------------------------------------|-------------------------------|

| Power-on reset with crystal        | 5 ms                          |

| Power-on reset with external clock | 200 μs + clock stability time |

| Powered reset                      | 200 μs                        |

#### Wakeup Pins

The 8051 puts itself and the rest of the chip into a power-down mode by setting PCON.0 = 1. This stops the oscillator and PLL. When WAKEUP is asserted by external logic, the oscillator restarts after the PLL stabilizes, and the 8051 receives a wakeup interrupt. This applies irrespective of whether FX2LP is connected to the USB.

The FX2LP exits the power-down (USB suspend) state by using one of the following methods:

- USB bus activity (if D+/D- lines are left floating, noise on these lines may indicate activity to the FX2LP and initiate a wakeup)

- External logic asserts the WAKEUP pin

- External logic asserts the PA3/WU2 pin

The second wakeup pin, WU2, can also be configured as a general-purpose I/O pin. This enables a simple external R-C network to be used as a periodic wakeup source. WAKEUP is by default active LOW.

Document Number: 38-08032 Rev. AC Page 9 of 75

#### Program/Data RAM

Size

The FX2LP has 16 KB of internal program/data RAM, where PSEN#/RD# signals are internally ORed to enable the 8051 to access it as both program and data memory. No USB control registers appears in this space.

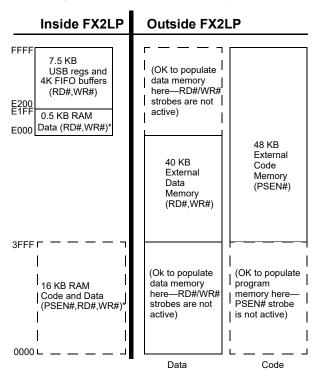

Two memory maps are shown in the following diagrams:

Figure 3 shows the Internal Code Memory, EA = 0.

Figure 4 on page 11 shows the External Code Memory, EA = 1.

Internal Code Memory, EA = 0

This mode implements the internal 16 KB block of RAM (starting at 0) as combined code and data memory. When external RAM or ROM is added, the external read and write strobes are

suppressed for memory spaces that exist inside the chip. This enables the user to connect a 64 KB memory without requiring address decodes to keep clear of internal memory spaces.

Only the internal 16 KB and scratch pad 0.5 KB RAM spaces have the following access:

- USB download

- USB upload

- Setup data pointer

- I<sup>2</sup>C interface boot load

External Code Memory, EA = 1

The bottom 16 KB of program memory is external and therefore the bottom 16 KB of internal RAM is accessible only as a data memory.

Figure 3. Internal Code Memory, EA = 0

\*SUDPTR, USB upload/download, I<sup>2</sup>C interface boot access

#### Note

6. If the external clock is powered at the same time as the CY7C680xxA and has a stabilization wait period, it must be added to the 200  $\mu$ s.

Document Number: 38-08032 Rev. AC

Inside FX2LP **Outside FX2LP** FFFF 7.5 KB USB regs and 4K FIFO buffers (OK to populate data memory here—RD#/WR# strobes are not (RD#,WR#) E200 E1FF active) 0.5 KB RAM Data (RD#,WR#)\* 40 KB External Data 64 KB External Code (RD#,WR#) Memory (PSEN#) 3FFF (Ok to populate 16 KB data memory here—RD#/WR# strobes are not RAM Data (RD#,WR#)\* active) 0000 \_ Data Code

Figure 4. External Code Memory, EA = 1

\*SUDPTR, USB upload/download, I<sup>2</sup>C interface boot access

Document Number: 38-08032 Rev. AC Page 11 of 75

## **Register Addresses**

| FFFF         | 4 KB EP2-EP8<br>buffers<br>(8 x 512) |

|--------------|--------------------------------------|

| F000<br>EFFF |                                      |

| E800         | 2 KB RESERVED                        |

| E7FF<br>E7C0 | 64 BEP1IN                            |

| E7BF<br>E780 | 64 Bytes EP1OUT                      |

| E77F<br>E740 | 64 Bytes EP0 IN/OUT                  |

| E73F<br>E700 | 64 Bytes RESERVED                    |

| E6FF<br>E500 | 8051 Addressable Registers (512)     |

| E4FF<br>E480 | Reserved (128)                       |

| E47F<br>E400 | 128 Bytes GPIF Waveforms             |

| E3FF<br>E200 | Reserved (512)                       |

| E1FF         | 512 Bytes<br>8051 xdata RAM          |

| E000         |                                      |

Document Number: 38-08032 Rev. AC Page 12 of 75

#### **Endpoint RAM**

#### Size

■ 3 × 64 bytes (Endpoints 0 and 1)

■ 8 × 512 bytes (Endpoints 2, 4, 6, 8)

#### Organization

- EP0

- Bidirectional endpoint zero, 64-byte buffer

- EP1IN, EP1OUT

- 64 byte buffers, bulk or interrupt

- EP2, 4, 6, 8

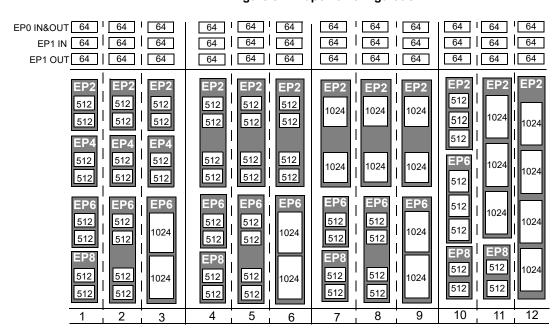

- Eight 512-byte buffers, bulk, interrupt, or isochronous. EP4 and EP8 can be double buffered; EP2 and 6 can be either double, triple, or quad buffered. For Hi-Speed endpoint configuration options, see Figure 5.

Setup Data Buffer

A separate 8-byte buffer at 0xE6B8-0xE6BF holds the setup data from a CONTROL transfer.

Endpoint Configurations (Hi-Speed Mode)

Endpoints 0 and 1 are the same for every configuration. Endpoint 0 is the only CONTROL endpoint, and endpoint 1 can be either BULK or INTERRUPT.

The endpoint buffers can be configured in any 1 of the 12 configurations shown in the vertical columns. When operating in the Full-Speed BULK mode, only the first 64 bytes of each buffer are used. For example, in Hi-Speed mode, the max packet size is 512 bytes, but in Full-Speed mode, it is 64 bytes. Even though a buffer is configured to a 512-byte buffer, in Full-Speed mode, only the first 64 bytes are used. The unused endpoint buffer space is not available for other operations. An example endpoint configuration is the EP2–1024 double-buffered; EP6–512 quad-buffered (column 8).

Figure 5. Endpoint Configuration

Document Number: 38-08032 Rev. AC Page 13 of 75

## Default Full-Speed Alternate Settings

## Table 6. Default Full Speed Alternate Settings<sup>[7, 8]</sup>

| Alternate Setting | 0  | 1                | 2                | 3                |

|-------------------|----|------------------|------------------|------------------|

| ep0               | 64 | 64               | 64               | 64               |

| ep1out            | 0  | 64 bulk          | 64 int           | 64 int           |

| ep1in             | 0  | 64 bulk          | 64 int           | 64 int           |

| ep2               | 0  | 64 bulk out (2×) | 64 int out (2×)  | 64 iso out (2×)  |

| ep4               | 0  | 64 bulk out (2×) | 64 bulk out (2×) | 64 bulk out (2×) |

| ер6               | 0  | 64 bulk in (2×)  | 64 int in (2×)   | 64 iso in (2×)   |

| ep8               | 0  | 64 bulk in (2×)  | 64 bulk in (2×)  | 64 bulk in (2×)  |

## Default High Speed Alternate Settings

## Table 7. Default Hi-Speed Alternate Settings<sup>[7, 8]</sup>

| Alternate Setting | 0  | 1                       | 2                 | 3                 |

|-------------------|----|-------------------------|-------------------|-------------------|

| ер0               | 64 | 64                      | 64                | 64                |

| ep1out            | 0  | 512 bulk <sup>[9]</sup> | 64 int            | 64 int            |

| ep1in             | 0  | 512 bulk <sup>[9]</sup> | 64 int            | 64 int            |

| ep2               | 0  | 512 bulk out (2×)       | 512 int out (2×)  | 512 iso out (2×)  |

| ep4               | 0  | 512 bulk out (2×)       | 512 bulk out (2×) | 512 bulk out (2×) |

| ер6               | 0  | 512 bulk in (2×)        | 512 int in (2×)   | 512 iso in (2×)   |

| ep8               | 0  | 512 bulk in (2×)        | 512 bulk in (2×)  | 512 bulk in (2×)  |

#### Notes

Document Number: 38-08032 Rev. AC Page 14 of 75

<sup>7. &</sup>quot;0" means "not implemented." 8. "2×" means "double buffered."

<sup>9.</sup> Even though these buffers are 64 bytes, they are reported as 512 for USB 2.0 compliance. The user must never transfer packets larger than 64 bytes to EP1.

#### **External FIFO Interface**

#### Architecture

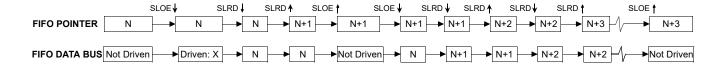

The FX2LP slave FIFO architecture has eight 512-byte blocks in the endpoint RAM that directly serve as FIFO memories and are controlled by FIFO control signals (such as IFCLK, SLCS#, SLRD, SLWR, SLOE, PKTEND, and flags).

In operation, some of the eight RAM blocks fill or empty from the SIE, while the others are connected to the I/O transfer logic. The transfer logic takes two forms: the GPIF for internally generated control signals and the slave FIFO interface for externally controlled transfers.

#### Master/Slave Control Signals

The FX2LP endpoint FIFOs are implemented as eight physically distinct 256×16 RAM blocks. The 8051/SIE can switch any of the RAM blocks between two domains, the USB (SIE) domain and the 8051-I/O Unit domain. This switching is done virtually instantaneously, giving essentially zero transfer time between "USB FIFOs" and "Slave FIFOs." Because they are physically the same memory, no bytes are actually transferred between buffers.

At any time, some RAM blocks are filling/emptying with the USB data under SIE control, while other RAM blocks are available to the 8051, the I/O control unit, or both. The RAM blocks operates as single-port in the USB domain, and dual-port in the 8051-I/O domain. The blocks can be configured as single-, double-, triple-, or quad-buffered as previously shown.

The I/O control unit implements either an internal master (M for Master) or external master (S for Slave) interface.

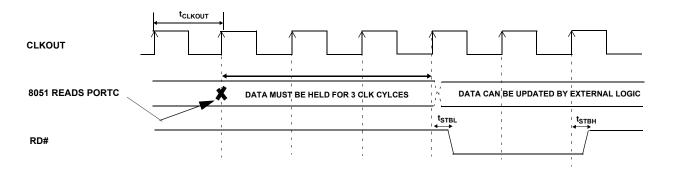

In Master (M) mode, the GPIF internally controls FIFOADR[1..0] to select a FIFO. The RDY pins (two in the 56-pin package, six in the 100-pin and 128-pin packages) can be used as flag inputs from an external FIFO or other logic if desired. The GPIF can be run from either an internally derived clock or externally supplied clock (IFCLK), at a rate that transfers data up to 96 MBytes/s (48 Hz IFCLK with 16-bit interface).

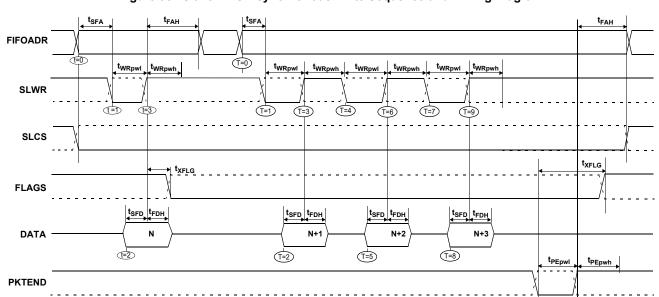

In the Slave (S) mode, FX2LP accepts either an internally derived clock or externally supplied clock (IFCLK, max frequency 48 MHz) and SLCS#, SLRD, SLWR, SLOE, PKTEND signals from external logic. When using an external IFCLK, the external clock must be present before switching to the external clock with the IFCLKSRC bit. Each endpoint can individually be selected for byte or word operation by an internal configuration bit and a Slave FIFO Output Enable signal (SLOE) that enables data of the selected width. External logic must ensure that the output enable signal is inactive when writing data to a slave FIFO. The slave interface can also operate asynchronously, where the SLRD and SLWR signals act directly as strobes, rather than a clock qualifier as in synchronous mode. The signals SLRD, SLWR, SLOE, and PKTEND are gated by the signal SLCS#.

#### GPIF and FIFO Clock Rates

An 8051 register bit selects one of two frequencies for the internally supplied interface clock: 30 MHz and 48 MHz.

Alternatively, an externally supplied clock of 5 MHz–48 MHz feeding the IFCLK pin can be used as the interface clock. IFCLK can be configured to function as an output clock when the GPIF and FIFOs are internally clocked. An output enable bit in the IFCONFIG register turns this clock output off, if desired. Another bit within the IFCONFIG register inverts the IFCLK signal whether internally or externally sourced.

#### **GPIF**

The GPIF is a flexible 8-bit or 16-bit parallel interface driven by a user-programmable finite state machine. It enables the CY7C68013A/15A to perform local bus mastering and can implement a wide variety of protocols such as ATA interface, printer parallel port, and Utopia.

The GPIF has six programmable control outputs (CTL), nine address outputs (GPIFADRx), and six general-purpose ready inputs (RDY). The data bus width can be 8 or 16 bits. Each GPIF vector defines the state of the control outputs, and determines what state a ready input (or multiple inputs) must be before proceeding. The GPIF vector can be programmed to advance a FIFO to the next data value, advance an address, etc. A sequence of the GPIF vectors make up a single waveform that is executed to perform the desired data move between the FX2LP and the external device.

#### Six Control OUT Signals

The 100-pin and 128-pin packages bring out all six Control Output pins (CTL0-CTL5). The 8051 programs the GPIF unit to define the CTL waveforms. The 56-pin package brings out three of these signals, CTL0-CTL2. CTLx waveform edges can be programmed to make transitions as fast as once per clock (20.8 ns using a 48-MHz clock).

## Six Ready IN Signals

The 100-pin and 128-pin packages bring out all six Ready inputs (RDY0–RDY5). The 8051 programs the GPIF unit to test the RDY pins for GPIF branching. The 56-pin package brings out two of these signals, RDY0–1.

#### Nine GPIF Address OUT Signals

Nine GPIF address lines are available in the 100-pin and 128-pin packages, GPIFADR[8..0]. The GPIF address lines enable indexing through up to a 512-byte block of RAM. If more address lines are needed, then I/O port pins are used.

#### Long Transfer Mode

In the master mode, the 8051 appropriately sets GPIF transaction count registers (GPIFTCB3, GPIFTCB2, GPIFTCB1, or GPIFTCB0) for unattended transfers of up to  $2^{32}$  transactions. The GPIF automatically throttles data flow to prevent under or overflow until the full number of requested transactions complete. The GPIF decrements the value in these registers to represent the current status of the transaction.

Document Number: 38-08032 Rev. AC Page 15 of 75

#### **ECC Generation**

The EZ-USB can calculate ECCs (Error Correcting Codes)<sup>[10]</sup> on data that passes across its GPIF or Slave FIFO interfaces. There are two ECC configurations: Two ECCs, each calculated over 256 bytes (SmartMedia Standard); and one ECC calculated over 512 bytes.

The ECC can correct any one-bit error or detect any two-bit error.

#### ECC Implementation

The two ECC configurations are selected by the ECCM bit:

#### ECCM = 0

Two 3-byte ECCs, each calculated over a 256-byte block of data. This configuration conforms to the SmartMedia Standard.

Write any value to ECCRESET, then pass data across the GPIF or Slave FIFO interface. The ECC for the first 256 bytes of data is calculated and stored in ECC1. The ECC for the next 256 bytes is stored in ECC2. After the second ECC is calculated, the values in the ECCx registers do not change until ECCRESET is written again, even if more data is subsequently passed across the interface.

#### ECCM = 1

One 3-byte ECC calculated over a 512-byte block of data.

Write any value to ECCRESET then pass data across the GPIF or Slave FIFO interface. The ECC for the first 512 bytes of data is calculated and stored in ECC1; ECC2 is unused. After the ECC is calculated, the values in ECC1 do not change even if more data is subsequently passed across the interface, till ECCRESET is written again.

#### **USB Uploads and Downloads**

The core has the ability to directly edit the data contents of the internal 16-KB RAM and of the internal 512-byte scratch pad RAM via a vendor-specific command. This capability is normally used when soft downloading the user code and is available only to and from the internal RAM, only when the 8051 is held in reset. The available RAM spaces are 16 KB from 0x0000–0x3FFF (code/data) and 512 bytes from 0xE000–0xE1FF (scratch pad data RAM)<sup>[11]</sup>.

## **Autopointer Access**

FX2LP provides two identical autopointers. They are similar to the internal 8051 data pointers but with an additional feature: they can optionally increment after every memory access. This capability is available to and from both internal and external RAM. Autopointers are available in external FX2LP registers

under the control of a mode bit (AUTOPTRSET-UP.0). Using the external FX2LP autopointer access (at 0xE67B–0xE67C) enables the autopointer to access all internal and external RAM to the part.

Also, autopointers can point to any FX2LP register or endpoint buffer space. When the autopointer access to external memory is enabled, locations 0xE67B and 0xE67C in XDATA and code space cannot be used.

#### I<sup>2</sup>C Controller

FX2LP has one I<sup>2</sup>C port that is driven by two internal controllers, the one that automatically operates at boot time to load VID/PID/DID and configuration information, and another that the 8051 uses when running to control external I<sup>2</sup>C devices. The I<sup>2</sup>C port operates in master mode only.

#### <sup>2</sup>C Port Pins

The  $I^2$ C pins SCL and SDA must have external 2.2-k $\Omega$  pull-up resistors even if no EEPROM is connected to the FX2LP. External EEPROM device address pins must be configured properly. See Table 8 for configuring the device address pins.

Table 8. Strap Boot EEPROM Address Lines to These Values

| Bytes | Example EEPROM         | A2  | <b>A</b> 1 | A0  |

|-------|------------------------|-----|------------|-----|

| 16    | 24LC00 <sup>[12]</sup> | N/A | N/A        | N/A |

| 128   | 24LC01                 | 0   | 0          | 0   |

| 256   | 24LC02                 | 0   | 0          | 0   |

| 4K    | 24LC32                 | 0   | 0          | 1   |

| 8K    | 24LC64                 | 0   | 0          | 1   |

| 16K   | 24LC128                | 0   | 0          | 1   |

#### PC Interface Boot Load Access

At power-on reset, the  $I^2C$  interface boot loader loads the VID/PID/DID configuration bytes and up to 16 KB of program/data. The available RAM spaces are 16 KB from 0x0000–0x3FFF and 512 bytes from 0xE000–0xE1FF. The 8051 is in reset.  $I^2C$  interface boot loads only occur after power-on reset.

#### PC Interface General-Purpose Access

The 8051 can control peripherals connected to the I<sup>2</sup>C bus using the I2CTL and I2DAT registers. FX2LP provides I<sup>2</sup>C master control only; it is never an I<sup>2</sup>C slave.

#### Notes

- 10. To use the ECC logic, the GPIF or Slave FIFO interface must be configured for byte-wide operation.

- 11. After the data is downloaded from the host, a "loader" can execute from internal RAM to transfer downloaded data to external memory.

12. This EEPROM does not have address pins.

#### Compatible with Previous Generation EZ-USB FX2

The EZ-USB FX2LP is form-, fit-, and with minor exceptions, functionally-compatible with its predecessor, the EZ-USB FX2. This makes for an easy transition for designers wanting to upgrade their systems from the FX2 to the FX2LP. The pinout and package selection are identical and a vast majority of firmware previously developed for the FX2 functions in the FX2LP.

For designers migrating from the FX2 to the FX2LP, a change in the bill of material and review of the memory allocation (due to increased internal memory) is required. For more information about migrating from EZ-USB FX2 to EZ-USB FX2LP, see the application note titled *Migrating from EZ-USB FX2 to EZ-USB FX2LP* available in the Cypress web site.

**Table 9. Part Number Conversion Table**

| EZ-USB FX2<br>Part Number | EZ-USB FX2LP<br>Part Number                 | Package<br>Description               |

|---------------------------|---------------------------------------------|--------------------------------------|

| CY7C68013-56PVC           | CY7C68013A-56PVXC or<br>CY7C68014A-56PVXC   | 56-pin<br>SSOP                       |

| CY7C68013-56PVCT          | CY7C68013A-56PVXCT or<br>CY7C68014A-56PVXCT | 56-pin<br>SSOP –<br>Tape and<br>Reel |

| CY7C68013-56LFC           | CY7C68013A-56LFXC or<br>CY7C68014A-56LFXC   | 56-pin QFN                           |

| CY7C68013-100AC           | CY7C68013A-100AXC or<br>CY7C68014A-100AXC   | 100-pin<br>TQFP                      |

| CY7C68013-128AC           | CY7C68013A-128AXC or<br>CY7C68014A-128AXC   | 128-pin<br>TQFP                      |

#### CY7C68013A/14A and CY7C68015A/16A Differences

CY7C68013A is identical to CY7C68014A in form, fit, and functionality. CY7C68015A is identical to CY7C68016A in form, fit, and functionality. CY7C68014A and CY7C68016A have a lower suspend current than CY7C68013A and CY7C68015A respectively and are ideal for power-sensitive battery applications.

CY7C68015A and CY7C68016A are available in 56-pin QFN package only. Two additional GPIO signals are available on the CY7C68015A and CY7C68016A to provide more flexibility when neither IFCLK or CLKOUT are needed in the 56-pin package.

USB developers wanting to convert their FX2 56-pin application to a bus-powered system directly benefit from these additional signals. The two GPIOs give developers the signals they need for the power-control circuitry of their bus-powered application without pushing them to a high-pincount version of FX2LP.

The CY7C68015A is only available in the 56-pin QFN package

Table 10. CY7C68013A/14A and CY7C68015A/16A Pin Differences

| CY7C68013A/CY7C68014A | CY7C68015A/CY7C68016A |

|-----------------------|-----------------------|

| IFCLK                 | PE0                   |

| CLKOUT                | PE1                   |

Document Number: 38-08032 Rev. AC Page 17 of 75

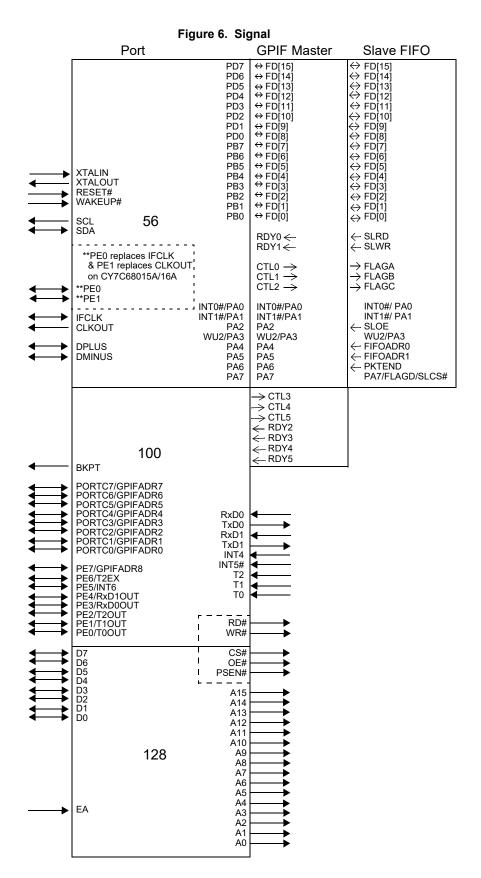

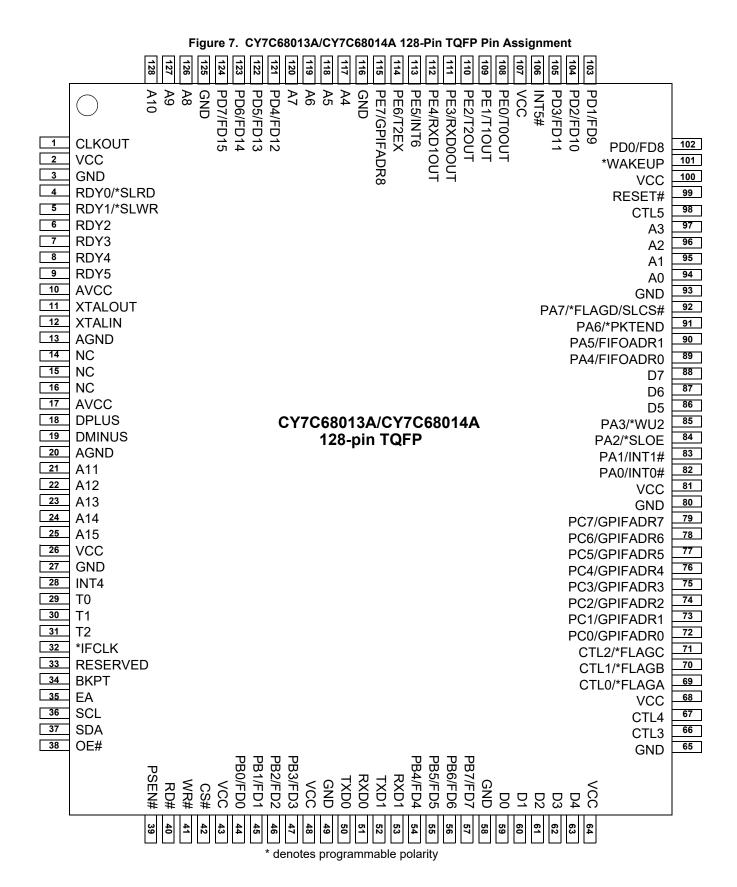

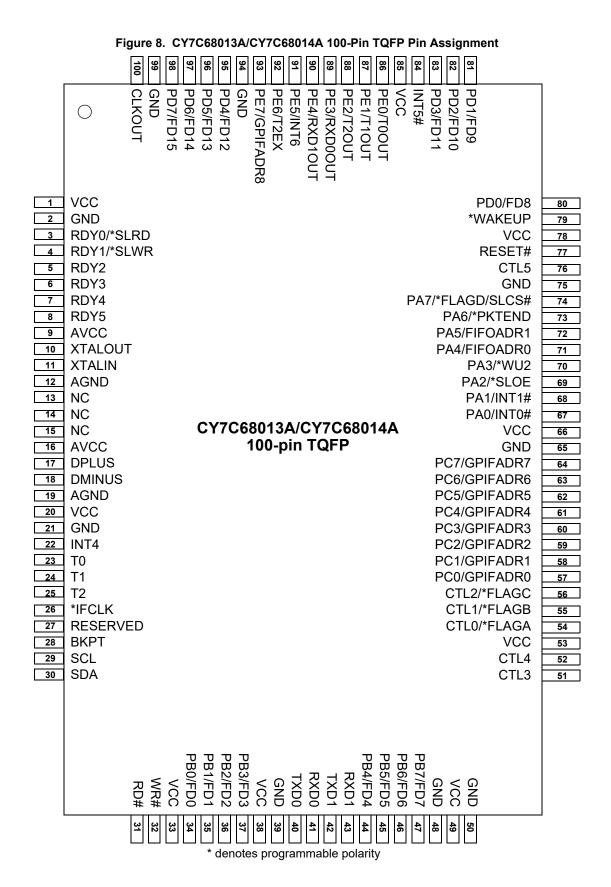

## **Pin Assignments**

Figure 6 on page 19 identifies all signals for the five package types. The following pages illustrate the individual pin diagrams, plus a combination diagram showing which of the full set of signals are available in the 128-pin, 100-pin, and 56-pin packages.

The signals on the left edge of the 56-pin package in Figure 6 on page 19 are common to all versions in the FX2LP family with the noted differences between the CY7C68013A/14A and the CY7C68015A/16A.

Three modes are available in all package versions: Port, GPIF master, and Slave FIFO. These modes define the signals on the right edge of the diagram. The 8051 selects the interface mode using the IFCONFIG[1:0] register bits. Port mode is the power on default configuration.

The 100-pin package adds functionality to the 56-pin package by adding these pins:

- PORTC or alternate GPIFADR[7:0] address signals

- PORTE or alternate GPIFADR[8] address signal and seven additional 8051 signals

- Three GPIF Control signals

- Four GPIF Ready signals

- Nine 8051 signals (two USARTs, three timer inputs, INT4, and INT5#)

- BKPT, RD#, WR#.

The 128-pin package adds the 8051 address and data buses plus control signals. Note that two of the required signals, RD# and WR#, are present in the 100-pin version.

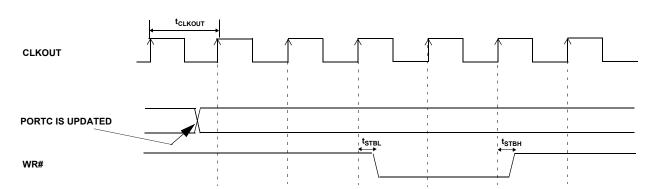

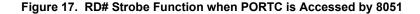

In the 100-pin and 128-pin versions, an 8051 control bit can be set to pulse the RD# and WR# pins when the 8051 reads from/writes to PORTC. This feature is enabled by setting the PORTCSTB bit in the CPUCS register.

PORTC Strobe Feature Timings on page 46 displays the timing diagram of the read and write strobing function on accessing PORTC.

Document Number: 38-08032 Rev. AC Page 18 of 75

Document Number: 38-08032 Rev. AC Page 19 of 75

Document Number: 38-08032 Rev. AC Page 20 of 75

Document Number: 38-08032 Rev. AC Page 21 of 75

Figure 9. CY7C68013A/CY7C68014A 56-Pin SSOP Pin Assignment

## CY7C68013A/CY7C68014A 56-pin SSOP

|    | Q          |                  |    |

|----|------------|------------------|----|

| 1  | PD5/FD13   | PD4/FD12         | 56 |

| 2  | PD6/FD14   | PD3/FD11         | 55 |

| 3  | PD7/FD15   | PD2/FD10         | 54 |

| 4  | GND        | PD1/FD9          | 53 |

| 5  | CLKOUT     | PD0/FD8          | 52 |

| 6  | VCC        | *WAKEUP          | 51 |

| 7  | GND        | VCC              | 50 |

| 8  | RDY0/*SLRD | RESET#           | 49 |

| 9  | RDY1/*SLWR | GND              | 48 |

| 10 | AVCC       | PA7/*FLAGD/SLCS# | 47 |

| 11 | XTALOUT    | PA6/PKTEND       | 46 |

| 12 | XTALIN     | PA5/FIFOADR1     | 45 |

| 13 | AGND       | PA4/FIFOADR0     | 44 |

| 14 | AVCC       | PA3/*WU2         | 43 |

| 15 | DPLUS      | PA2/*SLOE        | 42 |

| 16 | DMINUS     | PA1/INT1#        | 41 |

| 17 | AGND       | PA0/INT0#        | 40 |

| 18 | VCC        | VCC              | 39 |

| 19 | GND        | CTL2/*FLAGC      | 38 |

| 20 | *IFCLK     | CTL1/*FLAGB      | 37 |

| 21 | RESERVED   | CTL0/*FLAGA      | 36 |

| 22 | SCL        | GND              | 35 |

| 23 | SDA        | VCC              | 34 |

| 24 | VCC        | GND              | 33 |

| 25 | PB0/FD0    | PB7/FD7          | 32 |

| 26 | PB1/FD1    | PB6/FD6          | 31 |

| 27 | PB2/FD2    | PB5/FD5          | 30 |

| 28 | PB3/FD3    | PB4/FD4          | 29 |

|    |            |                  |    |

<sup>\*</sup> denotes programmable polarity

Document Number: 38-08032 Rev. AC Page 22 of 75

CLKOUT/\*\*PE1 PD7/FD15 PD4/FD12 PD3/FD11 PD2/FD10 \*WAKEUP PD0/FD8 GND VCC VCC 46 RDY0/\*SLRD RESET# RDY1/\*SLWR 41 **GND AVCC** PA7/\*FLAGD/SLCS# 40 3 **XTALOUT** 4 39 PA6/\*PKTEND CY7C68013A/CY7C68014A **XTALIN** PA5/FIFOADR1 38 PA4/FIFOADR0 **AGND** 6 CY7C68015A/CY7C68016A PA3/\*WU2 **AVCC** 36 56-pin QFN **DPLUS** PA2/\*SLOE 8 35 **DMINUS** 9 34 PA1/INT1# **AGND** PA0/INT0# 10 VCC **VCC** 11 **GND** 31 CTL2/\*FLAGC 12 \*IFCLK/\*\*PE0 CTL1/\*FLAGB 30 13 CTL0/\*FLAGA **RESERVED** VCC PB0/FD0 PB1/FD1 PB2/FD2 PB3/FD3 PB4/FD<sub>2</sub> PB5/FD5 PB6/FD6

Figure 10. CY7C68013A/14A/15A/16A 56-Pin QFN Pin Assignment

\* denotes programmable polarity

\*\* denotes CY7C68015A/CY7C68016A pinout

Document Number: 38-08032 Rev. AC Page 23 of 75

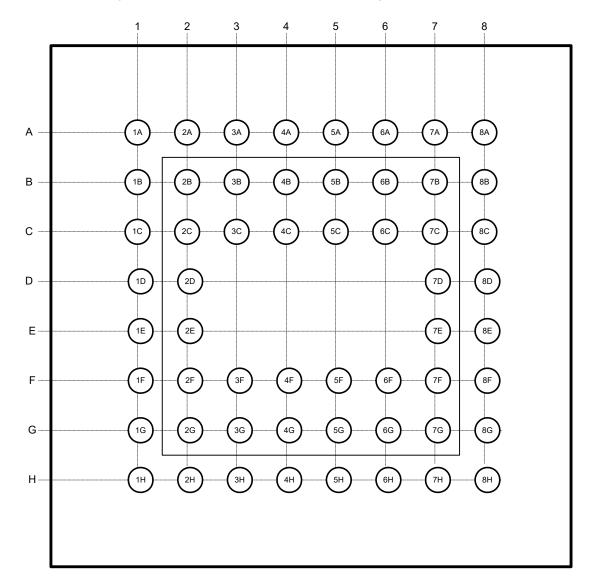

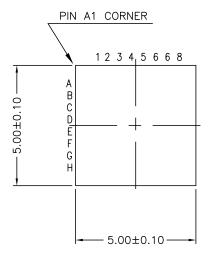

Figure 11. CY7C68013A 56-pin VFBGA Pin Assignment - Top View

Document Number: 38-08032 Rev. AC

## CY7C68013A/15A Pin Descriptions

Table 11. FX2LP Pin Descriptions<sup>[13]</sup>

| 128  | 100 | 56   | 56 | 56    |        |        |         | _                     | _                                                                                                                                                                                                                            |  |  |  |  |  |

|------|-----|------|----|-------|--------|--------|---------|-----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| TQFP |     | SSOP |    | VFBGA | Name   | Type   | Default | Reset <sup>[14]</sup> | Description                                                                                                                                                                                                                  |  |  |  |  |  |

| 10   | 9   | 10   | 3  | 2D    | AVCC   | Power  | N/A     | N/A                   | <b>Analog VCC</b> . Connect this pin to the 3.3 V power source. This signal provides power to the analog section of the chip.                                                                                                |  |  |  |  |  |

| 17   | 16  | 14   | 7  | 1D    | AVCC   | Power  | N/A     | N/A                   | <b>Analog VCC</b> . Connect this pin to the 3.3 V power source. This signal provides power to the analog section of the chip.                                                                                                |  |  |  |  |  |

| 13   | 12  | 13   | 6  | 2F    | AGND   | Ground | N/A     | N/A                   | Analog Ground. Connect to ground with as she a path as possible.                                                                                                                                                             |  |  |  |  |  |

| 20   | 19  | 17   | 10 | 1F    | AGND   | Ground | N/A     | N/A                   | <b>Analog Ground</b> . Connect to ground with as short a path as possible.                                                                                                                                                   |  |  |  |  |  |

| 19   | 18  | 16   | 9  | 1E    | DMINUS | I/O/Z  | Z       | N/A                   | USB D- Signal. Connect to the USB D- signal.                                                                                                                                                                                 |  |  |  |  |  |

| 18   | 17  | 15   | 8  | 2E    | DPLUS  | I/O/Z  | Z       | N/A                   | USB D+ Signal. Connect to the USB D+ signal.                                                                                                                                                                                 |  |  |  |  |  |

| 94   | 1   | _    | _  | _     | A0     | Output | L       | L                     |                                                                                                                                                                                                                              |  |  |  |  |  |

| 95   |     | _    | _  | _     | A1     | Output | L       | L                     |                                                                                                                                                                                                                              |  |  |  |  |  |

| 96   |     | _    | _  | _     | A2     | Output | L       | L                     |                                                                                                                                                                                                                              |  |  |  |  |  |

| 97   |     | _    | _  | _     | A3     | Output | L       | L                     |                                                                                                                                                                                                                              |  |  |  |  |  |

| 117  |     | _    | _  | _     | A4     | Output | L       | L                     |                                                                                                                                                                                                                              |  |  |  |  |  |

| 118  |     | _    | _  | _     | A5     | Output | L       | L                     |                                                                                                                                                                                                                              |  |  |  |  |  |

| 119  | _   | _    | _  | _     | A6     | Output | L       | L                     |                                                                                                                                                                                                                              |  |  |  |  |  |

| 120  | _   | _    | _  | _     | A7     | Output | L       | L                     | <b>8051 Address Bus</b> . This bus is driven at all times. When the 8051 is addressing internal RAM it                                                                                                                       |  |  |  |  |  |

| 126  | _   | _    | _  | _     | A8     | Output | L       | L                     | reflects the internal address.                                                                                                                                                                                               |  |  |  |  |  |

| 127  | _   | _    | _  | _     | A9     | Output | L       | L                     |                                                                                                                                                                                                                              |  |  |  |  |  |

| 128  | _   | _    | _  | _     | A10    | Output | L       | L                     |                                                                                                                                                                                                                              |  |  |  |  |  |

| 21   | _   | _    | _  | _     | A11    | Output | L       | L                     |                                                                                                                                                                                                                              |  |  |  |  |  |

| 22   | _   | _    | _  | _     | A12    | Output | L       | L                     |                                                                                                                                                                                                                              |  |  |  |  |  |

| 23   | _   | _    | _  | _     | A13    | Output | L       | L                     |                                                                                                                                                                                                                              |  |  |  |  |  |

| 24   | _   | _    | _  | _     | A14    | Output | L       | L                     |                                                                                                                                                                                                                              |  |  |  |  |  |

| 25   | ı   | _    | _  | _     | A15    | Output | L       | L                     |                                                                                                                                                                                                                              |  |  |  |  |  |

| 59   | ı   | _    | _  | _     | D0     | I/O/Z  | Z       | Z                     |                                                                                                                                                                                                                              |  |  |  |  |  |

| 60   | ı   | _    | _  | _     | D1     | I/O/Z  | Z       | Z                     | 0054 B.4. B This his are the sign of                                                                                                                                                                                         |  |  |  |  |  |

| 61   | ı   | _    | _  | _     | D2     | I/O/Z  | Z       | Z                     | <b>8051 Data Bus</b> . This bidirectional bus is high impedance when inactive, input for bus reads,                                                                                                                          |  |  |  |  |  |

| 62   | _   | _    | _  | _     | D3     | I/O/Z  | Z       | Z                     | and output for bus writes. The data bus is used for                                                                                                                                                                          |  |  |  |  |  |

| 63   | _   | _    | _  | _     | D4     | I/O/Z  | Z       | Z                     | external 8051 program and data memory. The data<br>bus is active only for external bus accesses, and is                                                                                                                      |  |  |  |  |  |

| 86   |     | _    |    |       | D5     | I/O/Z  | Z       | Z                     | driven LOW in suspend.                                                                                                                                                                                                       |  |  |  |  |  |

| 87   |     |      |    |       | D6     | I/O/Z  | Z       | Z                     | · ·                                                                                                                                                                                                                          |  |  |  |  |  |

| 88   |     |      | _  |       | D7     | I/O/Z  | Z       | Z                     |                                                                                                                                                                                                                              |  |  |  |  |  |