### FEATURES

- Wide Operating Voltage Range: 2.5V to 34V

- Overvoltage Protection to 60V

- Reverse Supply Protection to –40V

- LTC4365: Blocks 50Hz and 60Hz AC Power

- LTC4365-1: Fast (1ms) Recovery from Fault

- No Input Capacitor or TVS Required for Most Applications

- Adjustable Undervoltage and Overvoltage Protection Range

- Charge Pump Enhances External N-Channel MOSFET

- Low Operating Current: 125µA

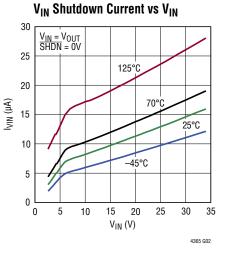

- Low Shutdown Current: 10µA

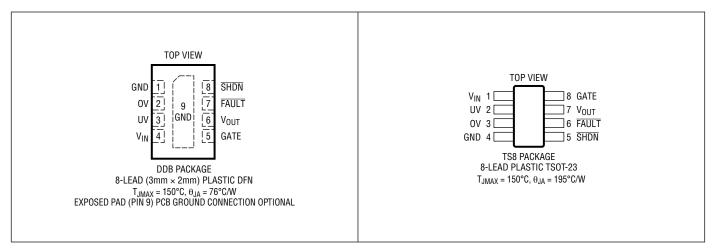

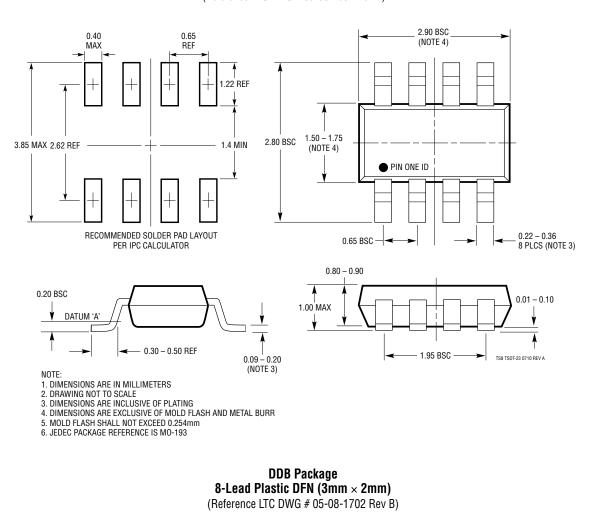

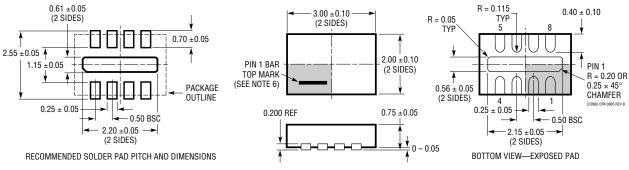

- Compact 8-Lead, 3mm × 2mm DFN and TSOT-23 (ThinSOT™) Packages

- AEC-Q100 Qualified for Automotive Applications

#### **APPLICATIONS**

- Portable Instrumentation

- Industrial Automation

- Laptops

- Automotive Surge Protection

### Overvoltage, Undervoltage and Reverse Supply Protection Controller **DESCRIPTION**

The LTC<sup>®</sup>4365 protects applications where power supply input voltages may be too high, too low or even negative. It does this by controlling the gate voltages of a pair of external N-channel MOSFETs to ensure that the output stays within a safe operating range.The LTC4365 can withstand voltages between -40V and 60V and has an operating range of 2.5V to 34V, while consuming only 125µA in normal operation.

Two comparator inputs allow configuration of the overvoltage (OV) and undervoltage (UV) set points using an external resistive divider. A shutdown pin provides external control for enabling and disabling the MOSFETs as well as placing the device in a low current shutdown state. A fault output provides status of the gate pin pulling low. A fault is indicated when the part is in shutdown or the input voltage is outside the UV and OV set points.

The LTC4365 has a 36ms turn-on delay that debounces live connections and blocks 50Hz to 60Hz AC power. For fast recovery after faults, the LTC4365-1 has a reduced 1ms turn-on delay.

All registered trademarks and trademarks are the property of their respective owners. Protected by U.S. patents, including XXXXX, XXXXX.

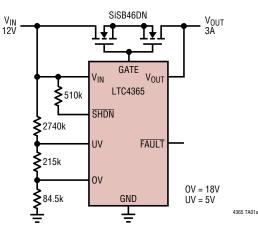

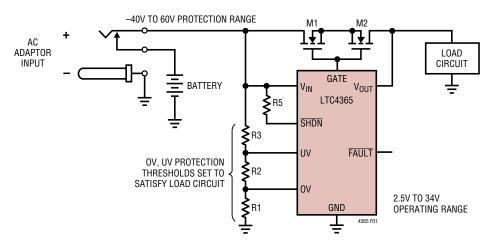

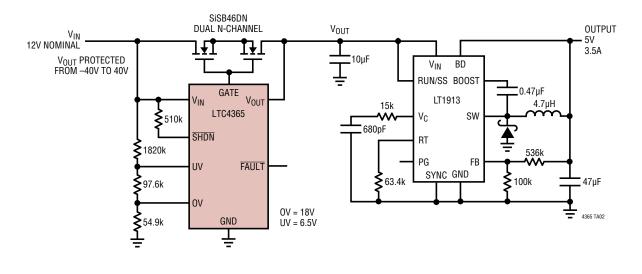

#### TYPICAL APPLICATION

#### **12V Automotive Application**

#### Load Protected from Reverse and Overvoltage at $\mathbf{V}_{\text{IN}}$

Rev. B

# **ABSOLUTE MAXIMUM RATINGS**

| Supply Voltage (Note 1)  |             |

|--------------------------|-------------|

| V <sub>IN</sub>          | 40V to 60V  |

| Input Voltages (Note 3)  |             |

| UV, <u>SHDN</u>          |             |

| 0V                       |             |

| V <sub>OUT</sub>         | 0.3V to 40V |

| Output Voltages (Note 4) |             |

| FAULT                    | 0.3V to 60V |

| GATE                     | 40V to 45V  |

|                          |             |

| Input Currents                       |                 |

|--------------------------------------|-----------------|

| UV, OV, <u>SHDN</u>                  | –1mA            |

| Operating Ambient Temperature Range  |                 |

| LTC4365C                             | 0°C to 70°C     |

| LTC43651                             | –40°C to 85°C   |

| LTC4365H                             | .–40°C to 125°C |

| Storage Temperature Range            | .–65°C to 150°C |

| Lead Temperature (Soldering, 10 sec) |                 |

| for TSOT Only                        | 300°C           |

### PIN CONFIGURATION

# ORDER INFORMATION

| TAPE AND REEL (MINI) | TAPE AND REEL       | PART MARKING* | PACKAGE DESCRIPTION            | TEMPERATURE RANGE |

|----------------------|---------------------|---------------|--------------------------------|-------------------|

| LTC4365CDDB#TRMPBF   | LTC4365CDDB#TRPBF   | LFKS          | 8-Lead (3mm × 2mm) Plastic DFN | 0°C to 70°C       |

| LTC4365CDDB-1#TRMPBF | LTC4365CDDB-1#TRPBF | LGMB          | 8-Lead (3mm × 2mm) Plastic DFN | 0°C to 70°C       |

| LTC4365IDDB#TRMPBF   | LTC4365IDDB#TRPBF   | LFKS          | 8-Lead (3mm × 2mm) Plastic DFN | -40°C to 85°C     |

| LTC4365IDDB-1#TRMPBF | LTC4365IDDB-1#TRPBF | LGMB          | 8-Lead (3mm × 2mm) Plastic DFN | -40°C to 85°C     |

| LTC4365HDDB#TRMPBF   | LTC4365HDDB#TRPBF   | LFKS          | 8-Lead (3mm × 2mm) Plastic DFN | -40°C to 125°C    |

| LTC4365HDDB-1#TRMPBF | LTC4365HDDB-1#TRPBF | LGMB          | 8-Lead (3mm × 2mm) Plastic DFN | -40°C to 125°C    |

| LTC4365CTS8#TRMPBF   | LTC4365CTS8#TRPBF   | LTFKT         | 8-Lead Plastic TSOT-23         | 0°C to 70°C       |

| LTC4365CTS8-1#TRMPBF | LTC4365CTS8-1#TRPBF | LTGKZ         | 8-Lead Plastic TSOT-23         | 0°C to 70°C       |

| LTC4365ITS8#TRMPBF   | LTC4365ITS8#TRPBF   | LTFKT         | 8-Lead Plastic TSOT-23         | -40°C to 85°C     |

| LTC4365ITS8-1#TRMPBF | LTC4365ITS8-1#TRPBF | LTGKZ         | 8-Lead Plastic TSOT-23         | -40°C to 85°C     |

| LTC4365HTS8#TRMPBF   | LTC4365HTS8#TRPBF   | LTFKT         | 8-Lead Plastic TSOT-23         | -40°C to 125°C    |

| LTC4365HTS8-1#TRMPBF | LTC4365HTS8-1#TRPBF | LTGKZ         | 8-Lead Plastic TSOT-23         | -40°C to 125°C    |

|                      |                     |               |                                | Re                |

# **ORDER INFORMATION**

#### Lead Free Finish

#### **AUTOMOTIVE PRODUCTS\*\***

| TAPE AND REEL (MINI)  | TAPE AND REEL        | PART MARKING* | PACKAGE DESCRIPTION    | TEMPERATURE RANGE |

|-----------------------|----------------------|---------------|------------------------|-------------------|

| LTC4365ITS8#WTRMPBF   | LTC4365ITS8#WTRPBF   | LTFKT         | 8-Lead Plastic TSOT-23 | -40°C to 85°C     |

| LTC4365ITS8-1#WTRMPBF | LTC4365ITS8-1#WTRPBF | LTGKZ         | 8-Lead Plastic TSOT-23 | -40°C to 85°C     |

| LTC4365HTS8#WTRMPBF   | LTC4365HTS8#WTRPBF   | LTFKT         | 8-Lead Plastic TSOT-23 | -40°C to 125°C    |

| LTC4365HTS8-1#WTRMPBF | LTC4365HTS8-1#WTRPBF | LTGKZ         | 8-Lead Plastic TSOT-23 | -40°C to 125°C    |

Contact the factory for parts specified with wider operating temperature ranges. \*The temperature grade is identified by a label on the shipping container.

Tape and reel specifications. Some packages are available in 500 unit reels through designated sales channels with #TRMPBF suffix.

\*\*Versions of this part are available with controlled manufacturing to support the quality and reliability requirements of automotive applications. These models are designated with a #W suffix. Only the automotive grade products shown are available for use in automotive applications. Contact your local Analog Devices account representative for specific product ordering information and to obtain the specific Automotive Reliability reports for these models.

**ELECTRICAL CHARACTERISTICS** The  $\bullet$  denotes the specifications which apply over the full operating temperature range, otherwise specifications are at T<sub>A</sub> = 25°C. V<sub>IN</sub> = 2.5V to 34V, unless otherwise noted. (Note 2)

| SYMBOL                             | PARAMETER                                        | CONDITIONS                                                                                                                                                                                                                      |   | MIN        | ТҮР            | MAX              | UNITS          |

|------------------------------------|--------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|------------|----------------|------------------|----------------|

| V <sub>IN</sub> , V <sub>OUT</sub> |                                                  |                                                                                                                                                                                                                                 |   | •          |                |                  | <u>.</u>       |

| V <sub>IN</sub>                    | Input Voltage Range                              | Operating Range<br>Protection Range                                                                                                                                                                                             | • | 2.5<br>-40 |                | 34<br>60         | V<br>V         |

| I <sub>VIN</sub>                   | Input Supply Current                             | $\label{eq:shdn} \begin{array}{ c c } \hline \hline SHDN = 0V, \ V_{IN} = V_{OUT}, \ -40^\circ C \ to \ 85^\circ C \\ \hline SHDN = 0V, \ V_{IN} = V_{OUT}, \ -40^\circ C \ to \ 125^\circ C \\ \hline SHDN = 2.5V \end{array}$ | • |            | 10<br>10<br>25 | 50<br>100<br>150 | μΑ<br>μΑ<br>μΑ |

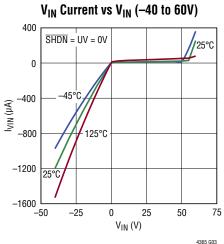

| I <sub>VIN(R)</sub>                | Reverse Input Supply Current                     | $V_{IN} = -40V, V_{OUT} = 0V$                                                                                                                                                                                                   | ٠ |            | -1.2           | -1.8             | mA             |

| V <sub>IN(UVLO)</sub>              | Input Supply Undervoltage Lockout                | V <sub>IN</sub> Rising                                                                                                                                                                                                          | ٠ | 1.8        | 2.2            | 2.4              | V              |

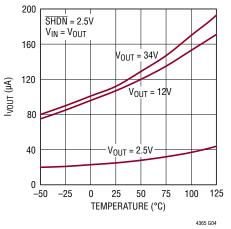

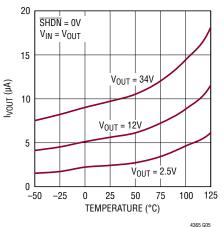

| I <sub>VOUT</sub>                  | V <sub>OUT</sub> Input Current                   | $\label{eq:shdd} \begin{array}{ c c } \hline \hline SHDN = 0V, V_{IN} = V_{OUT} \\ \hline SHDN = 2.5V, V_{IN} = V_{OUT} \\ \hline V_{IN} = -40V, V_{OUT} = 0V \end{array}$                                                      | • |            | 6<br>100<br>20 | 30<br>250<br>50  | μΑ<br>μΑ<br>μΑ |

| GATE                               |                                                  | ·                                                                                                                                                                                                                               |   |            |                |                  | <u>.</u>       |

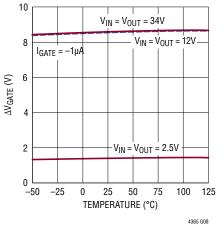

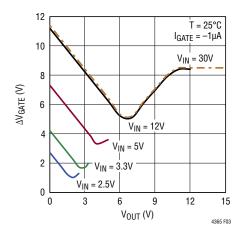

| $\Delta V_{GATE}$                  | N-Channel Gate Drive<br>(GATE-V <sub>OUT</sub> ) | $V_{IN} = V_{OUT} = 5.0V$ , $I_{GATE} = -1\mu A$<br>$V_{IN} = V_{OUT} = 12V$ to 34V, $I_{GATE} = -1\mu A$                                                                                                                       | • | 3<br>7.4   | 3.6<br>8.4     | 4.2<br>9.8       | V<br>V         |

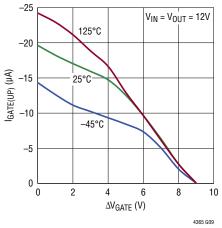

| I <sub>GATE(UP)</sub>              | N-Channel Gate Pull Up Current                   | $GATE = V_{IN} = V_{OUT} = 12V$                                                                                                                                                                                                 | ٠ | -12        | -20            | -30              | μA             |

| I <sub>GATE(FAST)</sub>            | N-Channel Gate Fast Pull Down Current            | Fast Shutdown, GATE = 20V, $V_{IN} = V_{OUT} = 12V$                                                                                                                                                                             | • | 31         | 50             | 72               | mA             |

| I <sub>GATE(SLOW)</sub>            | N-Channel Gate Gentle Pull Down Current          | Gentle Shutdown, GATE = 20V, V <sub>IN</sub> = V <sub>OUT</sub> = 12V                                                                                                                                                           | ٠ | 50         | 90             | 150              | μA             |

| t <sub>GATE(FAST)</sub>            | N-Channel Gate Fast Turn Off Delay               | C <sub>GATE</sub> = 2.2nF, UV or OV Fault                                                                                                                                                                                       | ٠ |            | 2              | 4                | μs             |

| t <sub>GATE(SLOW)</sub>            | N-Channel Gentle Turn Off Delay                  | $C_{GATE} = 2.2nF, \overline{SHDN}$ Falling, $V_{IN} = V_{OUT} = 12V$                                                                                                                                                           | ٠ | 150        | 250            | 350              | μs             |

| t <sub>RECOVERY</sub>              | GATE Recovery Delay Time                         | $V_{\text{IN}}$ = 12V, Power Good to $\Delta V_{\text{GATE}}$ > 0V LTC4365, $C_{\text{GATE}}$ = 2.2nF LTC4365-1, $C_{\text{GATE}}$ = 2.2nF                                                                                      | • | 26<br>0.6  | 36<br>1        | 49<br>1.5        | ms<br>ms       |

**ELECTRICAL CHARACTERISTICS** The  $\bullet$  denotes the specifications which apply over the full operating temperature range, otherwise specifications are at T<sub>A</sub> = 25°C. V<sub>IN</sub> = 2.5V to 34V, unless otherwise noted. (Note 2)

| SYMBOL               | PARAMETER                                  | CONDITIONS                                                                                                                 |   | MIN       | ТҮР       | MAX     | UNITS    |

|----------------------|--------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|---|-----------|-----------|---------|----------|

| UV, OV               |                                            |                                                                                                                            |   |           |           |         | ·        |

| V <sub>UV</sub>      | UV Input Threshold Voltage                 | UV Falling $\rightarrow \Delta V_{GATE} = 0V$                                                                              |   | 492.5     | 500       | 507.5   | mV       |

| V <sub>OV</sub>      | OV Input Threshold Voltage                 | OV Rising $\rightarrow \Delta V_{GATE} = 0V$                                                                               | • | 492.5     | 500       | 507.5   | mV       |

| VUVHYST              | UV Input Hysteresis                        |                                                                                                                            | • | 20        | 25        | 32      | mV       |

| V <sub>OVHYST</sub>  | OV Input Hysteresis                        |                                                                                                                            | • | 20        | 25        | 32      | mV       |

| I <sub>LEAK</sub>    | UV, OV Leakage Current                     | $V = 0.5V, V_{IN} = 34V$                                                                                                   | • |           |           | ±10     | nA       |

| t <sub>FAULT</sub>   | UV, OV Fault Propagation Delay             | $\begin{array}{l} \text{Overdrive} = 50\text{mV} \\ \text{V}_{\text{IN}} = \text{V}_{\text{OUT}} = 12\text{V} \end{array}$ | • |           | 1         | 2       | μs       |

| SHDN                 |                                            |                                                                                                                            |   |           |           |         | ·        |

| V <sub>SHDN</sub>    | SHDN Input Threshold                       | SHDN Falling to $\Delta V_{GATE} = 0V$                                                                                     |   | 0.4       | 0.75      | 1.2     | V        |

| I <sub>SHDN</sub>    | SHDN Input Current                         | <del>SHDN</del> = 0.75V, V <sub>IN</sub> = 34V                                                                             | • |           |           | ±10     | nA       |

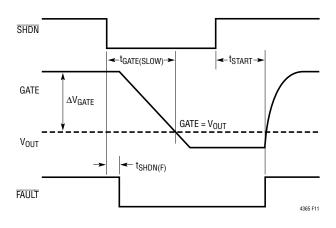

| t <sub>START</sub>   | Delay Coming Out of Shutdown Mode          | $\overline{\text{SHDN}}$ Rising to $\Delta V_{\text{GATE}} > 0V$ , $V_{\text{IN}} = V_{\text{OUT}} = 12V$                  | • | 400       | 800       | 1200    | μs       |

| t <sub>SHDN(F)</sub> | SHDN to FAULT Asserted                     | $V_{IN} = V_{OUT} = 12V$                                                                                                   | • |           | 1.5       | 3       | μs       |

| t <sub>lowpwr</sub>  | Delay from Turn Off to Low Power Operation | V <sub>IN</sub> = V <sub>OUT</sub> = 12V<br>LTC4365<br>LTC4365-1                                                           | • | 26<br>0.3 | 36<br>0.7 | 55<br>2 | ms<br>ms |

| FAULT                | ·                                          |                                                                                                                            |   |           |           |         | <u> </u> |

| V <sub>OL</sub>      | FAULT Output Voltage Low                   | I <sub>FAULT</sub> = 500μA                                                                                                 |   |           | 0.15      | 0.4     | V        |

| I <sub>FAULT</sub>   | FAULT Leakage Current                      | $\overline{FAULT} = 5V, V_{IN} = 34V$                                                                                      | • |           |           | ±20     | nA       |

Note 1. Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. Exposure to any Absolute Maximum Rating condition for extended periods may affect device reliability and lifetime.

Note 3. These pins can be tied to voltages below -0.3V through a resistor that limits the current below 1mA.

Note 4. The GATE pin is referenced to  $V_{\text{OUT}}$  and does not exceed 44V for the entire operating range.

Note 2. All currents into pins are positive; all voltages are referenced to GND unless otherwise noted.

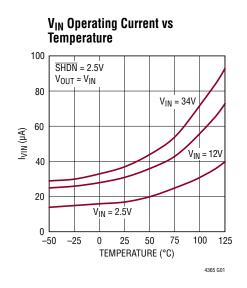

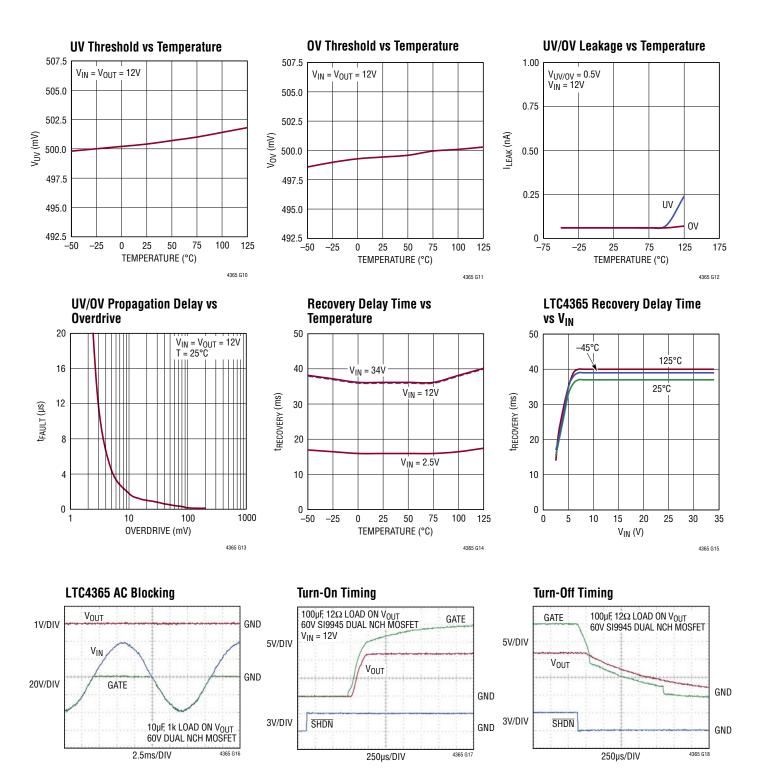

#### **TYPICAL PERFORMANCE CHARACTERISTICS**

V<sub>OUT</sub> Operating Current vs Temperature

V<sub>OUT</sub> Shutdown Current vs Temperature

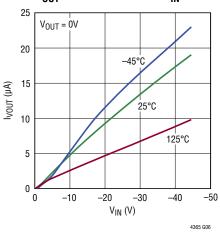

V<sub>OUT</sub> Current vs Reverse V<sub>IN</sub>

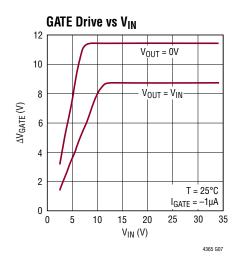

GATE Drive vs Temperature

**GATE Current vs GATE Drive**

Rev. B

# **TYPICAL PERFORMANCE CHARACTERISTICS**

#### PIN FUNCTIONS

Exposed Pad: Connect to device ground.

**FAULT:** Fault Indication Output. This high voltage open drain output is pulled low if UV is below its monitor threshold, if OV is above its monitor threshold, if SHDN is low, or if  $V_{IN}$  has not risen above  $V_{IN(UVLO)}$ .

**GATE:** Gate Drive Output for External N-channel MOSFETs. An internal charge pump provides  $20\mu$ A of pull-up current and up to 9.8V of enhancement to the gate of an external N-channel MOSFET.

When turned off, GATE is pulled just below the lower of  $V_{IN}$  or  $V_{OUT}$ . When  $V_{IN}$  goes negative, GATE is automatically connected to  $V_{IN}$ .

GND: Device Ground.

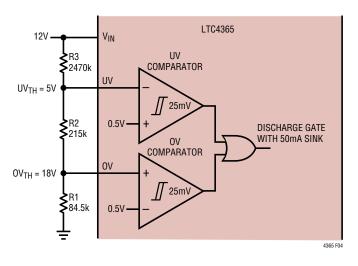

**OV:** Overvoltage Comparator Input. Connect this pin to an external resistive divider to set the desired  $V_{IN}$  overvoltage fault threshold. The OV input connects to an accurate, fast (1µs) comparator with a 0.5V rising threshold and 25mV of hysteresis. When OV rises above its threshold, a 50mA current sink pulls down on the GATE output. When OV falls back below 0.475V, and after a 36ms recovery delay waiting period (1ms for LTC4365-1), the GATE charge pump is enabled. The low leakage current of the OV input allows the use of large valued resistors for the external resistive divider. Connect to GND if unused.

**SHDN:** Shutdown Control Input. SHDN high enables the GATE charge pump which in turn enhances the gate of an external N-channel MOSFET. A low on SHDN generates a pull down on the GATE output with a 90 $\mu$ A current sink and places the LTC4365 in low current mode (10 $\mu$ A). If unused, connect to V<sub>IN</sub>. If V<sub>IN</sub> goes below ground, or if V<sub>IN</sub> rings to 60V, use a current limiting resistor of at least 100k.

**UV:** Undervoltage Comparator Input. Connect this pin to an external resistive divider to set the desired V<sub>IN</sub> undervoltage fault threshold. The UV input connects to an accurate, fast (1µs) comparator with a 0.5V falling threshold and 25mV of hysteresis. When UV falls below its threshold, a 50mA current sink pulls down on the GATE output. When UV rises back above 0.525V, and after a 36ms recovery delay waiting period (1ms for LTC4365-1), the GATE charge pump is enabled. The low leakage current of the UV input allows the use of large valued resistors for the external resistive divider. If unused, connect to V<sub>IN</sub>. While connected to V<sub>IN</sub>, if V<sub>IN</sub> goes below ground, or if V<sub>IN</sub> rings to 60V, use a current limiting resistor of at least 100k.

**V**<sub>IN</sub>: Power Supply Input. Maximum protection range: -40V to 60V. Operating range: 2.5V to 34V.

**V**<sub>OUT</sub>: Output Voltage Sense Input. This pin senses the voltage at the output side of the external N-channel MOSFET. The GATE charge pump voltage is referenced to V<sub>OUT</sub>. It is used as the charge pump input when V<sub>OUT</sub> is greater than approximately 6.5V.

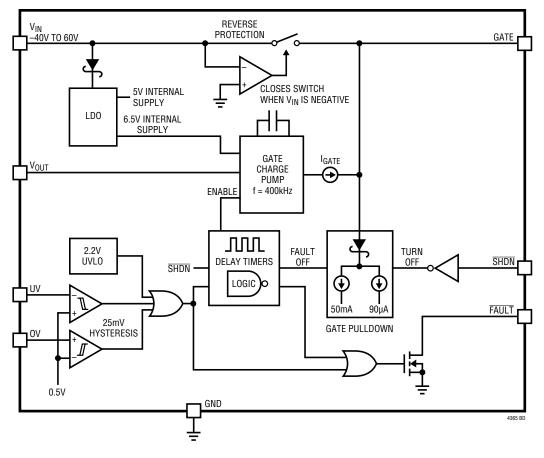

# **BLOCK DIAGRAM**

# OPERATION

Many of today's electronic systems get their power from external sources such as wall wart adapters, batteries and custom power supplies. A typical supply arrangement for a portable product is shown by the operational diagram in Figure 1. Power is supplied by an AC adaptor or, if the plug is withdrawn, by a removable battery. Trouble arises when any of the following occurs:

- The battery is installed backwards

- An AC adaptor of opposite polarity is attached

- An AC adaptor of excessive voltage is attached

- The battery is discharged below a safe level

This can lead to supply voltages that are too high, too low, or even negative. If these power sources are applied

directly to the electronic systems, the systems could be subject to damage. The LTC4365 is an input voltage fault protection N-channel MOSFET controller. The part isolates an input supply from its load to protect the load from unexpected supply voltage conditions, while providing a low loss path for qualified power.

To protect electronic systems from improperly connected power supplies, system designers will often add discrete diodes, transistors and high voltage comparators. The high voltage comparators enable system power only if the input supply falls within a desired voltage window. A Schottky diode or P-channel MOSFET typically added in series with the supply protects against reverse supply connections.

The LTC4365 provides accurate overvoltage and undervoltage comparators to ensure that power is applied to

Rev. B

### OPERATION

the system only if the input supply meets the user selectable voltage window. Reverse supply protection circuits automatically isolate the load from negative input voltages. During normal operation, a high voltage charge pump enhances the gate of external N-channel power MOSFETs. Power consumption is  $10\mu$ A during shutdown and  $125\mu$ A while operating. The LTC4365 integrates all these functions in tiny TSOT-23 and 3mm × 2mm DFN packages.

Figure 1. Operational Diagram Common to Many Portable Products

### **APPLICATIONS INFORMATION**

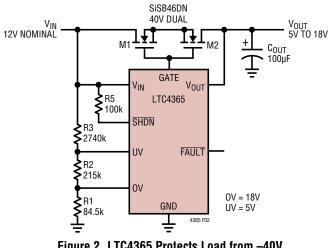

The LTC4365 is an N-channel MOSFET controller that protects a load from faulty supply connections. A basic application circuit using the LTC4365 is shown in Figure 2 The circuit provides a low loss connection from  $V_{IN}$  to  $V_{OUT}$  as long as the voltage at  $V_{IN}$  is between 5V and

Figure 2. LTC4365 Protects Load from –40V to 40V  $V_{\rm IN}$  Faults

18V. Voltages at V<sub>IN</sub> outside of the 5V to 18V range are prevented from getting to the load and can be as high as 40V and as low as -40V. The circuit of Figure 2 protects against negative voltages at V<sub>IN</sub> as shown. No other external components are needed.

During normal operation, the LTC4365 provides up to 9.8V of gate enhancement to the external back-to-back N-channel MOSFETs. This turns on the MOSFET, thus connecting the load at  $V_{OUT}$  to the supply at  $V_{IN}$ .

#### **GATE Drive**

The LTC4365 turns on the external N-channel MOSFETs by driving the GATE pin above  $V_{OUT}$ . The voltage difference between the GATE and  $V_{OUT}$  pins (gate drive) is a function of  $V_{IN}$  and  $V_{OUT}$ .

Figure 3 highlights the dependence of the gate drive on  $V_{IN}$  and  $V_{OUT}$ . When system power is first turned on (SHDN low to high,  $V_{OUT} = 0V$ ), gate drive is at a maximum for all values of  $V_{IN}$ . This helps prevent start-up problems into heavy loads by ensuring that there is enough gate drive to support the load.

As  $V_{OUT}$  ramps up from 0V, the absolute value of the GATE voltage remains fixed until  $V_{OUT}$  is greater than the lower of  $(V_{IN}$ –1V) or 6V. Once  $V_{OUT}$  crosses this threshold, gate drive begins to increase up to a maximum of 9.8V (for  $V_{IN} \geq 12V$ ). The curves of Figure 3 were taken with a GATE load of –1µA. If there were no load on GATE, the gate drive for each  $V_{IN}$  would be slightly higher.

Note that when  $V_{\text{IN}}$  is at the lower end of the operating range, the external N-channel MOSFET must be selected with a corresponding lower threshold voltage.

Figure 3. Gate Drive (GATE –  $V_{OUT}$ ) vs  $V_{OUT}$

Table 1 lists some external MOSFETs compatible with different  $V_{\mbox{\rm IN}}$  supply voltages.

| MOSFET | V <sub>TH(MAX)</sub>                           | V <sub>GS(MAX)</sub>                                                                                              | V <sub>DS(MAX)</sub>                                                                                                                                                |  |

|--------|------------------------------------------------|-------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| SiB914 | 0.8V                                           | 5V                                                                                                                | 8V                                                                                                                                                                  |  |

| Si5920 | 1.0V                                           | 5V                                                                                                                | 8V                                                                                                                                                                  |  |

| Si7940 | 1.5V                                           | 8V                                                                                                                | 12V                                                                                                                                                                 |  |

| Si4214 | 3.0V                                           | 20V                                                                                                               | 30V                                                                                                                                                                 |  |

| Si9945 | 3.0V                                           | 20V                                                                                                               | 60V                                                                                                                                                                 |  |

|        | MOSFET<br>SiB914<br>Si5920<br>Si7940<br>Si4214 | MOSFET     V <sub>TH(MAX)</sub> SiB914     0.8V       Si5920     1.0V       Si7940     1.5V       Si4214     3.0V | MOSFET     V <sub>TH(MAX)</sub> V <sub>GS(MAX)</sub> SiB914     0.8V     5V       Si5920     1.0V     5V       Si7940     1.5V     8V       Si4214     3.0V     20V |  |

| Table 1. Dual MOSFETs for Va | larious Supply Ranges |

|------------------------------|-----------------------|

|------------------------------|-----------------------|

#### **Overvoltage and Undervoltage Protection**

The LTC4365 provides two accurate comparators to monitor for overvoltage (OV) and undervoltage (UV) conditions at  $V_{IN}$ . If the input supply rises above the user adjustable OV threshold, the gate of the external MOSFET is quickly turned off, thus disconnecting the load from the input. Similarly, if the input supply falls below the user adjustable UV threshold, the gate of the external MOSFET also is quickly turned off. Figure 4 shows a UV/OV application for an input supply of 12V.

Figure 4. UV, OV Comparators Monitor 12V Supply

The external resistive divider allows the user to select an input supply range that is compatible with the load at V<sub>OUT</sub>. Furthermore, the UV and OV inputs have very low leakage currents (typically < 1nA at 100°C), allowing for large values in the external resistive divider. In the application of Figure 4, the load is connected to the supply only if V<sub>IN</sub> lies between 5V and 18V. In the event that V<sub>IN</sub> goes above 18V or below 5V, the gate of the external N-channel MOSFET is immediately discharged with a 50mA current sink, thus isolating the load from the supply.

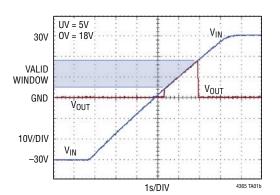

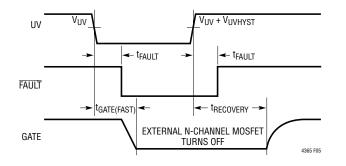

Figure 5 shows the timing associated with the UV pin. Once a UV fault propagates through the UV comparator ( $t_{FAULT}$ ), the FAULT output is asserted low and a 50mA current sink discharges the GATE pin. As  $V_{OUT}$  falls, the GATE pin tracks  $V_{OUT}$ .

Figure 5. UV Timing (OV < ( $V_{OV} - V_{OVHYST}$ ), SHDN > 1.2V)

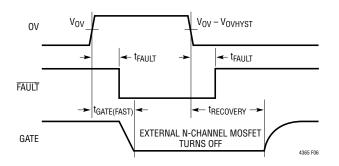

Figure 6 shows the timing associated with the OV pin. Once an OV fault propagates through the OV comparator ( $t_{FAULT}$ ), the FAULT output is asserted low and a 50mA current sink discharges the GATE pin. As  $V_{OUT}$  falls, the GATE pin tracks  $V_{OUT}$ .

Figure 6. OV Timing (UV > ( $V_{UV} + V_{UVHYST}$ ), SHDN > 1.2V)

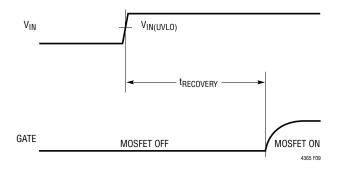

When both the UV and OV faults are removed, the external MOSFET is not immediately turned on. The input supply must remain within the user selected power good window for at least 36ms ( $t_{RECOVERY}$ ) before the load is again connected to the supply. This recovery timeout period filters noise (including line noise) at the input supply and prevents chattering of power at the load. For applications that require faster turn-on after a fault, the LTC4365-1 provides a 1ms recovery timeout period.

#### Procedure for Selecting UV/OV External Resistor Values

The following 3-step procedure helps select the resistor values for the resistive divider of Figure 4. This procedure minimizes UV and OV offset errors caused by leakage currents at the respective pins.

1. Choose maximum tolerable offset at the UV pin,  $V_{OS(UV)}$ . Divide by the worst case leakage current at the UV pin,  $I_{UV}$  (10nA). Set the sum of R1 + R2 equal to  $V_{OS(UV)}$  divided by 10nA. Note that due to the presence of R3, the actual offset at UV will be slightly lower:

$$R1 + R2 = \frac{V_{OS(UV)}}{I_{UV}}$$

2. Select the desired  $V_{\text{IN}}$  UV trip threshold,  $UV_{\text{TH}}.$  Find the value of R3:

$$R3 = \frac{V_{OS(UV)}}{I_{UV}} \bullet \left(\frac{UV_{TH} - 0.5V}{0.5V}\right)$$

3. Select the desired  $V_{\text{IN}}$  OV trip threshold,  $\text{OV}_{\text{TH}}.$  Find the values of R1 and R2:

$$R1 = \frac{\left(\frac{V_{OS(UV)}}{I_{UV}}\right) + R3}{0V_{TH}} \bullet 0.5V$$

$$R2 = \frac{V_{OS(UV)}}{I_{UV}} - R1$$

The example of Figure 4 uses standard 1% resistor values. The following parameters were selected:

$$V_{OS(UV)} = 3mV$$

$I_{UV} = 10nA$

$UV_{TH} = 5V$

$OV_{TH} = 18V$

The resistor values can then be solved:

1. R1 + R2 =

$$\frac{3mV}{10nA}$$

= 300k

2. R3 =

$$2 \cdot \frac{3mV}{10nA} \cdot (5V - 0.5V) = 2.7M$$

The closest 1% value: R3 = 2.74M:

3.

$$R1 = \frac{300k + 1.82M}{2 \cdot 18V} = 84.4k$$

The closest 1% value: R1 = 84.5k:

R2 = 300k - 84.5k = 215.5k

The closest 1% value: R2 = 215k

Therefore: OV = 17.99V, UV = 5.07V.

#### **Reverse VIN Protection**

The LTC4365's rugged and hot-swappable V<sub>IN</sub> input helps protect the more sensitive circuits at the output load. If the input supply is plugged in backwards, or a negative supply is inadvertently connected, the LTC4365 prevents this negative voltage from passing to the output load.

The LTC4365 employs a novel, high speed reverse supply voltage monitor. When the negative  $V_{IN}$  voltage is detected, an internal switch connects the gates of the external back-to-back N-channel MOSFETs to the negative input supply.

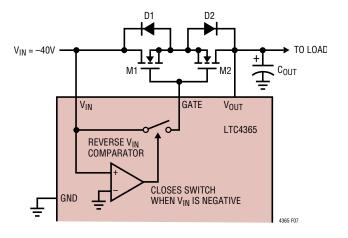

As shown in Figure 7, external back-to-back N-channel MOSFETs are required for reverse supply protection. When  $V_{IN}$  goes negative, the reverse  $V_{IN}$  comparator closes the internal switch, which in turn connects the gates of the external MOSFETs to the negative  $V_{IN}$  voltage. The body diode (D1) of M1 turns on, but the body diode (D2) of M2 remains in reverse blocking mode. This means that the common source connection of M1 and M2 remains about a diode drop higher than  $V_{IN}$ . Since the gate voltage of M2 is shorted to  $V_{IN}$ , M2 will be turned off and no current can flow from  $V_{IN}$  to the load at  $V_{OUT}$ . Note that the voltage rating of M2 must withstand the reverse voltage excursion at  $V_{IN}$ .

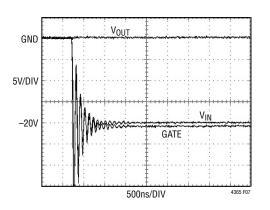

Figure 8 illustrates the waveforms that result when  $V_{IN}$  is hot plugged to -20V.  $V_{IN}$ , GATE and  $V_{OUT}$  start out at ground just before the connection is made. Due to the parasitic inductance of the  $V_{IN}$  and GATE connections, the voltage at the  $V_{IN}$  and GATE pins ring significantly below -20V. Therefore, a 40V N-channel MOSFET was selected to survive the overshoot.

The speed of the LTC4365 reverse protection circuits is evident by how closely the GATE pin follows  $V_{\rm IN}$  during the negative transients. The two waveforms are almost indistinguishable on the scale shown.

The trace at V<sub>OUT</sub>, on the other hand, does not respond to the negative voltage at V<sub>IN</sub>, demonstrating the desired reverse supply protection. The waveforms of Figure 8 were captured using a 40V dual N-channel MOSFET, a 10 $\mu$ F ceramic output capacitor and no load current on V<sub>OUT</sub>.

Figure 7. Reverse VIN Protection Circuits

Figure 8. Hot Swapping  $V_{IN}$  to –20V

#### **Recovery Timer**

The LTC4365 has a recovery delay timer that filters noise at V<sub>IN</sub> and helps prevent chatter at V<sub>OUT</sub>. After either an OV or UV fault has occurred, the input supply must return to the desired operating voltage window for at least 36ms ( $t_{RECOVERY}$ ) in order to turn the external MOSFET back on as illustrated in Figure 5 and Figure 6. For applications that require faster turn-on after a fault, the LTC4365-1 provides a 1ms recovery timeout period.

Going out of and then back into fault in less than  $t_{RECOVERY}$  will keep the MOSFET off continuously. Similarly, coming out of shutdown (SHDN low to high) triggers an 800µs start-up delay timer (see Figure 11).

The recovery timer is also active while the part is powering up. The recovery timer starts once  $V_{IN}$  rises above  $V_{IN(UVLO)}$  and  $V_{IN}$  lies within the user selectable UV/OV power good window. See Figure 9.

Figure 9. Recovery Timing During Power-On (OV = GND, UV =  $\overline{SHDN} = V_{IN}$ )

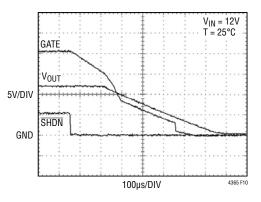

#### Gentle Shutdown

The  $\overline{\text{SHDN}}$  input turns off the external MOSFETs in a gentle, controlled manner. When  $\overline{\text{SHDN}}$  is asserted low, a 90µA current sink slowly begins to turn off the external MOSFETs.

Once the voltage at the GATE pin falls below the voltage at the V<sub>OUT</sub> pin, the current sink is throttled back and a feedback loop takes over. This loop forces the GATE voltage to track V<sub>OUT</sub>, thus keeping the external MOSFETs off as V<sub>OUT</sub> decays. Note that when V<sub>OUT</sub> < 4.5V, the GATE pin is pulled to within 400mV of ground.

Gentle gate turn off reduces load current slew rates and mitigates voltage spikes due to parasitic inductances. To

further decrease GATE pin slew rate, place a capacitor across the gate and source terminals of the external MOS-FETs. The waveforms of Figure 10 were captured using the Si4214 dual N-channel MOSFETs, and a 2A load with  $100\mu$ F output capacitor.

Figure 10. Gentle Shutdown: GATE Tracks  $V_{\text{OUT}}$  as  $V_{\text{OUT}}$  Decays

#### **FAULT Status**

The FAULT high voltage open drain output is driven low if SHDN is asserted low, if  $V_{IN}$  is outside the desired UV/OV voltage window, or if  $V_{IN}$  has not risen above  $V_{IN(UVLO)}$ . Figure 5, Figure 6 and Figure 11 show the FAULT output timing.

Figure 11. Gentle Shutdown Timing

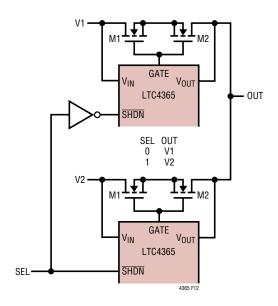

#### Select Between Two Input Supplies

With the part in shutdown, the  $V_{\rm IN}$  and  $V_{\rm OUT}$  pins can be driven by separate power supplies. The LTC4365 then automatically drives the GATE pin just below the lower of

the two supplies, thus turning off the external back-to-back MOSFETs. The application of Figure 12 uses two LTC4365s to select between two power supplies. Care should be taken to ensure that only one of the two LTC4365s is enabled at any given time.

Figure 12. Selecting One of Two Supplies

#### Single MOSFET Application

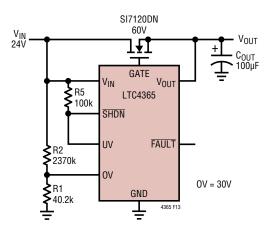

When reverse  $V_{\rm IN}$  protection is not needed, only a single external N-channel MOSFET is necessary. The application circuit of Figure 13 connects the load to  $V_{\rm IN}$  when  $V_{\rm IN}$  is less than 30V, and uses the minimal set of external components.

Figure 13. Small Footprint Single MOSFET Application Protects Against 60V

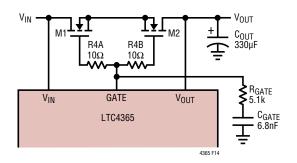

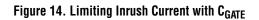

#### Limiting Inrush Current During Turn-On

The LTC4365 turns on the external N-channel MOSFET with a  $20\mu$ A current source. The maximum slew rate at the GATE pin can be reduced by adding a capacitor on the GATE pin:

Slew Rate =

$$\frac{20\mu A}{C_{GATE}}$$

Since the MOSFET acts like a source follower, the slew rate at  $V_{\text{OUT}}$  equals the slew rate at GATE.

Therefore, inrush current is given by:

$$I_{\text{INRUSH}} = \frac{C_{\text{OUT}}}{C_{\text{GATE}}} \bullet 20 \mu \text{A}$$

For example, a 1A inrush current to a  $330\mu$ F output capacitance requires a GATE capacitance of:

$$C_{GATE} = \frac{20\mu A \bullet C_{OUT}}{I_{INRUSH}}$$

$$C_{GATE} = \frac{20\mu A \cdot 330\mu F}{1A} = 6.6nF$$

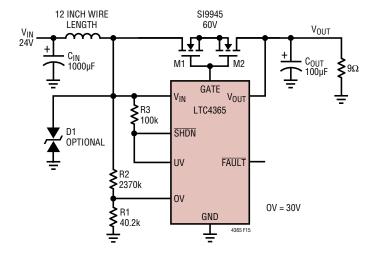

The 6.8nF  $C_{GATE}$  capacitor in the application circuit of Figure 14 limits the inrush current to approximately 1A.  $R_{GATE}$  makes sure that  $C_{GATE}$  does not affect the fast GATE turn off characteristics during UV/OV faults, or during reverse  $V_{IN}$  connection. R4A and R4B help prevent high frequency oscillations with the external N-channel MOSFET and related board parasitics.

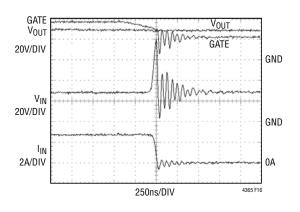

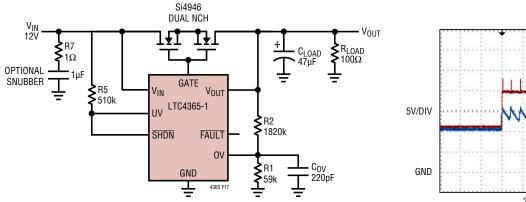

#### Transients During OV Fault

The circuit of Figure 15 was used to display transients during an overvoltage condition. The nominal input supply is 24V and it has an overvoltage threshold of 30V. The parasitic inductance is that of a 1 foot wire (roughly 300nH). Figure 16 shows the waveforms during an overvoltage condition at  $V_{IN}$ . These transients depend on the parasitic inductance and resistance of the wire along with the ca-

pacitance at the V<sub>IN</sub> node. D1 is an optional power clamp (TVS, Tranzorb) recommended for applications where the DC input voltage can exceed 24V and with large V<sub>IN</sub> parasitic inductance. No clamp was used to capture the waveforms of Figure 16. In order to maintain reverse supply protection, D1 must be a bi-directional clamp rated for at least 225W peak pulse power dissipation.

Figure 15. OV Fault with Large VIN Inductance

Figure 16. Transients During OV Fault When No Tranzorb (TVS) Is Used

Rev F

#### **REGULATOR APPLICATIONS**

#### Hysteretic Regulator

Built-in hysteresis and the availability of both inverting and noninverting control inputs (OV and UV) facilitate the design of hysteretic regulators. Figure 17 shows how the LTC4365-1 can protect a load from OV transients, while regulating the output voltage at a user-defined level. When the output voltage reaches its OV limit, the LTC4365-1 turns off the external MOSFETs. The load current then discharges the output capacitance until OV falls below the hysteresis voltage. The external MOSFETs are turned back on after a 1ms delay. Figure 18 shows the waveforms for the circuit of Figure 17. Note that the duration, magnitude and duty cycle of the  $V_{\mbox{\scriptsize IN}}$  glitch must not exceed the SOA rating of the external MOSFETs.

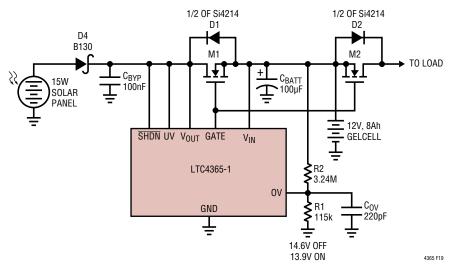

#### Solar Charger

Figure 19 shows a series regulator for a solar charger. The LTC4365-1 connects the solar charger to the battery when the battery voltage falls below 13.9V (after a 1ms delay). Conversely, when the battery reaches 14.6V, the LTC4365-1 immediately ( $2\mu$ s) opens the charging path.

Regulation of the battery voltage is achieved by connecting a resistive divider from the battery to the accurate OV comparator input (with 5% hysteresis). The fast rising response of the OV comparator prevents the battery voltage from rising above the user-selected threshold.

Figure 17. Hysteretic Regulation of  $V_{OUT}$  During OV Transients

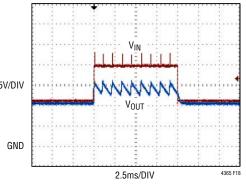

Figure 18. V<sub>OUT</sub> Regulates at 16V When V<sub>IN</sub> Glitches Above Desired Level

Figure 19. Series Hysteretic Solar Charger with Reverse-Battery and Solar Panel Protection

Note that during initial start-up, the LTC4365-1 will not turn on the external MOSFETs until a battery is first connected to the  $V_{IN}$  pin. To begin operation,  $V_{IN}$  must initially rise above the 2.2V UVLO lockout voltage. Connecting the battery ensures that the LTC4365-1 comes out of UVLO.

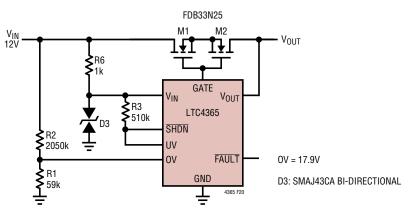

#### **12V Application with 150V Transient Protection**

Figure 20 shows a 12V application that withstands input supply transients up to 150V. When the input voltage exceeds 17.9V, the OV resistive divider turns off the external MOSFETs. As  $V_{IN}$  rises to 150V, the gate of transistor M1 remains in the Off condition, thus preventing conduction from  $V_{IN}$  to  $V_{OUT}$ . Note that M1 must have an operating range above 150V.

Resistor R6 and diode D3 clamp the LTC4365 supply voltage to 50V. To prevent R6 from interfering with reverse operation, the recommended value is 1k or less. Note that the power handling capability of R6 must be considered in order to avoid overheating during transients. D3 is shown as a bidirectional clamp in order to achieve reverse-polarity protection at V<sub>IN</sub>. M2 is also required in order to protect V<sub>OUT</sub> from negative voltages at V<sub>IN</sub> and should have an operating range beyond the breakdown of D3. If reverse protection is not desired remove M2 and connect the source of M1 directly to V<sub>OUT</sub>.

#### **MOSFET Selection**

To protect against a negative voltage at  $V_{IN}$ , the external N-channel MOSFETs must be configured in a back-toback arrangement. Dual N-channel packages are thus the best choice. The MOSFET is selected based on its power handling capability, drain and gate breakdown voltages, and threshold voltage.

The drain to source breakdown voltage must be higher than the maximum voltage expected between  $V_{IN}$  and  $V_{OUT}$ . Note that if an application generates high energy transients during normal operation or during Hot Swap<sup>TM</sup>, the external MOSFET must be able to withstand this transient voltage.

Due to the high impedance nature of the charge pump that drives the GATE pin, the total leakage on the GATE pin must be kept low. The gate drive curves of Figure 2 were measured with a 1 $\mu$ A load on the GATE pin. Therefore, the leakage on the GATE pin must be no greater than 1 $\mu$ A in order to match the curves of Figure 2. Higher leakage currents will result in lower gate drive. The dual N-channel MOSFETs shown in Table 1 all have a maximum GATE leakage current of 100nA. Additionally, Table 1 lists representative MOSFETs that would work at different values of V<sub>IN</sub>.

#### Layout Considerations

The trace length between the  $V_{\rm IN}$  pin and the drain of the external MOSFET should be minimized, as well as the trace length between the GATE pin of the LTC4365 and the gates of the external MOSFETs.

Place the bypass capacitors at  $V_{OUT}$  as close as possible to the external MOSFET. Use high frequency ceramic capacitors in addition to bulk capacitors to mitigate Hot Swap ringing. Place the high frequency capacitors closest to the MOSFET. Note that bulk capacitors mitigate ringing by virtue of their ESR. Ceramic capacitors have low ESR and can thus ring near their resonant frequency.

Figure 20. 12V Application Protected from 150V Transients

### PACKAGE DESCRIPTION

**TS8** Package 8-Lead Plastic TSOT-23 (Reference LTC DWG # 05-08-1637 Rev A)

NOTE:

1. DRAWING CONFORMS TO VERSION (WECD-1) IN JEDEC PACKAGE OUTLINE MO-229 2. DRAWING NOT TO SCALE

3. ALL DIMENSIONS ARE IN MILLIMETERS

ALE DIMENSIONS ARE IN WILLING LENS

DIMENSIONS OF EXPOSED PAD ON BOTTOM OF PACKAGE DO NOT INCLUDE MOLD FLASH. MOLD FLASH, IF PRESENT, SHALL NOT EXCEED 0.15mm ON ANY SIDE

5. EXPOSED PAD SHALL BE SOLDER PLATED

6. SHADED AREA IS ONLY A REFERENCE FOR PIN 1 LOCATION ON THE TOP AND BOTTOM OF PACKAGE

### **REVISION HISTORY**

| REV | DATE  | DESCRIPTION                                                                     | PAGE NUMBER |

|-----|-------|---------------------------------------------------------------------------------|-------------|

| Α   | 09/13 | Added LTC4365-1 Information                                                     | Multiple    |

|     |       | Operation section: Rewritten with new Figure 1                                  | 8, 9        |

|     |       | Table 1: MOSFET for ≤30V changed to Si4214 from Si4230                          | 10          |

|     |       | Figure 13: Inserted R5, 100k resistor to SHDN pin                               | 14          |

|     |       | Added "Regulator Applications" with three subsections and Figures 17 to 20      | 16, 17      |

|     |       | Updated Typical Application                                                     | 20          |

| В   | 09/19 | Added AEC-Q100 qualification and "W" part numbers                               | 1, 3        |

|     |       | Revised application examples (Figures 2 and 4) to support $V_{OUT} = 5V$ to 18V | 9-12        |

# TYPICAL APPLICATION

LTC4365 Protects Step Down Regulator from –40V to 40V  $V_{\text{IN}}$  Faults

### **RELATED PARTS**

| PART NUMBER     | DESCRIPTION                                                             | COMMENTS                                                                                        |

|-----------------|-------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------|

| LT4363          | Surge Stopper Overvoltage/Overcurrent Protection Regulator              | Wide Operating Range: 4V to 80V, Reverse Protection to –60V, Adjustable<br>Output Clamp Voltage |

| LTC4364         | Surge Stopper with Ideal Diode                                          | 4V to 80V Operation, -40V Reverse Input, -20V Reverse Output                                    |

| LTC4366         | Floating Surge Stopper                                                  | 9V to >500V Operation, 8-Pin TSOT and 3mm × 2mm DFN Packages                                    |

| LTC4361         | Overvoltage/Overcurrent Protection Controllers                          | 5.8V Overvoltage Threshold, 85V Absolute Maximum                                                |

| LTC2909         | Triple/Dual Inputs UV/OV Negative Monitor                               | Pin Selectable Input Polarity Allows Negative and OV Monitoring                                 |

| LTC2912/LTC2913 | Single/Dual UV/OV Voltage Monitor                                       | Ads UV and OV Trip Values, ±1.5% Threshold Accuracy                                             |

| LTC2914         | Quad UV/OV Monitor                                                      | For Positive and Negative Supplies                                                              |

| LTC2955         | Pushbutton On/Off Controller                                            | Automatic Turn-On, 1.5V to 36V Input, ±36V PB Input                                             |

| LT4256          | Positive 48V Hot Swap Controller with<br>Open-Circuit Detect            | Foldback Current Limiting, Open-Circuit and Overcurrent Fault Output,<br>Up to 80V Supply       |

| LTC4260         | Positive High Voltage Hot Swap Controller with ADC and I <sup>2</sup> C | Wide Operating Range 8.5V to 80V                                                                |

| LTC4352         | Ideal MOSFET ORing Diode                                                | External N-Channel MOSFETs Replace ORing Diodes, 0V to 18V                                      |

| LTC4354         | Negative Voltage Diode-OR Controller                                    | Controls Two N-Channel MOSFETs, 1.2µs Turn-Off, –80V Operation                                  |

| LTC4355         | Positive Voltage Diode-OR Controller                                    | Controls Two N-Channel MOSFETs, 0.4µs Turn-Off, 80V Operation                                   |

| LT1913          | Step-Down Switching Regulator                                           | 3.6V to 25V Input, 3.5A Maximum Current, 200kHz to 2.4MHz                                       |

### **Mouser Electronics**

Authorized Distributor

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

#### Analog Devices Inc.:

LTC4365CTS8#TRPBF LTC4365HTS8#TRPBF LTC4365ITS8-1#TRMPBF LTC4365HDDB-1#TRMPBF LTC4365CDDB-1#TRMPBF LTC4365IDDB-1#TRMPBF LTC4365CDDB#TRMPBF LTC4365IDDB#TRMPBF LTC4365CDDB-1#TRPBF LTC4365HDDB-1#TRPBF LTC4365CDDB#TRPBF LTC4365ITS8#TRMPBF LTC4365HDDB#TRPBF LTC4365IDDB#TRPBF LTC4365ITS8-1#TRPBF LTC4365HTS8-1#TRMPBF LTC4365CTS8-1#TRMPBF LTC4365CTS8#TRMPBF LTC4365HTS8#TRMPBF LTC4365CTS8-1#TRPBF LTC4365ITS8#TRPBF LTC4365HDDB#TRPBF LTC4365IDDB-1#TRPBF LTC4365HTS8-1#TRPBF LTC4365CTS8-1#TRMPBF LTC4365CTS8#TRMPBF LTC4365HTS8#TRMPBF LTC4365CTS8-1#TRPBF LTC4365ITS8#TRPBF LTC4365HDDB#TRMPBF LTC4365IDDB-1#TRPBF LTC4365HTS8-1#TRPBF DC1555C-B DC1555C-A LTC4365HTS8#WTRMPBF LTC4365HTS8#WTRPBF