Kaimeite Electronic (HK) Co., Limited

First choice One-Stop Mixed Distributor for World-Class manufacturer Email: info@kaimte.com Website: www.kaimte.com

# Click to view price, real time Inventory, Delivery & Lifecycle Information;

# TPS7A6033QKTTRQ1

# Texas instruments

LDO Voltage Regulators AC 300mA 40V LDO Reg

Any questions, please feel free to contact us. info@kaimte.com

#### TPS7A60-Q1, TPS7A61-Q1

SLVSA62J - MARCH 2010 - REVISED MARCH 2020

# TPS7A6x-Q1 300-mA, 40-V Low-Dropout Regulator With 25-µA Quiescent Current

#### 1 Features

- AEC-Q100 qualified for automotive applications:

- Temperature grade 1: –40°C to 125°C, T<sub>A</sub>

- Junction Temperature: –40°C to 150°C, T<sub>.I</sub>

- Low dropout voltage:

- 300 mV at  $I_{OUT} = 150$  mA

- 7-V to 40-V wide input voltage range with up to 45-V transients

- · 300-mA maximum output current

- Ultralow quiescent current:

- $I_{QUIESCENT}$  = 25  $\mu$ A (typical) at light loads

- I<sub>SLEEP</sub> < 2  $\mu$ A when ENABLE = low

- 3.3-V and 5-V fixed output voltage

- Low-ESR ceramic output stability capacitor

- Integrated power-on reset:

- Programmable delay

- Open-drain reset output

- Integrated fault protection:

- Short-circuit and overcurrent protection

- Thermal shutdown

- Low-input-voltage tracking

- Thermally enhanced power packages:

- 5-pin TO-263 (KTT, D2PAK)

- 5-pin TO-252 (KVU, DPAK)

## 2 Applications

- Automotive head units

- Automotive center information displays

- · Hybrid instrument clusters

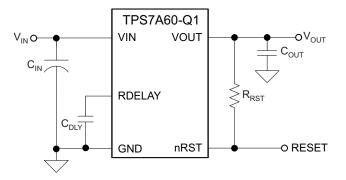

#### **Programmable Reset Delay Option**

#### 3 Description

The TPS7A60-Q1 and TPS7A61-Q1 comprise a family of low-dropout linear voltage regulators designed for low power consumption and quiescent current less than 25 µA in light-load applications. feature integrated devices overcurrent protection and are designed to achieve stable operation even with low-ESR ceramic capacitors. Power-on-reset delay is implemented during device start-up to indicate that the output voltage is stable and in regulation. The power-on-reset delay is fixed (250 µs typical), and can also be programmed by an external capacitor. A low-voltage tracking feature allows for a smaller input capacitor and can possibly eliminate the need of using a boost converter during cold-crank conditions. Because of these features, these devices are well-suited in power supplies for various automotive applications.

#### Device Information<sup>(1)</sup>

| PART NUMBER  | PACKAGE    | BODY SIZE (NOM)    |  |  |  |

|--------------|------------|--------------------|--|--|--|

| TDC746022 O4 | TO-263 (5) | 10.16 mm × 9.15 mm |  |  |  |

| TPS7A6033-Q1 | TO-252 (5) | 6.10 mm × 6.60 mm  |  |  |  |

| TPS7A6050-Q1 | TO-263 (5) | 10.16 mm × 9.15 mm |  |  |  |

| 1P57A6050-Q1 | TO-252 (5) | 6.10 mm × 6.60 mm  |  |  |  |

| TPS7A6133-Q1 | TO-252 (5) | 6.10 mm × 6.60 mm  |  |  |  |

| TPS7A6150-Q1 | TO-252 (5) | 6.10 mm × 6.60 mm  |  |  |  |

(1) For all available packages, see the orderable addendum at the end of the data sheet.

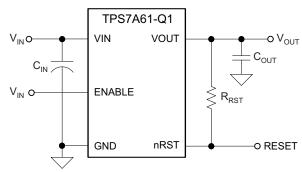

#### **Enable Option**

#### **Table of Contents**

|   | Features 1                           | 8.3 Feature Description13                               |

|---|--------------------------------------|---------------------------------------------------------|

| 2 | Applications 1                       | 8.4 Device Functional Modes17                           |

| 3 | Description 1                        | 9 Application and Implementation 18                     |

| 4 | Revision History2                    | 9.1 Application Information18                           |

| 5 | Device Comparison Table 4            | 9.2 Typical Applications18                              |

| 6 | Pin Configuration and Functions5     | 10 Power Supply Recommendations 22                      |

| 7 | Specifications 6                     | 11 Layout 22                                            |

| • | 7.1 Absolute Maximum Ratings         | 11.1 Layout Guidelines22                                |

|   | 7.2 ESD Ratings                      | 11.2 Layout Examples25                                  |

|   | 7.3 Recommended Operating Conditions | 12 Device and Documentation Support 27                  |

|   | 7.4 Thermal Information              | 12.1 Related Links                                      |

|   | 7.5 Electrical Characteristics       | 12.2 Receiving Notification of Documentation Updates 27 |

|   | 7.6 Switching Characteristics        | 12.3 Community Resources27                              |

|   | 7.7 Typical Characteristics 9        | 12.4 Trademarks27                                       |

| 8 | Detailed Description 12              | 12.5 Electrostatic Discharge Caution                    |

| - | 8.1 Overview                         | 12.6 Glossary                                           |

|   | 8.2 Functional Block Diagrams        | 13 Mechanical, Packaging, and Orderable Information27   |

#### 4 Revision History

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

| C | hanges from Revision I (May 2018) to Revision J                                  |   |  |

|---|----------------------------------------------------------------------------------|---|--|

| • | Changed AEC-Q100 Features bullets to conform to new standard                     | 1 |  |

| • | Changed input voltage range from 11 V to 7 V throughout document                 | 1 |  |

| • | Changed Applications section                                                     | 1 |  |

| • | Added footnote to V <sub>IN</sub> row in Recommended Operating Conditions table  | 6 |  |

| • | Added footnote to V <sub>IN</sub> row in <i>Electrical Characteristics</i> table | 7 |  |

#### Changes from Revision H (March 2016) to Revision I

| 'A60- |  |

|-------|--|

| Abu-  |  |

|       |  |

Page

| • | Changed device names from TPS7A6033-Q1, TPS7A6050-Q1, TPS7A6133-Q1, and TPS7A6150-Q1 to TPS7A60-Q1 and TPS7A61-Q1                                    |

|---|------------------------------------------------------------------------------------------------------------------------------------------------------|

| • | Changed 4 V to 11 V in fourth <i>Features</i> bullet                                                                                                 |

|   | Changed V <sub>IN</sub> minimum specification from 4 V to 11 V in <i>Recommended Operating Conditions</i> table                                      |

| • | Changed V <sub>IN</sub> and V <sub>ENABLE</sub> parameters to be separate rows, changed V <sub>ENABLE</sub> description to <i>Enable pin voltage</i> |

| • | Changed V <sub>IN</sub> parameter: condensed test conditions to one row and changed minimum specification from 5.3 V to 11 V 7                       |

| • | Changed 4 V (3.3-V version) or 5.3 V (5-V version) to 11 V in Regulation Mode section                                                                |

| • | Changed Input voltage range parameter example value in TPS7A60-Q1 Design Parameters table                                                            |

| • | Changed Input voltage range parameter example value in TPS7A61-Q1 Design Parameters table                                                            |

#### Changes from Revision G (April 2012) to Revision H

## Page

| • | Added new bullets to top of Features list                                                                                                                                                                                                                                                                         |

|---|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| • | Appended "-Q1" to the part number in numerous locations throughout the data sheet                                                                                                                                                                                                                                 |

| • | Added ESD Rating table, Switching Characteristics table Feature Description section, Device Functional Modes, Application and Implementation section, Power Supply Recommendations section, Layoutsection, Device and Documentation Support section, and Mechanical, Packaging, and Orderable Information section |

| • | Added MIN values for VIN. RDELAY, and VOUT in Absolute Maximum Ratings table                                                                                                                                                                                                                                      |

Submit Documentation Feedback

Copyright © 2010–2020, Texas Instruments Incorporated

Product Folder Links: TPS7A60-Q1 TPS7A61-Q1

## SLVSA62J -MARCH 2010-REVISED MARCH 2020

| 14/14/14/ | 4: |  |

|-----------|----|--|

|           |    |  |

| • | Deleted two graphs from the Typical Characteristics section              | 9  |

|---|--------------------------------------------------------------------------|----|

| • | Updated Typical Application Schematic for the TPS7A61xx-Q1 Device image. | 20 |

Product Folder Links: TPS7A60-Q1 TPS7A61-Q1

# 5 Device Comparison Table

| PART NUMBER  | OUTPUT VOLTAGE | ENABLE | RESET | PROGRAMMABLE RESET DELAY |

|--------------|----------------|--------|-------|--------------------------|

| TPS7A6033-Q1 | 221/           | No     | Yes   | Yes                      |

| TP37A6033-QT | 3.3 V          | No     | Yes   | Yes                      |

| TPS7A6050-Q1 | 5 V            | No     | Yes   | Yes                      |

| 1F37A0030-Q1 |                | No     | Yes   | Yes                      |

| TPS7A6133-Q1 | 3.3 V          | Yes    | Yes   | No                       |

| TPS7A6150-Q1 | 5 V            | Yes    | Yes   | No                       |

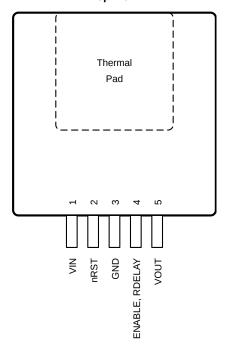

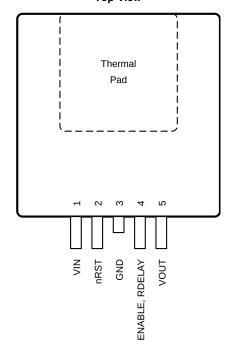

# 6 Pin Configuration and Functions

KTT Package 5-Pin TO-263 With Exposed Thermal Pad Top View

KVU Package 5-Pin TO-252 With Exposed Thermal Pad Top View

#### **Pin Functions**

| PIN    |     | TYPE                                                                                                                                                                                                                                                                                                             | DESCRIPTION                                                                                                                                                                                                                                                                                                                               |  |  |

|--------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| NAME   | NO. |                                                                                                                                                                                                                                                                                                                  | DESCRIPTION                                                                                                                                                                                                                                                                                                                               |  |  |

|        |     | Enable pin (for TPS7A61-Q1 only): This is a high-voltage-tolerant input pin with an internal pulldown. A high input to this pin activates the device and turns the regulator ON. This input can be connected to the VIN pin for self-bias applications. If this pin is not connected, the device stays disabled. |                                                                                                                                                                                                                                                                                                                                           |  |  |

| GND    | 3   | I/O                                                                                                                                                                                                                                                                                                              | Ground pin: This is the signal-ground pin of the IC.                                                                                                                                                                                                                                                                                      |  |  |

| nRST   | 2   | 0                                                                                                                                                                                                                                                                                                                | Reset pin: This is an output pin with an external pullup resistor connected to the VOUT pin.                                                                                                                                                                                                                                              |  |  |

| RDELAY | 4   | 0                                                                                                                                                                                                                                                                                                                | O Reset delay timer pin (for TPS7A60-Q1 only): This pin is used to program the reset delay timer using a external capacitor (C <sub>DLY</sub> ) to ground.                                                                                                                                                                                |  |  |

| VIN    | 1   | I                                                                                                                                                                                                                                                                                                                | Input voltage pin: The unregulated input voltage is supplied to this pin. A bypass capacitor is connected between the VIN pin and the GND pin to dampen input line transients.                                                                                                                                                            |  |  |

| VOUT   | 5   | 0                                                                                                                                                                                                                                                                                                                | Regulated output-voltage pin: This is a regulated voltage output ( $V_{OUT} = 3.3 \text{ V}$ or 5 V, as applicable) pin with a limitation on maximum output current. In order to achieve stable operation and prevent oscillation, an external output capacitor ( $C_{OUT}$ ) with low ESR is connected between this pin and the GND pin. |  |  |

## 7 Specifications

#### 7.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted)(1)

|                                               |             | MIN  | MAX | UNIT |

|-----------------------------------------------|-------------|------|-----|------|

| Unregulated inputs (2)                        | VIN, ENABLE | -0.3 | 45  | V    |

| Regulated output                              | VOUT        | -0.3 | 7   | V    |

| Open-drain reset output                       | nRST        | -0.3 | 7   | V    |

| Output to charge an external capacitor        | RDELAY      | -0.3 | 7   | V    |

| Operating ambient temperature, T <sub>J</sub> | -40         | 150  | °C  |      |

| Storage temperature, T <sub>stq</sub>         | -65         | 150  | °C  |      |

<sup>(1)</sup> Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

#### 7.2 ESD Ratings

|                    |                                                  |                                                         | VALUE | UNIT |  |  |  |

|--------------------|--------------------------------------------------|---------------------------------------------------------|-------|------|--|--|--|

| TPS7A60            | TPS7A60-Q1 and TPS7A61-Q1 Devices in KVU Package |                                                         |       |      |  |  |  |

| V <sub>(ESD)</sub> | Electrostatic discharge                          | Human-body model (HBM), per AEC Q100-002 <sup>(1)</sup> | ±4000 | V    |  |  |  |

|                    |                                                  | Charged-device model (CDM), per AEC Q100-011            | ±1000 |      |  |  |  |

| TPS7A60            | TPS7A60-Q1 Device in KTT Package                 |                                                         |       |      |  |  |  |

| V                  | Clastrostatic discharge                          | Human-body model (HBM), per AEC Q100-002 <sup>(1)</sup> | ±4000 | V    |  |  |  |

| $V_{(ESD)}$        | Electrostatic discharge                          | Charged-device model (CDM), per AEC Q100-011            | ±1500 | V    |  |  |  |

<sup>(1)</sup> AEC Q100-002 indicates that HBM stressing shall be in accordance with the ANSI/ESDA/JEDEC JS-001 specification.

#### 7.3 Recommended Operating Conditions

over operating ambient temperature range (unless otherwise noted)

|                                         |                                   | MIN              | MAX  | UNIT |

|-----------------------------------------|-----------------------------------|------------------|------|------|

| V <sub>IN</sub>                         | Unregulated input voltage         | 7 <sup>(1)</sup> | 40   | V    |

| V <sub>ENABLE</sub>                     | Enable pin voltage <sup>(2)</sup> | 4                | 40   | V    |

| V <sub>nRST</sub> , V <sub>RDELAY</sub> | Low-voltage output range (3)      | 0                | 5.25 | V    |

| I <sub>OUT</sub>                        | Output current                    | 0                | 300  | mA   |

| T <sub>A</sub>                          | Operating ambient temperature     | -40              | 150  | °C   |

<sup>(1)</sup>  $V_{IN}$  can go down to 4 V for 130 ms or less and remain functional. If  $V_{IN}$  is less than 7 V for longer than 130 ms, then some devices can turn off until the input voltage rises above 7 V.

Submit Documentation Feedback

Copyright © 2010–2020, Texas Instruments Incorporated

<sup>(2)</sup> Absolute maximum voltage for duration less than 480 ms

Applicable for the TPS7A61-Q1 only.

<sup>(3)</sup> Applicable for the TPS7A60-Q1 only.

#### 7.4 Thermal Information

|                      | (4)(9)                                       | TPS7A60-Q1,<br>TPS7A61-Q1 | TPS7A60-Q1   |      |

|----------------------|----------------------------------------------|---------------------------|--------------|------|

|                      | THERMAL METRIC <sup>(1)(2)</sup>             | KVU (TO-252)              | KTT (TO-263) | UNIT |

|                      |                                              | 5 PINS                    | 5 PINS       |      |

| $R_{\theta JA}$      | Junction-to-ambient thermal resistance       | 26.9                      | 24.7         | °C/W |

| $R_{\theta JC(top)}$ | Junction-to-case (top) thermal resistance    | 32.2                      | 38.9         | °C/W |

| $R_{\theta JB}$      | Junction-to-board thermal resistance         | 6.5                       | 7.4          | °C/W |

| ΨЈТ                  | Junction-to-top characterization parameter   | 2.5                       | 3.8          | °C/W |

| ΨЈВ                  | Junction-to-board characterization parameter | 6.5                       | 7.4          | °C/W |

| $R_{\theta JC(bot)}$ | Junction-to-case (bottom) thermal resistance | 2.8                       | 1.5          | °C/W |

The thermal data is based on JEDEC standard high K profile JESD 51-5. The copper pad is soldered to the thermal land pattern. The correct attachment procedure must be incorporated.

#### 7.5 Electrical Characteristics

$V_{IN} = 14 \text{ V}$ .  $T_{I} = -40 ^{\circ}\text{C}$  to 150  $^{\circ}\text{C}$  (unless otherwise noted)

|                                | PARAMETER                     | TEST CONDITIONS                                                                                                                                 | MIN              | TYP  | MAX  | UNIT |  |

|--------------------------------|-------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|------------------|------|------|------|--|

| INPUT VOLTA                    | AGE (VIN PIN)                 |                                                                                                                                                 |                  |      |      |      |  |

| V <sub>IN</sub>                | Input voltage                 | Fixed 5-V or 3.3-V output, I <sub>OUT</sub> = 1 mA                                                                                              | 7 <sup>(1)</sup> |      | 40   | V    |  |

| I <sub>QUIESCENT</sub>         | Quiescent current             | $V_{IN} = 8.2 \text{ V to } 18 \text{ V}, V_{ENABLE}^{(2)} = 5 \text{ V},$<br>$I_{OUT} = 0.01 \text{ mA to } 0.75 \text{ mA}$                   |                  | 25   | 40   | μΑ   |  |

| I <sub>SLEEP</sub> (2)         | Sleep or shutdown current     | $V_{IN} = 8.2 \text{ V to } 18 \text{ V}, V_{ENABLE}^{(2)} < 0.8 \text{ V}, \\ I_{OUT} = 0 \text{ mA (no load)}, T_A = 125^{\circ}\text{C}$     |                  |      | 3    | μΑ   |  |

| V <sub>IN-UVLO</sub>           | Undervoltage lockout voltage  | Ramp V <sub>IN</sub> down until output is turned OFF                                                                                            |                  | 3.16 |      | V    |  |

| V <sub>IN(POWERUP)</sub>       | Power-up voltage              | Ramp V <sub>IN</sub> up until output is turned ON                                                                                               |                  | 3.45 |      | V    |  |

| ENABLE INPU                    | JT (ENABLE PIN)               |                                                                                                                                                 |                  |      |      |      |  |

| V <sub>IL</sub> <sup>(2)</sup> | Logic input low level         |                                                                                                                                                 | 0                |      | 0.8  | V    |  |

| V <sub>IH</sub> <sup>(2)</sup> | Logic input high level        |                                                                                                                                                 | 2.5              |      | 40   | V    |  |

| REGULATED                      | OUTPUT VOLTAGE (VOUT PIN      | l)                                                                                                                                              |                  |      |      |      |  |

| V <sub>OUT</sub>               | Regulated output voltage      | Fixed V <sub>OUT</sub> value (3.3 V or 5 V as applicable), I <sub>OUT</sub> = 10 mA to 300 mA, V <sub>IN</sub> = V <sub>OUT</sub> + 1 V to 16 V | -2%              |      | 2%   |      |  |

|                                | Line regulation               | $V_{IN} = 6 \text{ V to } 28 \text{ V}, I_{OUT} = 10 \text{ mA}, V_{OUT} = 5 \text{ V}$                                                         |                  |      | 15   | mV   |  |

| $\Delta V_{\text{LINE-REG}}$   | Line regulation               | $V_{IN}$ = 6 V to 28 V, $I_{OUT}$ = 10 mA, $V_{OUT}$ = 3.3 V                                                                                    |                  |      | 20   | mV   |  |

| ۸\/                            | Load regulation               | $I_{OUT}$ = 10 mA to 300 mA, $V_{IN}$ = 14 V, $V_{OUT}$ = 5 V                                                                                   |                  |      | 25   | mV   |  |

| $\Delta V_{LOAD-REG}$          | Load regulation               | $I_{OUT}$ = 10 mA to 300 mA, $V_{IN}$ = 14 V, $V_{OUT}$ = 3.3 V                                                                                 |                  |      | 35   | mV   |  |

| V <sub>DROPOUT</sub> (3)       | Dropout voltage               | I <sub>OUT</sub> = 250 mA                                                                                                                       |                  |      | 500  | mV   |  |

| VDROPOUT` ′                    | $(V_{IN} - V_{OUT})$          | I <sub>OUT</sub> = 150 mA                                                                                                                       |                  |      | 300  | mV   |  |

| R <sub>SW</sub>                | Switch resistance             | VIN to VOUT resistance                                                                                                                          |                  |      | 2    | Ω    |  |

| I <sub>CL</sub>                | Output current limit          | V <sub>OUT</sub> = 0 V (VOUT pin is shorted to ground)                                                                                          | 350              |      | 1000 | mA   |  |

| PSRR                           |                               | $V_{\text{IN-RIPPLE}}$ = 0.5 Vpp, $I_{\text{OUT}}$ = 300 mA, frequency = 100 Hz, $V_{\text{OUT}}$ = 5 V and $V_{\text{OUT}}$ = 3.3 V            |                  | 60   |      | dB   |  |

| FORK                           | Power supply ripple rejection | $V_{\text{IN-RIPPLE}}$ = 0.5 Vpp, $I_{\text{OUT}}$ = 300 mA, frequency = 150 kHz, $V_{\text{OUT}}$ = 5 V and $V_{\text{OUT}}$ = 3.3 V           | 30               |      |      | uБ   |  |

| RESET (nRST                    | PIN)                          |                                                                                                                                                 |                  |      |      |      |  |

| V <sub>OL</sub>                | Reset pulled low              | I <sub>OL</sub> = 5 mA                                                                                                                          |                  |      | 0.4  | V    |  |

| I <sub>ОН</sub>                | Leakage current               | Reset pulled to VOUT through 5-kΩ resistor                                                                                                      |                  |      | 1    | μA   |  |

|                                |                               |                                                                                                                                                 |                  |      |      |      |  |

<sup>(1)</sup> V<sub>IN</sub> can go down to 4 V for 130 ms or less and remain functional. If V<sub>IN</sub> is less than 7 V for longer than 130 ms, then some devices can turn off until the input voltage rises above 7 V.

(2) Applicable for the TPS7A61-Q1 only.

Copyright © 2010–2020, Texas Instruments Incorporated

Submit Documentation Feedback

For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report.

This test is done with V<sub>OUT</sub> in regulation and V<sub>IN</sub> – V<sub>OUT</sub> parameter is measured when V<sub>OUT</sub> (3.3 V or 5 V) drops by 100 mV at specified

#### **Electrical Characteristics (continued)**

$V_{IN} = 14 \text{ V}$ .  $T_{I} = -40 ^{\circ}\text{C}$  to 150  $^{\circ}\text{C}$  (unless otherwise noted)

|                                 | PARAMETER                           | TEST CONDITIONS                                                                           | MIN  | TYP  | MAX  | UNIT |

|---------------------------------|-------------------------------------|-------------------------------------------------------------------------------------------|------|------|------|------|

| V                               | Power-on-reset threshold            | $V_{OUT}$ power up above internally set tolerance, $V_{OUT} = 5 \text{ V}$                | 4.5  | 4.65 | 4.77 | V    |

| V <sub>TH(POR)</sub>            | Power-on-reset tilleshold           | $V_{OUT}$ power up above internally set tolerance, $V_{OUT} = 3.3 \text{ V}$              |      | 3.07 |      | V    |

| 111/                            | Reset threshold                     | $V_{OUT}$ falling below internally set tolerance, $V_{OUT} = 5 \text{ V}$                 | 4.5  | 4.65 | 4.77 | V    |

| UV <sub>THRES</sub>             | Reset threshold                     | $V_{\text{OUT}}$ falling below internally set tolerance, $V_{\text{OUT}} = 3.3 \text{ V}$ |      | 3.07 |      | V    |

| RESET DELAY                     | Y (RDELAY PIN)                      |                                                                                           |      |      |      |      |

| V <sub>TH(RDELAY)</sub> (4)     | Threshold to release nRST high      | Voltage at RDELAY pin is ramped up.                                                       |      | 3    | 3.3  | V    |

| I <sub>DLY</sub> <sup>(4)</sup> | Delay capacitor charging current    |                                                                                           | 0.75 | 1    | 1.25 | μA   |

| I <sub>OL</sub> <sup>(4)</sup>  | Delay capacitor discharging current | Voltage at RDELAY pin = 1 V                                                               | 5    |      |      | mA   |

| OPERATING 1                     | EMPERATURE RANGE                    |                                                                                           |      |      |      |      |

| T <sub>J</sub>                  | Operating junction temperature      |                                                                                           | -40  |      | 150  | °C   |

| T <sub>SHUTDOWN</sub>           | Thermal shutdown trip point         |                                                                                           |      | 165  |      | °C   |

| T <sub>HYST</sub>               | Thermal shutdown hysteresis         |                                                                                           |      | 10   |      | ٥C   |

<sup>(4)</sup> Applicable for the TPS7A60-Q1 only.

#### 7.6 Switching Characteristics

over operating free-air temperature range (unless otherwise noted)

|                         | PARAMETER                                  | TEST CONDITIONS                                                                                           | MIN | TYP | MAX | UNIT |  |  |  |  |

|-------------------------|--------------------------------------------|-----------------------------------------------------------------------------------------------------------|-----|-----|-----|------|--|--|--|--|

| RESET (nRST PIN)        |                                            |                                                                                                           |     |     |     |      |  |  |  |  |

| t <sub>POR</sub>        | Dower on react delay                       | C <sub>DLY</sub> = 100 pF                                                                                 |     | 300 |     | μs   |  |  |  |  |

|                         | Power-on-reset delay                       | C <sub>DLY</sub> = 100 nF                                                                                 |     | 300 |     | ms   |  |  |  |  |

| t <sub>POR-PRESET</sub> | Internally preset power-on-<br>reset delay | $C_{DLY}$ not connected in TPS7A60xx or not available in TPS7A61xx, $V_{OUT}$ = 5 V and $V_{OUT}$ = 3.3 V |     | 250 |     | μs   |  |  |  |  |

| t <sub>DEGLITCH</sub>   | Reset deglitch time                        |                                                                                                           |     | 5.5 |     | μs   |  |  |  |  |

Submit Documentation Feedback

Copyright © 2010–2020, Texas Instruments Incorporated

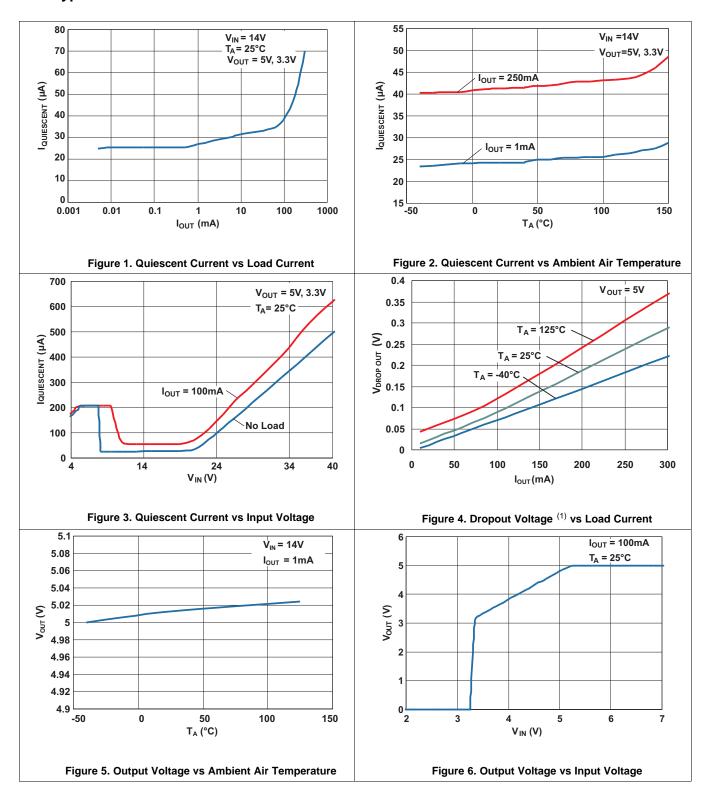

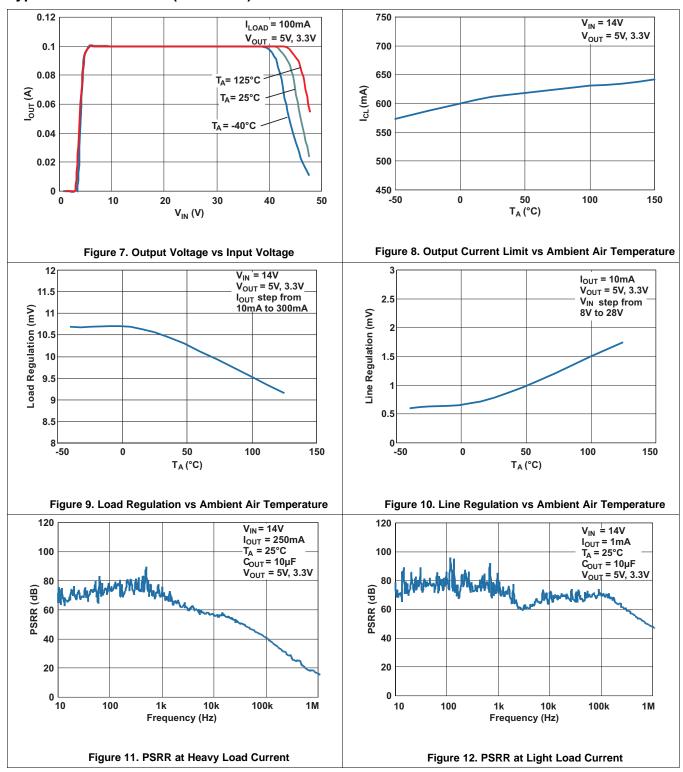

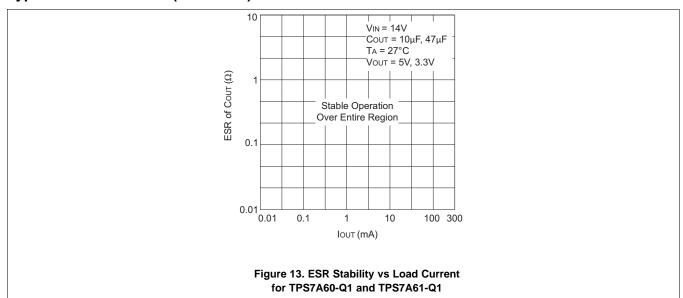

#### 7.7 Typical Characteristics

<sup>(1)</sup> Dropout voltage is measured when the output voltage drops by 100 mV from the regulated output voltage level. (For example, dropout voltage for the TPS7A6050-Q1 is measured when the output voltage drops down to 4.9 V from 5 V.)

Submit Documentation Feedback

# TEXAS INSTRUMENTS

#### **Typical Characteristics (continued)**

# **Typical Characteristics (continued)**

Submit Documentation Feedback

#### 8 Detailed Description

#### 8.1 Overview

The TPS7A60-Q1 and TPS7A61-Q1 devices comprise a family of monolithic low-dropout linear voltage regulators with integrated reset functionality. These voltage regulators are designed for low power consumption and quiescent current less than 25 µA in light-load applications. These devices are well-suited in power supplies for microprocessors and microcontrollers because of an integrated reset delay, also called power-on-reset delay.

These devices are available in two fixed output-voltage (3.3-V and 5-V) versions as follows:

- Programmable reset delay version (TPS7A60-Q1)

- Enable version (TPS7A61-Q1)

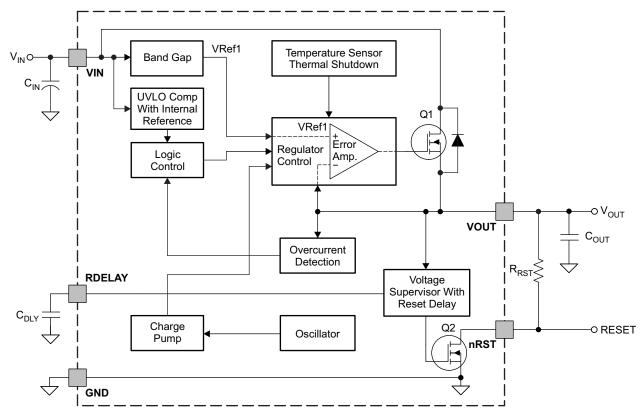

#### 8.2 Functional Block Diagrams

Figure 14. TPS7A60-Q1 Functional Block Diagram

Submit Documentation Feedback

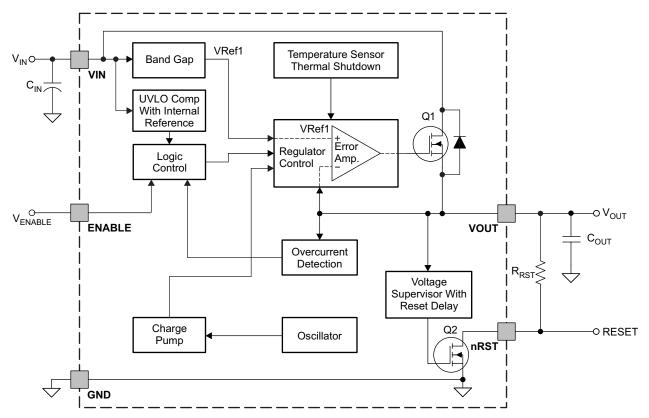

#### **Functional Block Diagrams (continued)**

Figure 15. TPS7A61-Q1 Functional Block Diagram

#### 8.3 Feature Description

The following section describes the features of TPS7A60-Q1 and TPS7A61-Q1 voltage regulators in detail.

#### 8.3.1 Reset Delay and Reset Output

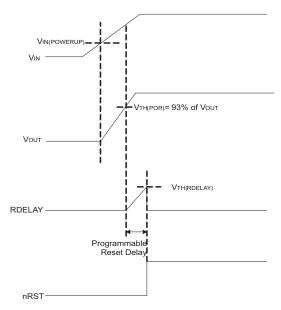

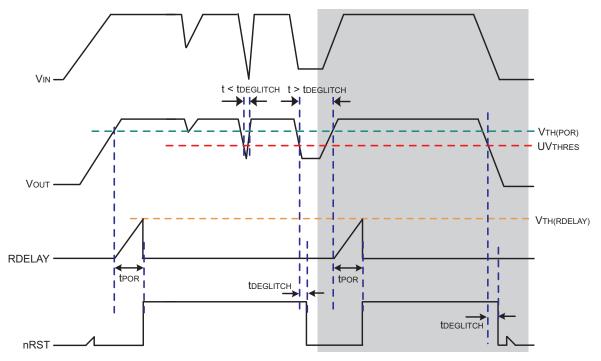

Reset delay is implemented when the device starts up to indicate that output voltage is stable and in regulation, and also when the output recovers from a negative voltage spike due to a load step or a dip in the input voltage for a specified duration. The reset-delay timer is initialized when the voltage at the output  $(V_{OUT})$  exceeds 93% of the regulated output voltage (3.3 V or 5 V, as applicable). The reset output (nRST) is asserted high after the power-on-reset delay  $(t_{POR})$  has elapsed. If the regulated output voltage falls below 93% of the set level, nRST is asserted low after a short de-glitch time of approximately 5.5  $\mu$ s (typical).

For TPS7A60-Q1 devices, the reset-delay time can be programmed by connecting an external capacitor ( $C_{DLY}$ ) to the RDELAY pin. The delay time is given by Equation 1:

$$t_{POR} = \frac{C_{DLY} \times 3}{1 \times 10^{-6}}$$

where

t<sub>POR</sub> = reset delay time in seconds

• C<sub>DLY</sub> = reset delay capacitor value in farads, 100 pF to 100 nF (1)

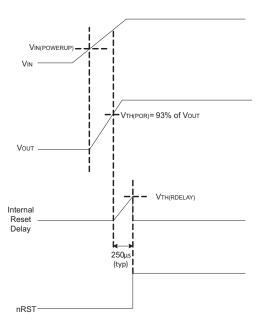

In TPS7A61xx devices, there is no RDELAY pin, and the reset-delay time is preset internally (250 µs typical).

#### **Feature Description (continued)**

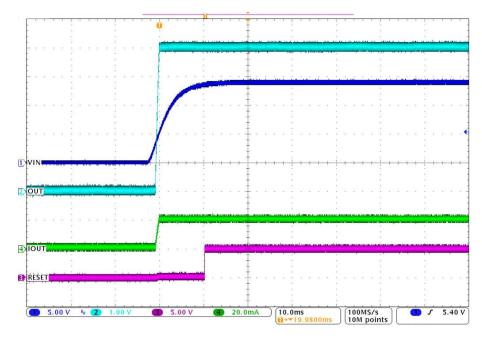

During power up, the regulator incorporates a protection scheme to limit the current through the pass element and output capacitor. When the input voltage exceeds a certain threshold  $(V_{IN(POWERUP)})$  level, the output voltage begins to ramp as shown in Figure 16 and Figure 17. When the output voltage reaches the power-on-reset threshold  $(V_{TH(POR)})$  level, a constant output current charges an external capacitor  $(C_{DLY})$  to an internal threshold  $(V_{TH(RDELAY)})$  voltage level. Then, nRST is asserted high and  $C_{DLY}$  is discharged through an internal load. This allows  $C_{DLY}$  to charge from approximately 0 V during the next power cycle. If no external capacitor is connected, the delay time is preset internally. This is shown in Figure 16.

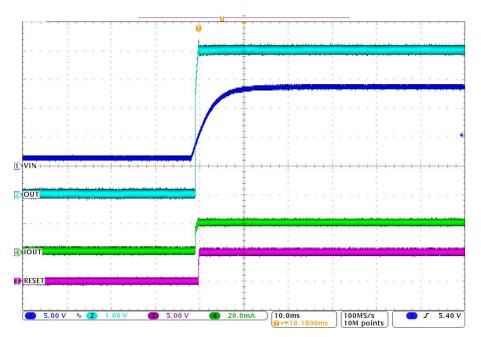

In TPS7A60-Q1 devices, if the  $C_{DLY}$  capacitor is not connected to the RDELAY pin, the reset-delay time is set internally. This is shown in Figure 17.

Figure 16. Power Up and Reset-Delay Function With the C<sub>DLY</sub> Capacitor Connected to the RDELAY Pin for TPS7A60-Q1

Figure 17. Power Up and Reset Delay Function With the C<sub>DLY</sub> Capacitor Not Connected or Available in TPS7A60-Q1 and TPS7A61-Q1, Respectively

Product Folder Links: TPS7A60-Q1 TPS7A61-Q1

#### **Feature Description (continued)**

In case of negative transients in the input voltage  $(V_{IN})$ , the reset signal is asserted low only if the output  $(V_{OUT})$  drops and stays below the reset threshold level  $(V_{TH(POR)})$  for more than the de-glitch time  $(t_{DEGLITCH})$ . This is shown in Figure 18.

While nRST is low, if the input voltage returns to the nominal operating voltage, the normal power-up sequence is followed. nRST is asserted high, only if the output voltage exceeds the reset-threshold voltage  $(V_{TH(POR)})$  and the reset-delay time  $(t_{POR})$  has elapsed. This is shown in the shaded region of Figure 18.

Figure 18. Conditions for Activation of Reset

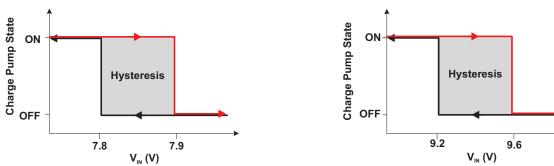

#### 8.3.2 Charge Pump Operation

These devices have an internal charge pump which turns on or off depending on the input voltage and the output current. The charge-pump switching circuitry does not cause conducted emissions to exceed required thresholds on the input-voltage line. For a given output current, the charge pump stays on at lower input voltages and turns off at higher input voltages. The charge-pump switching thresholds are hysteretic. Figure 19 and Figure 20 show typical switching thresholds for the charge pump at light ( $I_{OUT}$  < approximately 2 mA) and heavy ( $I_{OUT}$  > approximately 2 mA) loads, respectively.

Figure 19. Charge Pump Operation at Light Loads Figure 20. Charge Pump Operation at Heavy Loads

#### **Feature Description (continued)**

#### 8.3.3 Undervoltage Shutdown

These devices have an integrated undervoltage lockout (UVLO) circuit to shut down the output if the input voltage ( $V_{IN}$ ) falls below an internally fixed UVLO threshold level ( $V_{IN-UVLO}$ ). This ensures that the regulator is not latched into an unknown state during low-input-voltage conditions. The regulator powers up when the input voltage exceeds the  $V_{IN(POWERUP)}$  level.

#### 8.3.4 Low-Voltage Tracking

At low input voltages, the regulator drops out of regulation, and the output voltage tracks the input minus a voltage based on the load current ( $I_{OUT}$ ) and switch resistance ( $R_{SW}$ ). This allows for a smaller input capacitor and can possibly eliminate the need of using a boost converter during cold-crank conditions.

#### 8.3.5 Integrated Fault Protection

These devices feature integrated fault protection to make them ideal for use in automotive applications. In order to keep them in a safe area of operation during certain fault conditions, internal current-limit protection and current-limit foldback are used to limit the maximum output current. This protects them from excessive power dissipation. For example, during a short-circuit condition on the output, current through the pass element is limited to  $I_{Cl}$  to protect the device from excessive power dissipation.

#### 8.3.6 Thermal Shutdown

These devices incorporate a thermal shutdown (TSD) circuit as a protection from overheating. For continuous normal operation, the junction temperature should not exceed the TSD trip point. If the junction temperature exceeds the TSD trip point, the output is turned off. When the junction temperature falls below the TSD trip point, the output is turned on again. This is shown in Figure 21.

Figure 21. Thermal Cycling Waveform for the TPS7A6150-Q1

Submit Documentation Feedback

Copyright © 2010-2020, Texas Instruments Incorporated

#### 8.4 Device Functional Modes

#### 8.4.1 Low-Power Mode

At light loads and high input voltages ( $V_{IN}$  > approximately 8 V such that charge pump is off), the device operates in low-power mode and the quiescent current consumption is reduced to 25  $\mu$ A (typical) as shown in Table 1.

**Table 1. Typical Quiescent Current Consumption**

| l <sub>out</sub>                                   | CHARGE PUMP ON | CHARGE PUMP OFF        |

|----------------------------------------------------|----------------|------------------------|

| I <sub>OUT</sub> < approximately 2 mA (light load) | 250 μΑ         | 25 μA (low-power mode) |

| I <sub>OUT</sub> > approximately 2 mA (heavy load) | 280 μΑ         | 70 μA                  |

#### 8.4.2 Sleep Mode (TPS7A61-Q1 Only)

The enable falling edge is 0.8 V (minimum). The device operates in the sleep mode by holding the ENABLE pin below that voltage, and the quiescent current consumption is reduced to 3  $\mu$ A (maximum) as shown in *Electrical Characteristics*.

#### 8.4.3 Regulation Mode

When the input voltage is above 7 V, with the ENABLE pin pulled higher than 2.5 V, the device operates in regulation mode and outputs the nominal voltage.

Product Folder Links: TPS7A60-Q1 TPS7A61-Q1

#### 9 Application and Implementation

#### NOTE

Information in the following applications sections is not part of the TI component specification, and TI does not warrant its accuracy or completeness. TI's customers are responsible for determining suitability of components for their purposes. Customers should validate and test their design implementation to confirm system functionality.

#### 9.1 Application Information

The TPS7A60-Q1 and TPS7A61-Q1 devices are 300-mA low-dropout linear regulators designed for up to 40-V  $_{\text{IN}}$  operation with only 25- $\mu$ A quiescent current at no load. There are specific EVMs designed for these devices to enable evaluation of all the functions of the devices. Both the EVM and its user guide are available on the product folder as well.

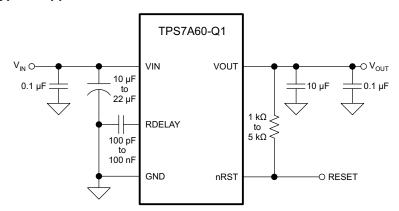

#### 9.2 Typical Applications

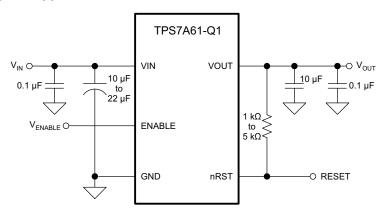

Figure 22 and Figure 24 show typical application circuits for the TPS7A60-Q1 and TPS7A61-Q1, respectively. One may use different values of external components, depending on the end application. An application may require a larger output capacitor during fast load steps in order to prevent reset from occurring. TI recommends a low-ESR ceramic capacitor with dielectric of type X5R or X7R.

#### 9.2.1 TPS7A60-Q1 Typical Application

Figure 22. Typical Application Schematic for the TPS7A60-Q1 Device

#### 9.2.1.1 Design Requirements

For this design example, use the parameters listed in Table 2.

Table 2. TPS7A60-Q1 Design Parameters

| DESIGN PARAMETER            | EXAMPLE VALUE                                      |  |  |  |  |  |

|-----------------------------|----------------------------------------------------|--|--|--|--|--|

| Input voltage range         | 7 V to 40 V                                        |  |  |  |  |  |

| Output voltage              | 3.3 V (for TPS7A6033-Q1) or 5 V (for TPS7A6050-Q1) |  |  |  |  |  |

| Output current rating       | 300 mA                                             |  |  |  |  |  |

| Output capacitor range      | 10 μF to 47 μF                                     |  |  |  |  |  |

| Output-capacitor ESR range  | 10 m $\Omega$ to 10 $\Omega$                       |  |  |  |  |  |

| RESET-delay capacitor range | 100 pF to 100 nF                                   |  |  |  |  |  |

Submit Documentation Feedback

Copyright © 2010–2020, Texas Instruments Incorporated

#### 9.2.1.2 Detailed Design Procedure

To begin the design process, determine the following:

- Input voltage range

- Output voltage

- Output current rating

- · Input capacitor

- · Output capacitor

#### 9.2.1.2.1 Input Capacitor

The device requires an input bypass capacitor, the value of which depends on the application. The typical recommended value for the bypass capacitor is 10  $\mu$ F. The voltage rating must be greater than the maximum input voltage.

#### 9.2.1.2.2 Output Capacitor

The device requires an output capacitor to stabilize the output voltage. TI recommends to selecting a capacitor between 10  $\mu$ F and 47  $\mu$ F with ESR range from 10 m $\Omega$  to 10  $\Omega$ .

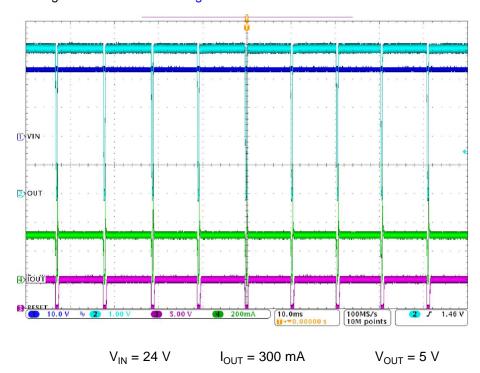

#### 9.2.1.3 Application Curve

Figure 23. Power Up ( $V_{OUT} = 5 \text{ V}$ ) With 10-ms RESET Delay, 10 ms/div,  $I_L = 20 \text{ mA}$

#### 9.2.2 TPS7A61-Q1 Typical Application

Figure 24. Typical Application Schematic for the TPS7A61-Q1 Device

#### 9.2.2.1 Design Requirements

For this design example, use the parameters listed in Table 3.

Table 3. TPS7A61-Q1 Design Parameters

| DESIGN PARAMETER           | EXAMPLE VALUE                                      |  |  |  |  |  |

|----------------------------|----------------------------------------------------|--|--|--|--|--|

| Input voltage range        | 7 V to 40 V                                        |  |  |  |  |  |

| Output voltage             | 3.3 V (for TPS7A6133-Q1) or 5 V (for TPS7A6150-Q1) |  |  |  |  |  |

| Output current rating      | 300 mA                                             |  |  |  |  |  |

| Output capacitor range     | 10 μF to 47 μF                                     |  |  |  |  |  |

| Output-capacitor ESR range | 10 m $\Omega$ to 10 $\Omega$                       |  |  |  |  |  |

#### 9.2.2.2 Detailed Design Procedure

To begin the design process, determine the following:

- Input voltage range

- Output voltage

- · Output current rating

- Input capacitor

- Output capacitor

Submit Documentation Feedback

Copyright © 2010–2020, Texas Instruments Incorporated

#### 9.2.2.3 Application Curve

Figure 25. Power Up ( $V_{OUT} = 5 \text{ V}$ ), 10 ms/div,  $I_L = 20 \text{ mA}$

#### 10 Power Supply Recommendations

Design of the device is for operation from an input voltage supply with a range between 4 V and 40 V. This input supply must be well regulated. If the input supply is located more than a few inches from the TPS7A60-Q1 or TPS7A61-Q1 device, TI recommends adding an electrolytic capacitor with a value of 22 µF and a ceramic bypass capacitor at the input.

#### 11 Layout

#### 11.1 Layout Guidelines

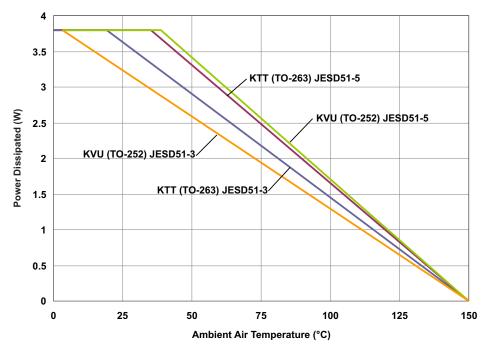

For the LDO power supply, especially these high voltage and large current ones, layout is an important step. If layout is not carefully designed, the regulator could not deliver enough output current because of the thermal limitation. To improve the thermal performance of the device, and maximize the current output at high ambient temperature, it is recommended to spread the thermal pad as large as possible and put enough thermal vias on the thermal pad. Figure 29 and Figure 30 show an example layout.

#### 11.1.1 Power Dissipation and Thermal Considerations

Power dissipated in the device can be calculated using Equation 2.

$$P_D = I_{OUT} \times (V_{IN} - V_{OUT}) + I_{QUIESCENT} \times V_{IN}$$

where

- P<sub>D</sub> = continuous power dissipation

- I<sub>OUT</sub> = output current

- V<sub>IN</sub> = input voltage

- V<sub>OUT</sub> = output voltage

• I<sub>QUIESCENT</sub> = quiescent current (2)

As IQUIESCENT << I<sub>OUT</sub>, therefore, the term I<sub>QUIESCENT</sub> × V<sub>IN</sub> in Equation 2 can be ignored.

For a device under operation at a given ambient air temperature (T<sub>A</sub>), the junction temperature (T<sub>J</sub>) can be calculated using Equation 3.

$$T_{J} = T_{A} + (R_{\theta JA} \times P_{D})$$

where

$R_{\theta JA}$  = junction-to-ambient-air thermal impedance (3)

Submit Documentation Feedback

#### **Layout Guidelines (continued)**

The rise in junction temperature due to power dissipation can be calculated using Equation 4.

$$\Delta T = T_J - T_A = (R_{\theta JA} \times P_D) \tag{4}$$

For a given maximum junction temperature  $(T_{J-Max})$ , the maximum ambient air temperature  $(T_{A-Max})$  at which the device can operate can be calculated using Equation 5.

$$T_{A-Max} = T_{J-Max} - (R_{\theta JA} \times P_D)$$

(5)

#### Example:

If  $I_{OUT}$  = 100 mA,  $V_{OUT}$  = 5 V,  $V_{IN}$  = 14 V,  $I_{QUIESCENT}$  = 250  $\mu$ A and  $R_{\theta JA}$ = 30°C/W, the continuous power dissipated in the device is 0.9 W. The rise in junction temperature due to power dissipation is 27°C. For a maximum junction temperature of 150°C, maximum ambient air temperature at which the device can operate is 123°C.

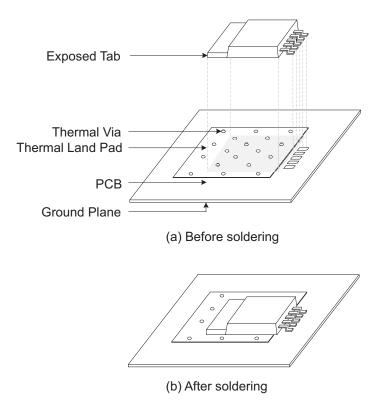

For adequate heat dissipation, it is recommended to solder the thermal pad (exposed heat sink) to a thermal land pad on the PCB. Doing this provides a heat conduction path from the die to the PCB and reduces overall package thermal resistance. Power derating curves for the TPS7A60-Q1 and TPS7A61-Q1 family of devices in the KTT (TO-263) and KVU (TO-252) packages are shown in Figure 26.

Figure 26. Power Derating Curves

For optimum thermal performance, TI recommends to use a high-K PCB with thermal vias between the ground plane and solder pad or thermal land pad. This is shown in Figure 27 (a) and (b). Further, the heat-spreading capabilities of a PCB can be considerably improved by using a thicker ground plane and a thermal land pad with a larger surface area.

#### **Layout Guidelines (continued)**

Figure 27. Using Multilayer PCB and Thermal Vias For Adequate Heat Dissipation

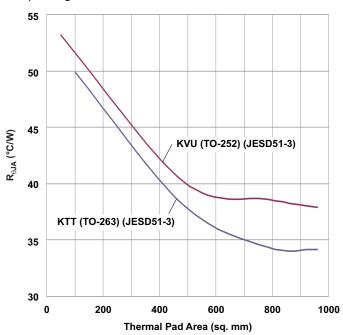

Keeping other factors constant, surface area of the thermal land pad contributes to heat dissipation only to a certain extent. Figure 28 shows the variation of  $R_{\theta JA}$  with surface area of the thermal land pad (soldered to the exposed pad) for KTT and KVU packages.

Figure 28.  $R_{\theta JA}$  vs Thermal Pad Area

Submit Documentation Feedback

Copyright © 2010–2020, Texas Instruments Incorporated

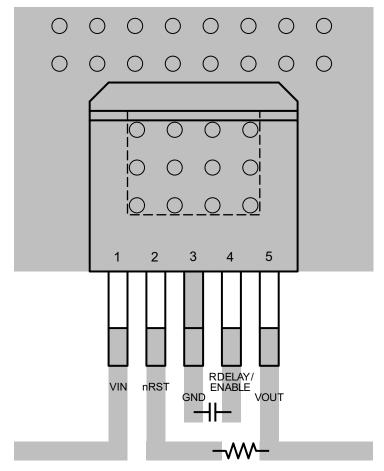

#### 11.2 Layout Examples

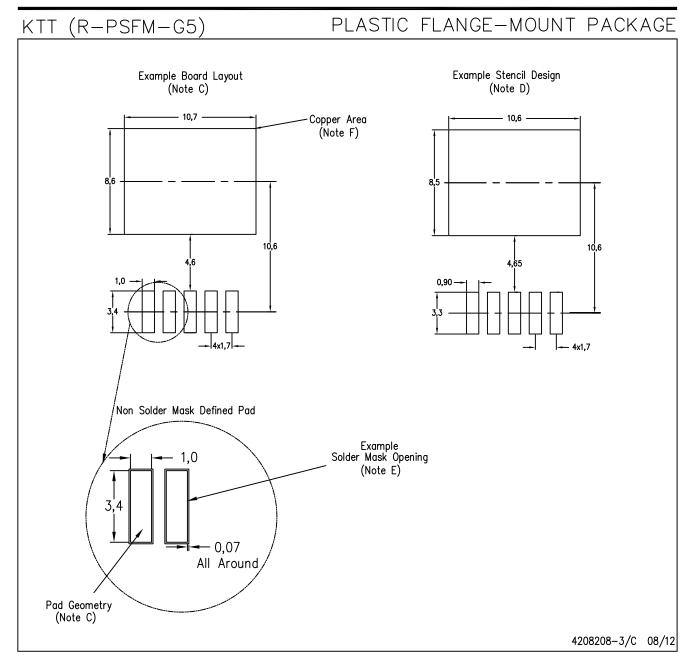

Figure 29. Layout Recommendation for 5-Pin KTT Package

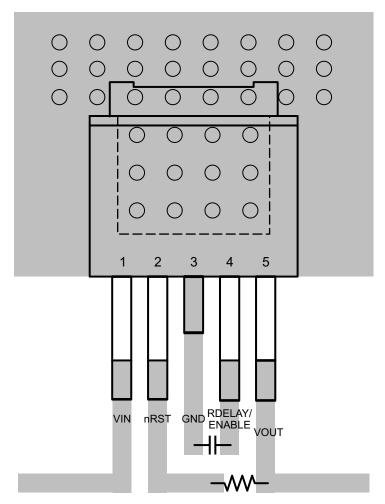

#### **Layout Examples (continued)**

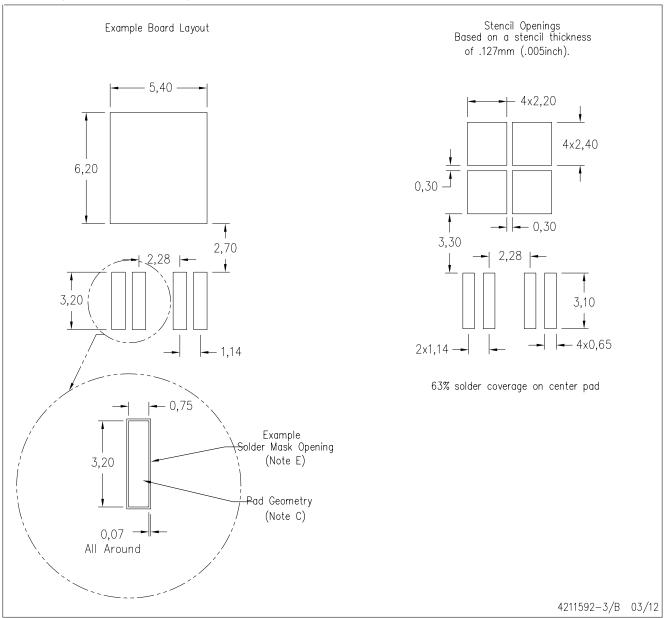

Figure 30. Layout Recommendation for 5-pin KVU package

#### 12 Device and Documentation Support

#### 12.1 Related Links

The table below lists quick access links. Categories include technical documents, support and community resources, tools and software, and quick access to order now.

**Table 4. Related Links**

| PARTS      | PRODUCT FOLDER | PRODUCT FOLDER ORDER NOW TECHNICAL DOCUMENTS |            | TOOLS &<br>SOFTWARE | SUPPORT & COMMUNITY |

|------------|----------------|----------------------------------------------|------------|---------------------|---------------------|

| TPS7A60-Q1 | Click here     | Click here                                   | Click here | Click here          | Click here          |

| TPS7A61-Q1 | Click here     | Click here                                   | Click here | Click here          | Click here          |

#### 12.2 Receiving Notification of Documentation Updates

To receive notification of documentation updates, navigate to the device product folder on ti.com. In the upper right corner, click on *Alert me* to register and receive a weekly digest of any product information that has changed. For change details, review the revision history included in any revised document.

#### 12.3 Community Resources

TI E2E™ support forums are an engineer's go-to source for fast, verified answers and design help — straight from the experts. Search existing answers or ask your own question to get the quick design help you need.

Linked content is provided "AS IS" by the respective contributors. They do not constitute TI specifications and do not necessarily reflect TI's views; see TI's Terms of Use.

#### 12.4 Trademarks

E2E is a trademark of Texas Instruments.

All other trademarks are the property of their respective owners.

#### 12.5 Electrostatic Discharge Caution

This integrated circuit can be damaged by ESD. Texas Instruments recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage.

ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet its published specifications.

#### 12.6 Glossary

SLYZ022 — TI Glossary.

This glossary lists and explains terms, acronyms, and definitions.

#### 13 Mechanical, Packaging, and Orderable Information

The following pages include mechanical, packaging, and orderable information. This information is the most-current data available for the designated devices. This data is subject to change without notice and without revision of this document. For browser-based versions of this data sheet, see the left-hand navigation pane.

Copyright © 2010–2020, Texas Instruments Incorporated

Submit Documentation Feedback

#### **PACKAGING INFORMATION**

| Orderable Device | Status | Package Type     | Package<br>Drawing | Pins | Package<br>Qty | Eco Plan     | Lead finish/<br>Ball material | MSL Peak Temp (3)   |

|------------------|--------|------------------|--------------------|------|----------------|--------------|-------------------------------|---------------------|

| TPS7A6033QKTTRQ1 | ACTIVE | DDPAK/<br>TO-263 | KTT                | 5    | 500            | RoHS & Green | SN                            | Level-3-245C-168 HR |

| TPS7A6033QKVURQ1 | ACTIVE | TO-252           | KVU                | 5    | 2500           | RoHS & Green | SN                            | Level-3-260C-168 HR |

| TPS7A6050QKTTRQ1 | ACTIVE | DDPAK/<br>TO-263 | KTT                | 5    | 500            | RoHS & Green | SN                            | Level-3-245C-168 HR |

| TPS7A6050QKVURQ1 | ACTIVE | TO-252           | KVU                | 5    | 2500           | RoHS & Green | SN                            | Level-3-260C-168 HR |

| TPS7A6133QKVURQ1 | ACTIVE | TO-252           | KVU                | 5    | 2500           | RoHS & Green | SN                            | Level-3-260C-168 HR |

| TPS7A6150QKVURQ1 | ACTIVE | TO-252           | KVU                | 5    | 2500           | RoHS & Green | SN                            | Level-3-260C-168 HR |

(1) The marketing status values are defined as follows:

**ACTIVE:** Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

PREVIEW: Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

(2) RoHS: TI defines "RoHS" to mean semiconductor products that are compliant with the current EU RoHS requirements for all 10 RoHS substances, including to not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, "RoHS" products are suitable for use in spreference these types of products as "Pb-Free".

RoHS Exempt: Ti defines "RoHS Exempt" to mean products that contain lead but are compliant with EU RoHS pursuant to a specific EU RoHS exemption.

Green: Ti defines "Green" to mean the content of Chlorine (CI) and Bromine (Br) based flame retardants meet JS709B low halogen requirements of <=1000pp flame retardants must also meet the <=1000ppm threshold requirement.

- (3) MSL, Peak Temp. The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

- (4) There may be additional marking, which relates to the logo, the lot trace code information, or the environmental category on the device.

- (5) Multiple Device Markings will be inside parentheses. Only one Device Marking contained in parentheses and separated by a "~" will appear on a device. If a lin of the previous line and the two combined represent the entire Device Marking for that device.

- (6) Lead finish/Ball material Orderable Devices may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Elines if the finish value exceeds the maximum column width.

Addendum-Page 1

Important Information and Disclaimer: The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis of TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer of

# **PACKAGE MATERIALS INFORMATION**

www.ti.com 24-Apr-2020

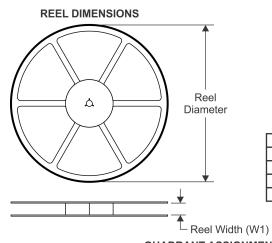

#### TAPE AND REEL INFORMATION

# TAPE DIMENSIONS KO P1 BO W Cavity AO Cavity

| Γ | A0 | Dimension designed to accommodate the component width     |

|---|----|-----------------------------------------------------------|

|   | B0 | Dimension designed to accommodate the component length    |

|   | K0 | Dimension designed to accommodate the component thickness |

|   |    | Overall width of the carrier tape                         |

|   | P1 | Pitch between successive cavity centers                   |

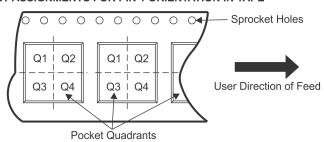

#### QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

#### \*All dimensions are nominal

| Device           | Package<br>Type  | Package<br>Drawing |   | SPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|------------------|------------------|--------------------|---|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| TPS7A6033QKTTRQ1 | DDPAK/<br>TO-263 | KTT                | 5 | 500  | 330.0                    | 24.4                     | 10.6       | 15.8       | 4.9        | 16.0       | 24.0      | Q2               |

| TPS7A6033QKVURQ1 | TO-252           | KVU                | 5 | 2500 | 330.0                    | 16.4                     | 6.9        | 10.5       | 2.7        | 8.0        | 16.0      | Q2               |

| TPS7A6050QKTTRQ1 | DDPAK/<br>TO-263 | KTT                | 5 | 500  | 330.0                    | 24.4                     | 10.6       | 15.8       | 4.9        | 16.0       | 24.0      | Q2               |

| TPS7A6050QKVURQ1 | TO-252           | KVU                | 5 | 2500 | 330.0                    | 16.4                     | 6.9        | 10.5       | 2.7        | 8.0        | 16.0      | Q2               |

| TPS7A6133QKVURQ1 | TO-252           | KVU                | 5 | 2500 | 330.0                    | 16.4                     | 6.9        | 10.5       | 2.7        | 8.0        | 16.0      | Q2               |

| TPS7A6150QKVURQ1 | TO-252           | KVU                | 5 | 2500 | 330.0                    | 16.4                     | 6.9        | 10.5       | 2.7        | 8.0        | 16.0      | Q2               |

# PACKAGE MATERIALS INFORMATION

www.ti.com 24-Apr-2020

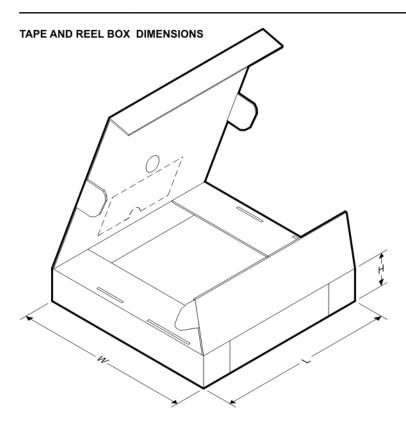

#### \*All dimensions are nominal

| Device           | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|------------------|--------------|-----------------|------|------|-------------|------------|-------------|

| TPS7A6033QKTTRQ1 | DDPAK/TO-263 | KTT             | 5    | 500  | 340.0       | 340.0      | 38.0        |

| TPS7A6033QKVURQ1 | TO-252       | KVU             | 5    | 2500 | 340.0       | 340.0      | 38.0        |

| TPS7A6050QKTTRQ1 | DDPAK/TO-263 | KTT             | 5    | 500  | 340.0       | 340.0      | 38.0        |

| TPS7A6050QKVURQ1 | TO-252       | KVU             | 5    | 2500 | 340.0       | 340.0      | 38.0        |

| TPS7A6133QKVURQ1 | TO-252       | KVU             | 5    | 2500 | 340.0       | 340.0      | 38.0        |

| TPS7A6150QKVURQ1 | TO-252       | KVU             | 5    | 2500 | 340.0       | 340.0      | 38.0        |

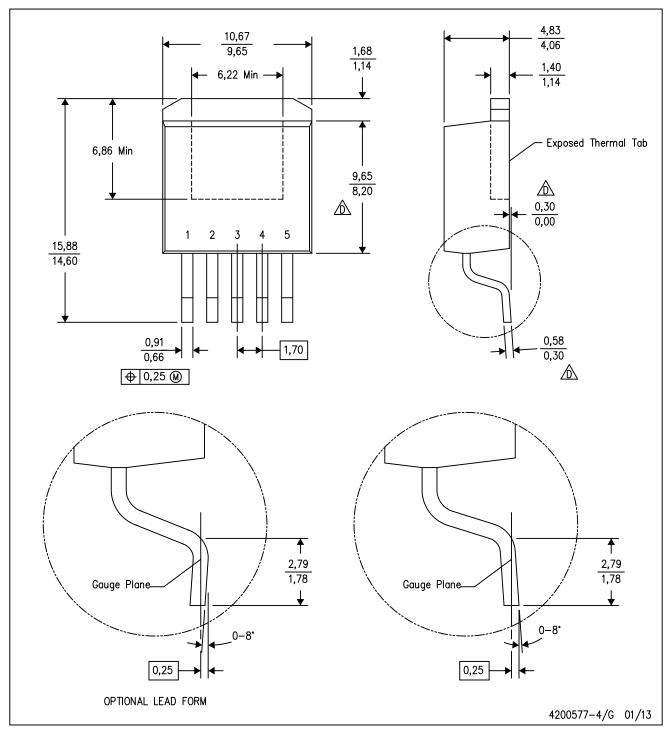

# KTT (R-PSFM-G5)

# PLASTIC FLANGE-MOUNT PACKAGE

NOTES:

- A. All linear dimensions are in millimeters.

- B. This drawing is subject to change without notice.

- C. Body dimensions do not include mold flash or protrusion. Mold flash or protrusion not to exceed 0.005 (0,13) per side.

- Falls within JEDEC TO—263 variation BA, except minimum lead thickness, maximum seating height, and minimum body length.

NOTES: A. All linear dimensions are in millimeters.

- B. This drawing is subject to change without notice.

- C. Publication IPC-SM-782 is recommended for alternate designs.

- D. Laser cutting apertures with trapezoidal walls and also rounding corners will offer better paste release.

Customers should contact their board assembly site for stencil design recommendations. Refer to IPC-7525.

- E. Customers should contact their board fabrication site for solder mask tolerances between and around signal pads.

- F. This package is designed to be soldered to a thermal pad on the board. Refer to the Product Datasheet for specific thermal information, via requirements, and recommended thermal pad size. For thermal pad sizes larger than shown a solder mask defined pad is recommended in order to maintain the solderable pad geometry while increasing copper area.

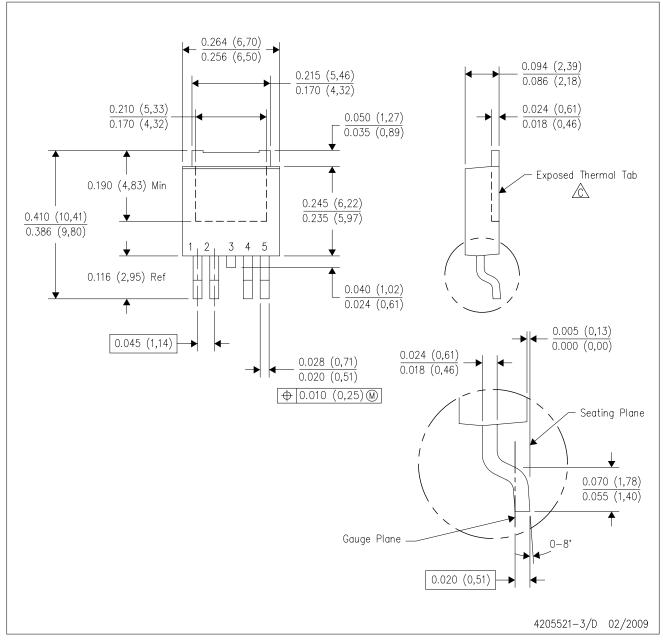

# KVU (R-PSFM-G5)

# PLASTIC FLANGE-MOUNT PACKAGE

NOTES:

- A. All linear dimensions are in inches (millimeters).

- B. This drawing is subject to change without notice.

- The center lead is in electrical contact with the exposed thermal tab.

- D. Body Dimensions do not include mold flash or protrusions. Mold flash and protrusion shall not exceed 0.006 (0,15) per side.

- E. Falls within JEDEC TO-252 variation AD.

# KVU (R-PSFM-G5)

# PLASTIC FLANGE MOUNT PACKAGE

NOTES:

- A. All linear dimensions are in millimeters.

- B. This drawing is subject to change without notice.

- C. Publication IPC-SM-782 is an alternate information source for PCB land pattern designs.

- D. Laser cutting apertures with trapezoidal walls and also rounding corners will offer better paste release. Customers should contact their board assembly site for stencil design recommendations. Refer to IPC—7525 for other stencil recommendations.

- E. Customers should contact their board fabrication site for recommended solder mask tolerances and via tenting recommendations for vias placed in thermal pad.

#### **IMPORTANT NOTICE AND DISCLAIMER**

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, or other requirements. These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

Tl's products are provided subject to Tl's Terms of Sale (<a href="www.ti.com/legal/termsofsale.html">www.ti.com/legal/termsofsale.html</a>) or other applicable terms available either on ti.com or provided in conjunction with such Tl products. Tl's provision of these resources does not expand or otherwise alter Tl's applicable warranties or warranty disclaimers for Tl products.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2020, Texas Instruments Incorporated