Click to view price, real time Inventory, Delivery & Lifecycle Information ;

# DS125DF1610FB/NOPB

## Texas instruments

Interface - Signal Buffers, Repeaters 16 Channel Retimer

Any questions, please feel free to contact us. info@kaimte.com

## DS125DF1610

SNLS482B - APRIL 2014 - REVISED JANUARY 2017

## DS125DF1610 9.8 to 12.5 Gbps 16-Channel Retimer

## 1 Features

Texas

• Pin-Compatible Family

**INSTRUMENTS**

- DS150DF1610: 12.5 to 15 G

- DS125DF1610: 9.8 to 12.5 G

- DS110DF1610: 8.5 to 11.3 G

- 4x4 Analog Cross Point Switch for Each Quad

- Fully Adaptive CTLE

- Self tuning DFE, with Optional Continuous Adaption

- Configurable VGA

- Adjustable Transmit V<sub>OD</sub>

- Adjustable 3-tap Transmit FIR Filter

- On-chip AC Coupling on Receive Inputs

- Locks to Half/Quarter/Eighth Data Rates for Legacy Support

- On-chip Eye Monitor(EOM), PRBS Checker, Pattern Generator

- Supports JTAG Boundary Scan

- Programmable Output Polarity Inversion

- Input Signal Detection, CDR Lock Detection

- Single 2.5 V ±5% Power Supply

- SMBus Based Register Configuration

- Optional EEPROM Configuration

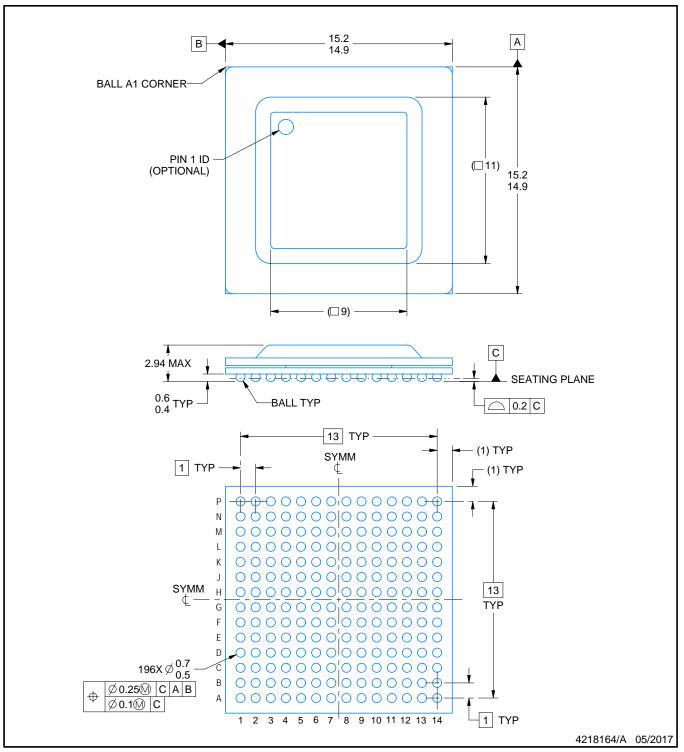

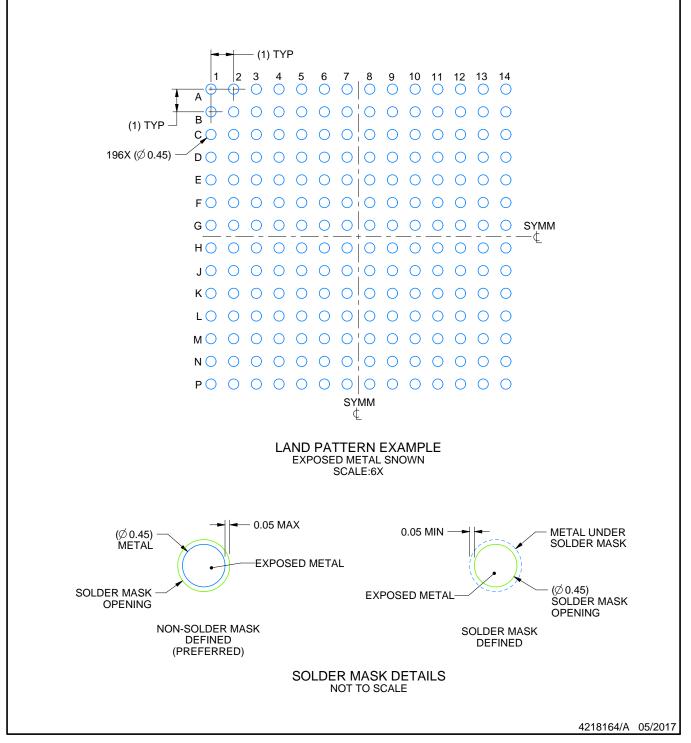

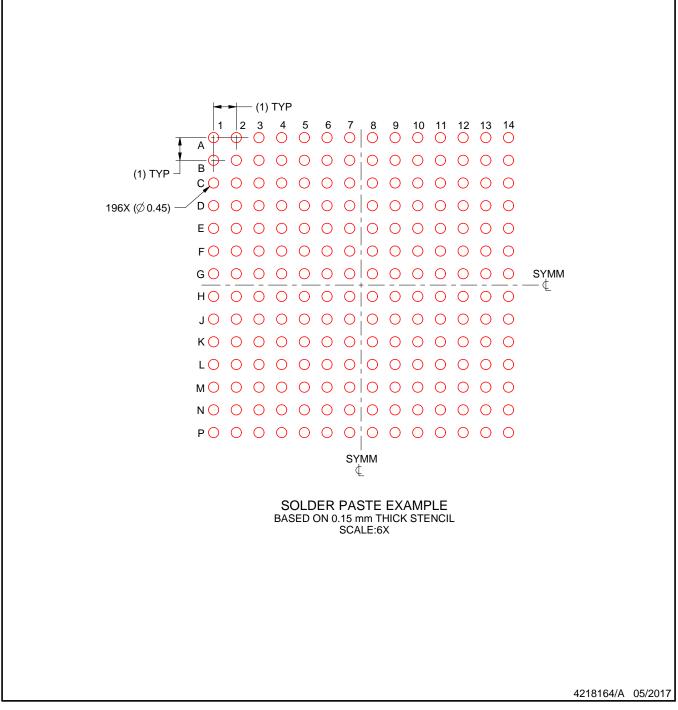

- 15 mm × 15 mm, 196-pin FCBGA Package

- Operating Temp Range : -40°C to +85°C

## 2 Applications

- SFF-8431

- CPRI

- 10G/40G Ethernet

- Backplanes

## 3 Description

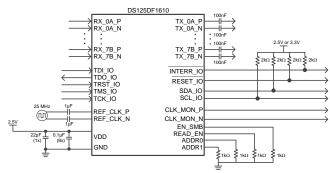

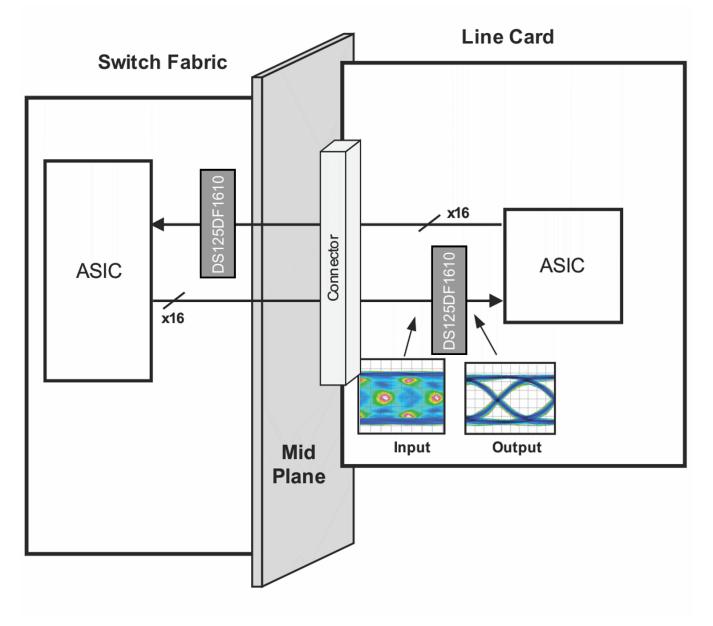

The DS125DF1610 is a sixteen-channel multi-rate retimer with integrated signal conditioning features. The device includes a fully adaptive Continuous Time Linear Equalizer (CTLE), Decision Feedback Equalizer (DFE), clock and data recovery (CDR), and a transmit FIR filter to enhance the reach and robustness over long, lossy, crosstalk impaired high speed serial links to achieve BER <  $1 \times 10^{-15}$ .

Each channel of the DS125DF1610 independently locks to serial data at 9.8 to 12.5 Gbps and the divide by 2, 4 and 8 sub-multiples. A simple external oscillator (±100ppm) that is synchronous or asynchronous with the incoming data stream is used as a reference clock. Integrated 4x4 cross point switches allow for full non-blocking routing or broadcasting within each quad of the DS125DF1610.

Programmable transmit FIR filter offers control of the pre-cursor, main tap and post-cursor for transmit equalization. The fully adaptive receive equalization (CTLE and DFE) enables longer distance transmission in lossy copper interconnects and backplanes with multiple connectors.

A non-disruptive mission mode eye-monitor feature allows link monitoring internal to the receiver. The built-in PRBS generator and checker compliment the internal diagnostic features to complete standalone BERT measurements. Built-in JTAG enables manufacturing tests.

## Device Information (1)

| PART NUMBER | PACKAGE     | BODY SIZE NOM       |

|-------------|-------------|---------------------|

| DS125DF1610 | FCBGA (196) | 15.00 mm x 15.00 mm |

(1) For all available packages, see the orderable addendum at the end of the datasheet

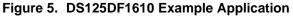

## Simplified Schematic

An IMPORTANT NOTICE at the end of this data sheet addresses availability, warranty, changes, use in safety-critical applications, intellectual property matters and other important disclaimers. PRODUCTION DATA.

DS125DF1610 SNLS482B-APRIL 2014-REVISED JANUARY 2017

1

2

7

2

## **Table of Contents**

| Features 1                           | 8 Application and Implementation 69                     |

|--------------------------------------|---------------------------------------------------------|

| Applications 1                       | 8.1 Application Information 69                          |

| Description1                         | 8.2 Typical Applications 70                             |

| Revision History2                    | 8.3 Initialization Setup 73                             |

| Pin Configuration and Functions 3    | 9 Power Supply Recommendations                          |

| Specifications                       | 9.1 Power Supply Filtering 75                           |

| 6.1 Absolute Maximum Ratings         | 10 Layout                                               |

| 6.2 Handling Ratings                 | 10.1 Layout Guidelines 75                               |

| 6.3 Recommended Operating Conditions | 10.2 Layout Example 76                                  |

| 6.4 Thermal Information              | 11 Device and Documentation Support                     |

| 6.5 Additional Thermal Information8  | 11.1 Device Support77                                   |

| 6.6 Electrical Characteristics9      | 11.2 Documentation Support                              |

| Detailed Description 13              | 11.3 Receiving Notification of Documentation Updates 77 |

| 7.1 Overview                         | 11.4 Community Resources                                |

| 7.2 Functional Block Diagram 13      | 11.5 Trademarks                                         |

| 7.3 Feature Description              | 11.6 Electrostatic Discharge Caution                    |

| 7.4 Device Functional Modes          | 11.7 Glossary 77                                        |

| 7.5 Programming                      | 12 Mechanical, Packaging, and Orderable<br>Information  |

|    | 8.1  | Application Information 69                         |

|----|------|----------------------------------------------------|

|    | 8.2  | Typical Applications 70                            |

|    | 8.3  | Initialization Setup                               |

| 9  | Pow  | er Supply Recommendations75                        |

|    | 9.1  | Power Supply Filtering 75                          |

| 10 | Lay  | out                                                |

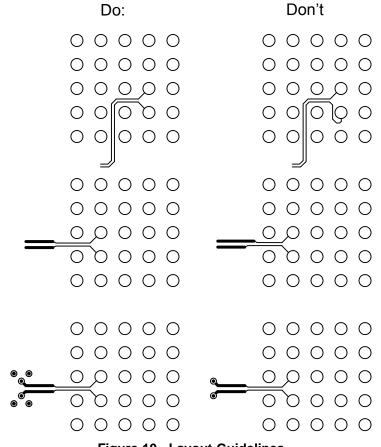

|    | 10.1 | Layout Guidelines75                                |

|    | 10.2 | Layout Example 76                                  |

| 11 | Dev  | ice and Documentation Support                      |

|    | 11.1 | Device Support77                                   |

|    | 11.2 | Documentation Support77                            |

|    | 11.3 | Receiving Notification of Documentation Updates 77 |

|    | 11.4 | Community Resources 77                             |

|    | 11.5 | Trademarks 77                                      |

|    | 11.6 | Electrostatic Discharge Caution 77                 |

|    | 11.7 | Glossary 77                                        |

| 12 |      | hanical, Packaging, and Orderable                  |

|    | Info | rmation                                            |

|    |      |                                                    |

Copyright © 2014–2017, Texas Instruments Incorporated

**4** Revision History NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

| Changes from Revision A (December 2015) to Revision B                   | Page |

|-------------------------------------------------------------------------|------|

| <ul> <li>Changed the minimum temperature from -20°C to -40°C</li> </ul> |      |

| Changed the minimum temperature from -20°C to -40°C                     |      |

| Changes from Original (April 2014) to Revision A                        | Page |

| Added full datasheet                                                    |      |

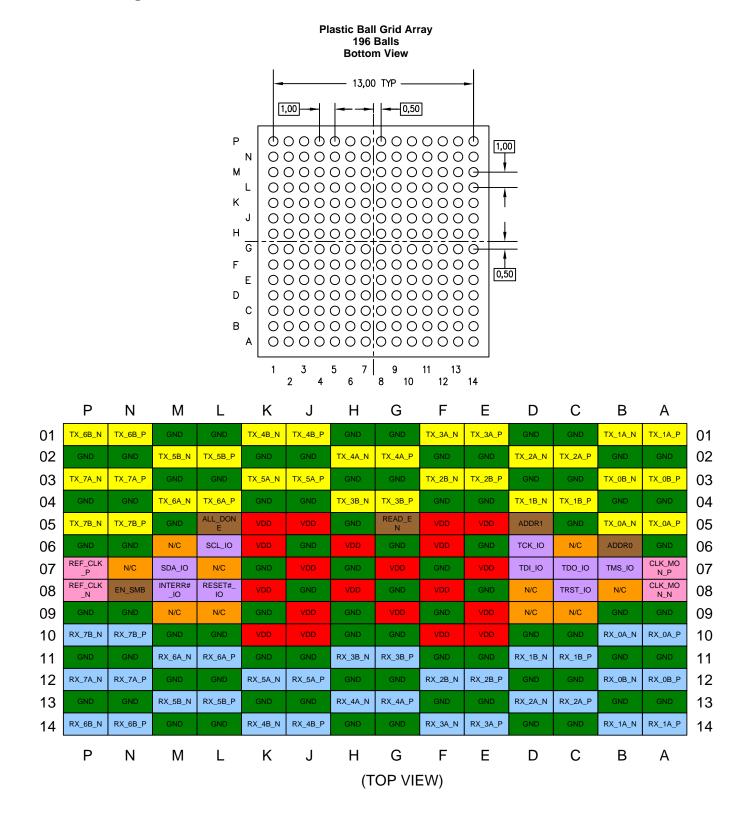

## 5 Pin Configuration and Functions

Product Folder Links: DS125DF1610

## DS125DF1610

SNLS482B-APRIL 2014-REVISED JANUARY 2017

www.ti.com

Texas Instruments

|                                         | Pin Functions           |            |        |                                                                                                                                                         |  |

|-----------------------------------------|-------------------------|------------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| DS110DF1610,<br>DS125DF1610<br>PIN NAME | DS150DF1610<br>PIN NAME | PIN        | I/O    | DESCRIPTION                                                                                                                                             |  |

| HIGH SPEED DIFF                         | ERENTIAL I/O            | 1          |        |                                                                                                                                                         |  |

| RX_1A_P<br>RX_1A_N                      | RX_0_0P<br>RX_0_0N      | A14<br>B14 | I, CML | Inverting and non-inverting CML-compatible, AC coupled differential inputs. An on-chip 100 Ohm differential termination resistor connects these inputs. |  |

| RX_0B_P<br>Rx_0B_N                      | RX_0_1P<br>RX_0_1N      | A12<br>B12 | I, CML | Inverting and non-inverting CML-compatible, AC coupled differential inputs. An on-chip 100 Ohm differential termination resistor connects these inputs. |  |

| RX_0A_P<br>RX_0A_N                      | RX_0_2P<br>RX_0_2N      | A10<br>B10 | I, CML | Inverting and non-inverting CML-compatible, AC coupled differential inputs. An on-chip 100 Ohm differential termination resistor connects these inputs. |  |

| RX_2A_P<br>RX_2A_N                      | RX_0_3P<br>RX_0_3N      | C13<br>D13 | I, CML | Inverting and non-inverting CML-compatible, AC coupled differential inputs. An on-chip 100 Ohm differential termination resistor connects these inputs. |  |

| RX_1B_P<br>RX_1B_N                      | RX_0_4P<br>RX_0_4N      | C11<br>D11 | I, CML | Inverting and non-inverting CML-compatible, AC coupled differential inputs. An on-chip 100 Ohm differential termination resistor connects these inputs. |  |

| RX_3A_P<br>RX_3A_N                      | RX_0_5P<br>RX_0_5N      | E14<br>F14 | I, CML | Inverting and non-inverting CML-compatible, AC coupled differential inputs. An on-chip 100 Ohm differential termination resistor connects these inputs. |  |

| RX_2B_P<br>RX_2B_N                      | RX_0_6P<br>RX_0_6N      | E12<br>F12 | I, CML | Inverting and non-inverting CML-compatible, AC coupled differential inputs. An on-chip 100 Ohm differential termination resistor connects these inputs. |  |

| RX_4A_P<br>RX_4A_N                      | RX_0_7P<br>RX_0_7N      | G13<br>H13 | I, CML | Inverting and non-inverting CML-compatible, AC coupled differential inputs. An on-chip 100 Ohm differential termination resistor connects these inputs. |  |

| RX_3B_P<br>RX_3B_N                      | RX_1_0P<br>RX_1_0N      | G11<br>H11 | I, CML | Inverting and non-inverting CML-compatible, AC coupled differential inputs. An on-chip 100 Ohm differential termination resistor connects these inputs. |  |

| RX_4B_P<br>Rx_4B_N                      | RX_1_1P<br>RX_1_1N      | J14<br>K14 | I, CML | Inverting and non-inverting CML-compatible, AC coupled differential inputs. An on-chip 100 Ohm differential termination resistor connects these inputs. |  |

| RX_5A_P<br>RX_5A_N                      | RX_1_2P<br>RX_1_2N      | J12<br>K12 | I, CML | Inverting and non-inverting CML-compatible, AC coupled differential inputs. An on-chip 100 Ohm differential termination resistor connects these inputs. |  |

| RX_5B_P<br>RX_5B_N                      | RX_1_3P<br>RX_1_3N      | L13<br>M13 | I, CML | Inverting and non-inverting CML-compatible, AC coupled differential inputs. An on-chip 100 Ohm differential termination resistor connects these inputs. |  |

| RX_6A_P<br>RX_6A_N                      | RX_1_4P<br>RX_1_4N      | L11<br>M11 | I, CML | Inverting and non-inverting CML-compatible, AC coupled differential inputs. An on-chip 100 Ohm differential termination resistor connects these inputs. |  |

| RX_6B_P<br>RX_6B_N                      | RX_1_5P<br>RX_1_5N      | N14<br>P14 | I, CML | Inverting and non-inverting CML-compatible, AC coupled differential inputs. An on-chip 100 Ohm differential termination resistor connects these inputs. |  |

| RX_7A_P<br>RX_7A_N                      | RX_1_6P<br>RX_1_6N      | N12<br>P12 | I, CML | Inverting and non-inverting CML-compatible, AC coupled differential inputs. An on-chip 100 Ohm differential termination resistor connects these inputs. |  |

| RX_7B_P<br>RX_7B_N                      | RX_1_7P<br>RX_1_7N      | N10<br>P10 | I, CML | Inverting and non-inverting CML-compatible, AC coupled differential inputs. An on-chip 100 Ohm differential termination resistor connects these inputs. |  |

| TX_1A_P<br>TX_1A_N                      | TX_0_0P<br>TX_0_0N      | A1<br>B1   | O, CML | Inverting and non-inverting CML-compatible differential outputs. Driver presents an output impedance of 100 ohms between these outputs when switching.  |  |

| TX_0B_P<br>TX_0B_N                      | TX_0_1P<br>TX_0_1N      | A3<br>B3   | O, CML | Inverting and non-inverting CML-compatible differential outputs. Driver presents an output impedance of 100 ohms between these outputs when switching.  |  |

| TX_0A_P<br>TX_0A_N                      | TX_0_2P<br>TX_0_2N      | A5<br>B5   | O, CML | Inverting and non-inverting CML-compatible differential outputs. Driver presents an output impedance of 100 ohms between these outputs when switching.  |  |

4 Submit Documentation Feedback

Copyright © 2014–2017, Texas Instruments Incorporated

Product Folder Links: DS125DF1610

SNLS482B - APRIL 2014 - REVISED JANUARY 2017

## Pin Functions (continued)

| D0440DE4040                             |                         |          | -                  |                                                                                                                                                                                                                                                                                                                                                          |

|-----------------------------------------|-------------------------|----------|--------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DS110DF1610,<br>DS125DF1610<br>PIN NAME | DS150DF1610<br>PIN NAME | PIN      | I/O                | DESCRIPTION                                                                                                                                                                                                                                                                                                                                              |

| TX_2A_P<br>TX_2A_N                      | TX_0_3P<br>TX_0_3N      | C2<br>D2 | O, CML             | Inverting and non-inverting CML-compatible differential outputs. Driver presents an output impedance of 100 ohms between these outputs when switching.                                                                                                                                                                                                   |

| TX_1B_P<br>TX_1B_N                      | TX_0_4P<br>TX_0_4N      | C4<br>D4 | O, CML             | Inverting and non-inverting CML-compatible differential outputs. Driver presents an output impedance of 100 ohms between these outputs when switching.                                                                                                                                                                                                   |

| TX_3A_P<br>TX_3A_N                      | TX_0_5P<br>TX_0_5N      | E1<br>F1 | O, CML             | Inverting and non-inverting CML-compatible differential outputs. Driver presents an output impedance of 100 ohms between these outputs when switching.                                                                                                                                                                                                   |

| TX_2B_P<br>TX_2B_N                      | TX_0_6P<br>TX_0_6N      | E3<br>F3 | O, CML             | Inverting and non-inverting CML-compatible differential outputs. Driver presents an output impedance of 100 ohms between these outputs when switching.                                                                                                                                                                                                   |

| TX_4A_P<br>TX_4A_N                      | TX_0_7P<br>TX_0_7N      | G2<br>H2 | O, CML             | Inverting and non-inverting CML-compatible differential outputs. Driver presents an output impedance of 100 ohms between these outputs when switching.                                                                                                                                                                                                   |

| TX_3B_P<br>TX_3B_N                      | TX_1_0P<br>TX_1_0N      | G4<br>H4 | O, CML             | Inverting and non-inverting CML-compatible differential outputs. Driver presents an output impedance of 100 ohms between these outputs when switching.                                                                                                                                                                                                   |

| TX_4B_P<br>TX_4B_N                      | TX_1_1P<br>TX_1_1N      | J1<br>K1 | O, CML             | Inverting and non-inverting CML-compatible differential outputs. Driver presents an output impedance of 100 ohms between these outputs when switching.                                                                                                                                                                                                   |

| TX_5A_P<br>TX_5A_N                      | TX_1_2P<br>TX_1_2N      | J3<br>K3 | O, CML             | Inverting and non-inverting CML-compatible differential outputs. Driver presents an output impedance of 100 ohms between these outputs when switching.                                                                                                                                                                                                   |

| TX_5B_P<br>TX_5B_N                      | TX_1_3P<br>TX_1_3N      | L2<br>M2 | O, CML             | Inverting and non-inverting CML-compatible differential outputs. Driver presents an output impedance of 100 ohms between these outputs when switching.                                                                                                                                                                                                   |

| TX_6A_P<br>TX_6A_N                      | TX_1_4P<br>TX_1_4N      | L4<br>M4 | O, CML             | Inverting and non-inverting CML-compatible differential outputs. Driver presents an output impedance of 100 ohms between these outputs when switching.                                                                                                                                                                                                   |

| TX_6B_P<br>TX_6B_N                      | TX_1_5P<br>TX_1_5N      | N1<br>P1 | O, CML             | Inverting and non-inverting CML-compatible differential outputs. Driver presents an output impedance of 100 ohms between these outputs when switching.                                                                                                                                                                                                   |

| TX_7A_P<br>TX_7A_N                      | TX_1_6P<br>TX_1_6N      | N3<br>P3 | O, CML             | Inverting and non-inverting CML-compatible differential outputs. Driver presents an output impedance of 100 ohms between these outputs when switching.                                                                                                                                                                                                   |

| TX_7B_P<br>TX_7B_N                      | TX_1_7P<br>TX_1_7N      | N5<br>P5 | O, CML             | Inverting and non-inverting CML-compatible differential outputs. Driver presents an output impedance of 100 ohms between these outputs when switching.                                                                                                                                                                                                   |

| CLOCK PINS                              |                         |          |                    |                                                                                                                                                                                                                                                                                                                                                          |

| REF_CLK_P<br>REF_CLK_N                  |                         | P7<br>P8 | I, LVDS/<br>LVCMOS | Inverting and non-inverting<br>CML-compatible differential inputs for 25 MHz, 125 MHz, or<br>312.5 MHz clock. These differential signals are typically AC<br>coupled with 1 µF capacitors<br>When configured for single-ended input operation, apply<br>LVCMOS ref clock to REF_CLK_P and float REF_CLK_N.<br>Single-ended signals should be DC coupled. |

| CLK_MON_P<br>CLK_MON_N                  |                         | A7<br>A8 | O, LVDS            | Inverting and non-inverting<br>CML-compatible differential outputs to monitor system<br>differential clock.<br>When daisy chaining to another retimer the output frequency<br>should be set to 25 MHz.                                                                                                                                                   |

| SMBUS INTERFAC                          | E                       |          |                    |                                                                                                                                                                                                                                                                                                                                                          |

| SDA_IO                                  |                         | Μ7       | I/O,<br>Open Drain | Data Input / Open Drain Output<br>External pull-up resistor is required, typically in the $2k\Omega$ to $5k\Omega$ range. Pull-up value should be selected according to system<br>implementation.<br>Pin is 3.3 V LVCMOS tolerant.                                                                                                                       |

Copyright © 2014–2017, Texas Instruments Incorporated

5

Submit Documentation Feedback

## DS125DF1610 SNLS482B-APRIL 2014-REVISED JANUARY 2017

## **Pin Functions (continued)**

| DS110DF1610,<br>DS125DF1610<br>PIN NAME | DS150DF1610<br>PIN NAME | PIN                                                                                                  | I/O                | DESCRIPTION                                                                                                                                                                                                                                                          |

|-----------------------------------------|-------------------------|------------------------------------------------------------------------------------------------------|--------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SCL_IO                                  |                         | L6                                                                                                   | l/O,<br>Open Drain | Clock input/output<br>External pull-up resistor is required, typically in the $2k\Omega$ to $5k\Omega$<br>range. Pull-up value should be selected according to system<br>implementation.<br>Pin is 3.3 V LVCMOS tolerant<br>EEPROM configuration (SMBus Master mode) |

| JTAG INTERFACE <sup>(1)</sup>           |                         |                                                                                                      |                    |                                                                                                                                                                                                                                                                      |

| TMS_IO                                  |                         | B7                                                                                                   | I, LVCMOS          | JTAG Test Mode Select, internal pull-up                                                                                                                                                                                                                              |

| TDO_IO                                  |                         | C7                                                                                                   | O, LVCMOS          | JTAG Test Data Out                                                                                                                                                                                                                                                   |

| TRST_IO                                 |                         | C8                                                                                                   | I, LVCMOS          | JTAG Test Reset, internal pull-up                                                                                                                                                                                                                                    |

| TCK_IO                                  |                         | D6                                                                                                   | I, LVCMOS          | JTAG Test clock, internal pull-up                                                                                                                                                                                                                                    |

| TDI_IO                                  |                         | D7                                                                                                   | I, LVCMOS          | JTAG Test Data Input, internal pull-up                                                                                                                                                                                                                               |

| OTHER PINS                              |                         |                                                                                                      |                    |                                                                                                                                                                                                                                                                      |

| RESET_IO                                |                         | L8                                                                                                   | I, LVCMOS          | Resets registers and state machines on rising edge. Pulse LOW for minimum of $10\mu s$ to perform reset. Pin should be pulled HIGH during power on.                                                                                                                  |

| INTERR_IO                               |                         | M8                                                                                                   | O, Open<br>Drain   | Active Low interrupt signal. Pin goes low when an interrupt event occurs. Interrupts must be enabled via SMBus.                                                                                                                                                      |

| ADDR0                                   |                         | B6                                                                                                   | I, LVCMOS          | 4 level input strap pin for SMBus address code LSB. Standard LVCMOS output.                                                                                                                                                                                          |

| ADDR1                                   |                         | D5                                                                                                   | I, LVCMOS          | 4 level input strap pin for SMBus address code MSB.<br>Standard LVCMOS output.                                                                                                                                                                                       |

| READ_EN                                 |                         | G5                                                                                                   | I, LVCMOS          | Tie LOW for SMBus slave mode normal operation. Pin has<br>internal pull down.<br>In SMBus slave mode, tie HIGH to force SMBus address =<br>0x30.                                                                                                                     |

| ALL_DONE                                |                         | L5                                                                                                   | O, LVCMOS          | EEPROM load status. Pin goes LOW when EEPROM load is complete.                                                                                                                                                                                                       |

| EN_SMB                                  |                         | N8                                                                                                   | I, LVCMOS          | Connect to GND through ≤1kΩ resistor for SMBus slave<br>operation.<br>Connect to VDD through ≤1kΩ resistor for EEPROM<br>configuration                                                                                                                               |

| POWER                                   |                         |                                                                                                      |                    | ·                                                                                                                                                                                                                                                                    |

| VDD                                     |                         | E5, E7, E9,<br>E10, F5, F6,<br>F8, F10, G7,<br>G9, H6, H8,<br>J5, J7, J9,<br>J10, K5, K6,<br>K8, K10 | Power              | VDD = 2.5 V +/- 5%                                                                                                                                                                                                                                                   |

(1) Refer to the DS125DF1610 Programming Guide for additional information

Product Folder Links: DS125DF1610

Ţexas NSTRUMENTS

| DS110DF1610,<br>DS125DF1610<br>PIN NAME | DS150DF1610<br>PIN NAME | PIN                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | I/O   | DESCRIPTION                |

|-----------------------------------------|-------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|----------------------------|

| GND                                     |                         | A2, A4, A6,<br>A9, A11, A13,<br>B2, B4, B9,<br>B11, B13,<br>C1, C3, C5,<br>C10, C12,<br>C14, D1, D3,<br>D10, D12,<br>D14, E2, E4,<br>E6, E8, E11,<br>E13, F2, F4,<br>F7, F9, F11,<br>F13, G1, G3,<br>G6, G8, G10,<br>G12, G14,<br>H1, H3, H5,<br>H7, H9, H10,<br>H12, H14, J2,<br>J4, J6, J8,<br>J11, J13, K2,<br>K4, K7, K9,<br>K11, K13, L1,<br>L3, L10, L12,<br>L14, M1, M3,<br>M5, M10,<br>M12, M14,<br>N2, N4, N6,<br>N9, N11,<br>N13, P2, P4,<br>P6, P9, P11,<br>P13 | Power | Ground reference           |

| N/C                                     |                         | B8, C6, C9,<br>D8, D9, L7,<br>L9, M6, M9,<br>N7                                                                                                                                                                                                                                                                                                                                                                                                                            |       | No Connect, leave floating |

Submit Documentation Feedback

7

## 6 Specifications

## 6.1 Absolute Maximum Ratings<sup>(1)</sup>

Over operating free-air temperature range (unless otherwise noted)

|                                             | MIN  | MAX         | UNIT |

|---------------------------------------------|------|-------------|------|

| Supply Voltage (VDD)                        | -0.5 | 2.75        | V    |

| LVCMOS Input/Output Voltage                 | -0.5 | 2.75        | V    |

| Open Drain I/O Supply Voltage               | -0.5 | 4.0         | V    |

| CML Input Voltage                           | -0.5 | (VDD + 0.5) | V    |

| CML Input Current                           | -30  | 30          | mA   |

| Storage temperature range, T <sub>stg</sub> | -40  | 150         | °C   |

(1) If Military/Aerospace specified devices are required, please contact the Texas Instruments Sales Office/ Distributors for availability and specifications

## 6.2 Handling Ratings

|                    |                         |                                                                                                | VALUE  | UNIT |

|--------------------|-------------------------|------------------------------------------------------------------------------------------------|--------|------|

|                    |                         | Human body model (HBM), per ANSI/ESDA/JEDEC JS-001, all pins <sup>(1)</sup>                    | ±4,000 |      |

| V <sub>(ESD)</sub> | Electrostatic discharge | Charged device model (CDM), per JEDEC specification JESD22-C101, all $\ensuremath{pins^{(2)}}$ | ±1,000 | V    |

(1) JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

(2) JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

## 6.3 Recommended Operating Conditions

Over operating free-air temperature range (unless otherwise noted)

|                                                                     | MIN   | TYP | MAX   | UNIT |

|---------------------------------------------------------------------|-------|-----|-------|------|

| Supply Voltage                                                      | 2.375 | 2.5 | 2.625 | V    |

| Ambient Temperature                                                 | -40   | 25  | 85    | °C   |

| SMBus (SDA, SCL), INTERR_IO                                         |       | 2.5 | 3.6   | V    |

| Maximum Continuous Junction Temperature while Device is Operational |       |     | 115   | °C   |

## 6.4 Thermal Information

|                       | THERMAL METRIC <sup>(1)</sup> <sup>(2)</sup> | DS125DF1610<br>FCBGA ABB<br>(196) PINS | UNIT |

|-----------------------|----------------------------------------------|----------------------------------------|------|

| $R_{\thetaJA}$        | Junction-to-ambient thermal resistance       | 18.2                                   |      |

| R <sub>0JC(top)</sub> | Junction-to-case (top) thermal resistance    | 0.7                                    |      |

| $R_{\theta JB}$       | Junction-to-board thermal resistance         | 5.3                                    | °C/W |

| ΨJT                   | Junction-to-top characterization parameter   | 0.8                                    | C/VV |

| Ψјв                   | Junction-to-board characterization parameter | 5.3                                    |      |

| R <sub>0JC(bot)</sub> | Junction-to-case (bottom) thermal resistance | N/A                                    |      |

(1) For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report.

(2) Thermal model available upon request

## 6.5 Additional Thermal Information

| BOARD                           | θ <sub>JC</sub> (°C / W) | θ <sub>JA</sub> (°C / W) | ψ <sub>JT</sub> (°C / W) | ψ <sub>JB</sub> (°C / W) |

|---------------------------------|--------------------------|--------------------------|--------------------------|--------------------------|

| JEDEC 4 layer board, no airflow | 0.7                      | 18.2                     | 0.8                      | 5.3                      |

| 8x6 inches 10 layer, no airflow | 0.7                      | 7.2                      | 0.3                      | 3.2                      |

| 8x6 inches 20 layer, no airflow | 0.7                      | 6.4                      | 0.3                      | 3.2                      |

| 8x6 inches 30 layer, no airflow | 0.7                      | 6.3                      | 0.3                      | 3.2                      |

## 6.6 Electrical Characteristics

Over operating free-air temperature range (unless otherwise noted)

| SYMBOL              | PARAMETER                               | CONDITIONS                                                                | MIN   | TYP | MAX    | UNIT             |

|---------------------|-----------------------------------------|---------------------------------------------------------------------------|-------|-----|--------|------------------|

|                     |                                         | Full Rate                                                                 | 9.8   |     | 12.5   | Gbps             |

| Dhavd               |                                         | Half Rate                                                                 | 4.9   |     | 6.25   | Gbps             |

| R_baud              | Input Data Rate                         | Quarter Rate                                                              | 2.45  |     | 3.125  | Gbps             |

|                     |                                         | Eighth Rate                                                               | 1.225 |     | 1.5625 | Gbps             |

| POWER SUPPLY        |                                         |                                                                           |       |     |        |                  |

|                     |                                         | CTLE only, 800mVp-p<br>VOD, per channel,<br>CDR locked                    |       | 175 |        | mW               |

|                     |                                         | CDR Locking with CTLE<br>only, 800mVp-p VOD,<br>per channel               |       | 325 |        | mW               |

| W                   | Power Consumption per<br>Active Channel | CTLE and DFE, 800mVp-<br>p VOD, per channel,<br>CDR locked                |       | 200 | 323    | mW               |

|                     |                                         | CDR Locking with CTLE<br>and DFE, 800mVp-p VOD                            |       | 350 | 535.5  | mW               |

|                     |                                         | PRBS Checker                                                              |       | 100 |        | mW               |

|                     |                                         | PRBS Generator                                                            |       | 105 |        | mW               |

| W <sub>STATIC</sub> | Device Static Power<br>Consumption      | Power Applied to Device,<br>No Signals Present                            |       | 325 | 1325   | mW               |

|                     |                                         | 50 Hz to 100 Hz                                                           | 100   |     |        |                  |

| NT <sub>PS</sub>    | Power Supply Noise<br>Tolerance         | 100 Hz to 10 MHz                                                          |       | 40  |        | mV <sub>PP</sub> |

|                     | Tolerance                               | 10 MHz to 5.0 GHz                                                         |       | 10  |        |                  |

| LVCMOS              |                                         |                                                                           |       |     |        |                  |

| V IH                | High level input voltage                |                                                                           | 1.75  |     | VDD    | V                |

| VIL                 | Low level input voltage                 |                                                                           | GND   |     | 0.7    | V                |

| V <sub>OH</sub>     | High level output voltage               | IOH = 4mA                                                                 | 2     |     |        | V                |

| V <sub>OL</sub>     | Low level output voltage                | IOL = -4mA                                                                |       |     | 0.4    | V                |

|                     |                                         | Vinput = VDD,<br>Open Drain terminals                                     |       |     | 30     | μA               |

| l <sub>ін</sub>     | Input High Leakage<br>current           | Vinput = VDD,<br>JTAG terminals, Ref_CLK<br>terminals                     |       |     | 25     | μA               |

|                     |                                         | Vinput = VDD,<br>ADDR, READ_EN,<br>ALL_DONE terminals,<br>EN_SMB terminal |       |     | 75     | μΑ               |

|                     |                                         | Vinput = 0V,<br>Open drain terminals                                      | -15   |     |        | μA               |

| I <sub>IL</sub>     | Input Low Leakage<br>current            | Vinput = 0V,<br>JTAG terminals, Ref_CLK<br>terminals                      | -45   |     |        | μA               |

|                     |                                         | Vinput = 0V,<br>ADDR, READ_EN,<br>ALL_DONE terminals,<br>EN_SMB terminal  | -120  |     |        | μΑ               |

9

## **Electrical Characteristics (continued)**

Over operating free-air temperature range (unless otherwise noted)

| SYMBOL                          | PARAMETER                                                                               | CONDITIONS                                                                 | MIN                    | TYP | MAX                                           | UNIT             |

|---------------------------------|-----------------------------------------------------------------------------------------|----------------------------------------------------------------------------|------------------------|-----|-----------------------------------------------|------------------|

| RX INPUTS                       |                                                                                         |                                                                            | -                      |     |                                               |                  |

| R <sub>RD</sub>                 | DC Input Resistance                                                                     |                                                                            | 80                     | 100 | 120                                           | Ω                |

| V <sub>RX-IN</sub>              | Input Differential Voltage                                                              | Differential voltage seen at the high speed input terminals <sup>(1)</sup> |                        |     | 1600                                          | mV <sub>PP</sub> |

| V <sub>SDAT</sub>               | Signal Detect Assert                                                                    | Default setting<br>1T pattern, 12.5 Gbps                                   |                        | 110 |                                               | mV <sub>PP</sub> |

| V SDAT                          | Threshold                                                                               | Default setting<br>PRBS-31, 12.5 Gbps                                      |                        | 24  |                                               | Шурр             |

|                                 | Signal Detect De-Assert                                                                 | Default setting<br>1T pattern, 12.5 Gbps                                   |                        | 70  |                                               | mV <sub>PP</sub> |

| V <sub>SDDT</sub>               | Threshold                                                                               | Default setting<br>PRBS-31, 12.5 Gbps                                      |                        | 21  | mv                                            |                  |

| V <sub>cm-RX</sub>              | Input common mode                                                                       | Internal coupling cap                                                      | V <sub>RX-IN</sub> / 4 |     | VDD - (V <sub>RX-</sub><br><sub>IN</sub> / 4) | V                |

| TX OUTPUTS                      |                                                                                         |                                                                            |                        |     |                                               |                  |

| Vod                             | Output Differential Voltage                                                             | drv_sel_vod[5:0] = 31,<br>DEM, FIR = default                               | 725                    | 935 | 1135                                          | mV <sub>PP</sub> |

| VOD                             | Output Differential Voltage                                                             | drv_sel_vod[5:0] = 15,<br>DEM, FIR = default                               | 350                    | 470 | 595                                           | шурр             |

| $\Delta V_{OD}$                 | Step Size for drv_sel_vod<br>Control                                                    | Default DEM, and FIR settings                                              |                        | 50  |                                               | mV <sub>PP</sub> |

| $\Delta V_{ODVT}$               | Change in Output<br>Differential Voltage due to<br>Change in Temperature<br>and Voltage |                                                                            |                        | <15 |                                               | mV <sub>PP</sub> |

| T <sub>Rd</sub>                 | Output Differential<br>Resistance                                                       |                                                                            |                        | 100 |                                               | Ω                |

| t <sub>r</sub> , t <sub>f</sub> | Output Rise/Fall Time                                                                   | 20% - 80% using 8T<br>Pattern, fir_sel_edge =<br>default                   |                        | 35  |                                               | ps               |

| I <sub>OS</sub>                 | Output Short Circuit<br>Current                                                         | Differential Driver Output<br>Pin Short to GND                             |                        | -16 |                                               | mA               |

(1) Parameter is not tested at final production

## **Electrical Characteristics (continued)**

| SYMBOL             | PARAMETER                                                | CONDITIONS                                                                                   | MIN                        | TYP   | MAX  | UNIT               |  |

|--------------------|----------------------------------------------------------|----------------------------------------------------------------------------------------------|----------------------------|-------|------|--------------------|--|

| RETIMER JITTER     | SPECS                                                    |                                                                                              |                            |       |      |                    |  |

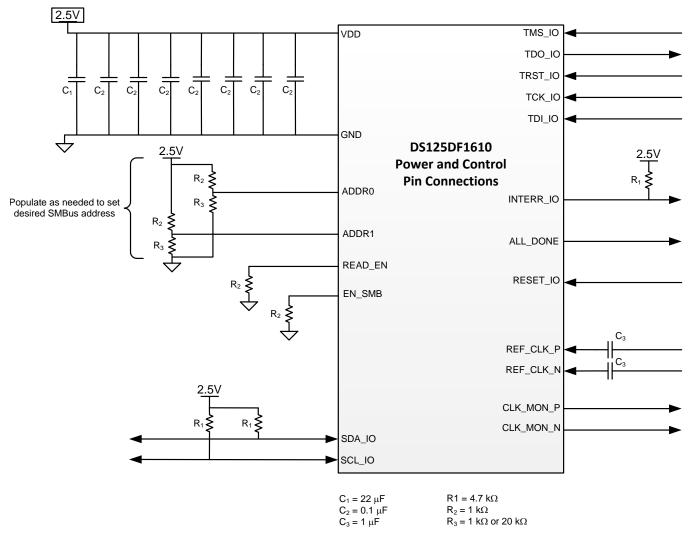

| J <sub>TJ</sub>    | Total Output Jitter                                      | PRBS-15 pattern,<br>measured to 1e-12<br>10.3125 Gbps                                        |                            | 0.08  |      | UI                 |  |

| J <sub>RJ</sub>    | Output Random Jitter                                     | PRBS-15 pattern,<br>measured to 1e-12<br>10.3125 Gbps                                        |                            | 3.6   |      | mUI <sub>RMS</sub> |  |

| J <sub>DJ</sub>    | Output Deterministic Jitter                              | PRBS-15<br>10.3125 Gbps                                                                      |                            | 0.03  |      | UI                 |  |

| 1                  | litter Decking                                           | Data Rate = 9.8 Gbps,<br>Peaking Frequency =<br>1 - 3 MHz                                    |                            | <1    |      | ٦Ŀ                 |  |

| JPEAK              | Jitter Peaking                                           | Data Rate = 12.5 Gbps<br>Peaking Frequency =<br>3 - 8 MHz                                    |                            | <1    |      | - dB               |  |

|                    |                                                          | Data Rate = 9.8 Gbps                                                                         |                            | 5     |      | N 41 1-            |  |

| BW <sub>PLL</sub>  | PLL Bandwidth at -3 dB                                   | Data Rate = 12.5 Gbps                                                                        |                            | 10    |      | MHz                |  |

| J <sub>TOL</sub>   | Input Jitter Tolerance                                   | Jitter per SFF-8431<br>Appendix D.11<br>Combination of $D_J P_J$ and $R_J$                   |                            | >0.7  |      | UI                 |  |

| RETIMER TIMING     | SPECS                                                    |                                                                                              |                            |       |      |                    |  |

| +                  | Propagation Delay from                                   | No Cross Point                                                                               | 3UI + 220ps<br>3UI + 230ps |       |      | ps                 |  |

| t <sub>D</sub>     | Rx inputs to Tx outputs                                  | Cross Point enabled                                                                          |                            |       |      |                    |  |

| t <sub>SK</sub>    | Channel To Channel<br>Skew                               |                                                                                              | <80                        |       |      | ps                 |  |

| RECOMMENDED        | REFERENCE CLOCK SPECS                                    |                                                                                              |                            |       |      |                    |  |

|                    |                                                          |                                                                                              |                            | 25    |      |                    |  |

| REF <sub>f</sub>   | Input Reference Clock<br>Frequency                       |                                                                                              |                            | 125   |      | MHz                |  |

|                    | - 1                                                      |                                                                                              |                            | 312.5 |      |                    |  |

| REF <sub>PPM</sub> | Reference Clock PPM<br>Tolerance                         | $REF_{f} = 25 \text{ MHz}^{(2)}$                                                             | -100                       |       | 100  | PPM                |  |

| REF <sub>IDC</sub> | Input Reference Clock<br>Duty Cycle                      | $REF_f = 25 MHz^{(2)}$                                                                       | 40%                        | 50%   | 60%  |                    |  |

| REF <sub>ODC</sub> | Intrinsic Reference Clock<br>Duty Cycle Distortion       | Intrinsic Duty Cycle<br>Distortion of the reference<br>clock output from the<br>CLK_MON pins |                            | ±1%   |      |                    |  |

| REF <sub>VID</sub> | Reference Clock Input<br>Differential Voltage            | Differential mode <sup>(2)</sup>                                                             | 200                        |       | 1200 | mV <sub>PP</sub>   |  |

| REF <sub>VIH</sub> | Reference Clock Signle-<br>Ended Input High<br>Threshold | Single-ended mode.<br>Signal DC coupled to<br>REF_CLK_P,<br>REF_CLK_N is float               |                            | 1.75  |      | V                  |  |

| REF <sub>VIL</sub> | Reference Clock Single-<br>Ended Input Low<br>Threshold  | Single-ended mode.<br>Signal DC coupled to<br>REF_CLK_P,<br>REF_CLK_N is float               |                            | 0.7   |      | V                  |  |

Over operating free-air temperature range (unless otherwise noted)

(2) Parameter is specified by design and not tested at final production

## **Electrical Characteristics (continued)**

| SYMBOL              | PARAMETER                           | CONDITIONS                                                                  | MIN  | ТҮР  | MAX | UNIT |

|---------------------|-------------------------------------|-----------------------------------------------------------------------------|------|------|-----|------|

| SMBus ELECTRI       | CAL CHARACTERISTICS (SLAVE M        | IODE)                                                                       |      |      |     |      |

| V <sub>IH</sub>     | Input High Level Voltage            | SDA and SCL                                                                 | 1.75 |      | 3.6 | V    |

| V <sub>IL</sub>     | Input Low Level Voltage             | SDA and SCL                                                                 | GND  |      | 0.8 | V    |

| C <sub>IN</sub>     | Input Pin Capacitance               |                                                                             |      | <5   |     | pF   |

| V <sub>OL</sub>     | Low Level Output Voltage            | SDA or SCL<br>IOL = 1.25 mA                                                 |      |      | 0.4 | V    |

| I <sub>IN</sub>     | Input Current                       | SDA or SCL, V <sub>INPUT</sub> =<br>V <sub>IN</sub> , V <sub>DD</sub> , GND | -15  |      | 15  | μA   |

| T <sub>R</sub>      | SDA Rise Time Read<br>Operation     | SDA, pullup resistor = 1 $k\Omega$ , Cb = 50pF                              |      | 150  |     | ns   |

| T <sub>F</sub>      | SDA Fall Time Read<br>Operation     | SDA, pullup resistor = 1 $k\Omega$ , Cb = 50pF                              |      | 4.5  |     | ns   |

| RECOMMENDED         | SMBus SWITCHING CHARACTERI          | STICS (SLAVE MODE)                                                          |      |      |     |      |

| f <sub>SCL</sub>    | SCL Clock Frequency                 |                                                                             | 10   | 100  | 400 | kHz  |

| t <sub>HD:DAT</sub> | Data Hold Time                      |                                                                             |      | 0.75 |     | ns   |

| t <sub>SU:DAT</sub> | Data Setup Time                     |                                                                             |      | 100  |     | ns   |

| RECOMMENDED         | SMBus SWITCHING CHARACTERI          | STICS (MASTER MODE)                                                         |      |      |     |      |

| F <sub>SCL</sub>    | SCL Clock Frequency                 |                                                                             |      | 400  |     | kHz  |

| T <sub>LOW</sub>    | SCL Low Period                      |                                                                             |      | 1.25 |     | μs   |

| T <sub>HIGH</sub>   | SCL High Period                     |                                                                             |      | 1.25 |     | μs   |

| T <sub>HD:STA</sub> | Hold Time Start Operation           |                                                                             |      | 0.6  |     | μs   |

| T <sub>SU:STA</sub> | Setup Time Start<br>Operation       |                                                                             |      | 0.6  |     | μs   |

| T <sub>HD:DAT</sub> | Data Hold Time                      |                                                                             |      | 0.9  |     | μs   |

| T <sub>SD:DAT</sub> | Data Setup Time                     |                                                                             |      | 0.1  |     | μs   |

| T <sub>SU:STO</sub> | Stop Condition Setup<br>Time        |                                                                             |      | 0.6  |     | μs   |

| T <sub>BUF</sub>    | Bus Free Time between<br>Stop-Start |                                                                             |      | 1.3  |     | μs   |

| T <sub>R</sub>      | SCL and SDA Rise Time               |                                                                             |      | 300  |     | ns   |

| T <sub>F</sub>      | SCL and SDA Fall Time               |                                                                             |      | 300  |     | ns   |

| RECOMMENDED         | JTAG SWITCHING CHARACTERIS          | TICS                                                                        | ·    |      |     |      |

| t <sub>TCK</sub>    | TCK Clock Period                    |                                                                             |      | 100  |     | ns   |

| t <sub>SU</sub>     | TDI, TMI Setup Time to TCK          |                                                                             |      | 50   |     | ns   |

| t <sub>HD</sub>     | TDI, TMS Hold Time to TCK           |                                                                             |      | 50   |     | ns   |

| t <sub>DLY</sub>    | TCK Falling Edge to TDO             |                                                                             |      | 50   |     | ns   |

Over operating free-air temperature range (unless otherwise noted)

## 7 Detailed Description

## 7.1 Overview

The DS125DF1610 is a multi-rate, 16-channel retimer with integrated 4x4 cross point switches and receiver AC coupling capacitors. There is 1 cross point switch per 4 channels (quad). Each channel in the DS125DF1610 operates independently even if the cross point switch routing is enabled. All channels include a Continuous Time Linear Equalizer (CTLE), Decision Feedback Equalizer (DFE), Variable Gain Amplifier (VGA), Clock and Data Recovery circuit (CDR) and a differential driver with a 3-tap transmit Finite Impulse Response (FIR) filter. Each channel also has its own Eye Opening Monitor (EOM) and configurable Pseudo-Random Bit Sequence (PRBS) pattern checker and pattern generator that can be used for debug purposes.

The DS125DF1610 also supports JTAG boundary scan. The DS125DF1610 is configurable through a single SMBus port. The DS125DF1610 can also act as an SMBus master to configure itself from an EEPROM.

The sections below describe the functionality of the various circuits and features within the DS125DF1610. For more information about how to program or operate these features please consult the DS125DF1610 Programming Guide.

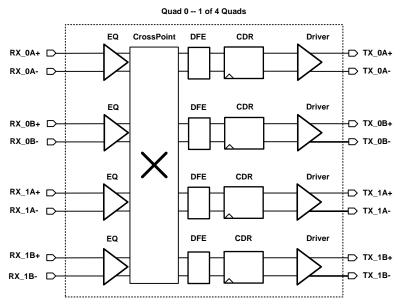

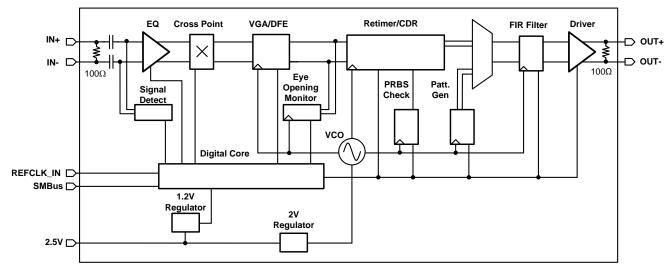

## 7.2 Functional Block Diagram

Figure 1. DS125DF1610 Simplified Cross Point Diagram

## Functional Block Diagram (continued)

Figure 2. DS125DF1610 Simplified Data Path Diagram

## 7.3 Feature Description

## 7.3.1 Device Data Path Operation

The DS125DF1610 data path consists of several key blocks as shown in Figure 2. These key circuits are:

- AC-coupled Receiver with Signal Detect

- CTLE

- Cross Point Switch

- DFE with VGA

- CDR

- Differential Driver with FIR Filter

## 7.3.2 AC-Coupled Receiver with Signal Detect

The differential receiver for each DS125DF1610 channel contains on chip AC coupling capacitors. The minimum bandwidth for this AC coupled receiver is 16kHz. The receiver also contains a signal detect circuit.

The signal detect circuit monitors the energy level on the receiver inputs and powers on or off the rest of the high speed data path if a signal is detected or not. By default, each channel allows the signal detect circuit to automatically power on or off the rest of the high speed data path depending on if a signal is present. The signal detect block can be manually controlled in the SMBus channel registers. This can be useful if it is desired manually force channels to be disabled. For information on how to manually operate the signal detect circuit please see the DS125DF1610 Programming Guide and channel register 0x14 information.

## 7.3.3 CTLE

The CTLE in the DS125DF1610 is a fully adaptive equalizer with adjustable bandwidth and optional limiting stage. The CTLE adapts according to a Figure of Merit (FOM) calculation during the lock acquisition process. Once the CDR has locked and the CTLE has been adapted, the CTLE boost level will be frozen until a manual re-adapt command is issued or until the CDR re-enters the lock acquisition state. The CTLE is typically re-adapted by resetting the CDR, set and then clear channel register 0x0A[3:2].

## Feature Description (continued)

The CTLE consists of 4 stages, with each stage having 2-bit boost control. This allows for 256 different stageboost combinations. The CTLE adaption algorithm allows the CTLE to adapt through 32 of these stage-boost combinations. These 32 stage-boost combinations comprise the EQ Table in the channel registers; see channel registers 0x40 through 0x5F. This EQ Table can be reprogrammed to support up to 32 of the 256 stage-boost settings. Users also have the option of limiting the EQ table length to any value between a minimum value of 1 and a maximum value of 32.

CTLE boost levels are determined by summing the boosts levels of the 4 stages. Different stage-boost combinations that sum to the same number will have approximately the same boost level, but will result in a different shape for the EQ transfer function (boost curve). The boost levels can be set between 0 dB and 31 dB.

The CTLE bandwidth can be adjusted through SMBus control to 3 different levels:

| CTLE BANDWIDTH SETTING | BANDWDITH (GHz) (TYP) |

|------------------------|-----------------------|

| Full Rate (default)    | 9                     |

| Mid Rate               | 7                     |

| Half Rate              | 5                     |

## Table 1. CTLE Bandwidth Settings

The fourth stage in the CTLE can be programmed through the SMBus interface to become a limiting stage rather than a linear stage. This is useful in some applications, but it should not be typically used in combination with the DFE.

## 7.3.4 Cross Point Switch

Each quad has a 4x4 non-blocking analog cross point switch. This allows for full switching or broadcasting of data between any input within the quad to any output within the quad. Since the cross point switch is an analog implementation, all of the channels are allowed to operate asynchronously. The analog implementation also minimizes added latency through the device.

As shown in Figure 3, the cross point switch connections for each quad are located between CTLE and DFE in each channel.

The cross point switch consists of 4 sets of MUXs and buffers. In each channel there is a local buffer and a multidrive buffer. The local buffer transmits data from the CTLE to the DFE of the same channel. The multi drive buffer transmits data from the CTLE to the DFE(s) of other channels within the quad. Each channel has two MUXs:

- 1. Data path mux Selects whether to get data from the local buffer or from the other channel's multi-driver buffer

- 2. Control bus mux Selects where the signal detect and EQ control bus should be connected. This setting should mirror the data path mux setting. Note, when an EQ is connected to another channel's CDR the EQ becomes associated with that CDR's register set. For example, if the cross point was configured to do point to point switching from the inputs of channel 0 to the output of channel 1 and the inputs of channel 1 to the outputs of channel 0, the EQ physically located at the pins for inputs of channel 0 would be accessible through the register set of channel 1.

A simplified diagram of the cross point switch is shown in Figure 3.

| 0 | TX/RX_0A | TX/RX_0B | TX/RX_1A | TX/RX_1B |

|---|----------|----------|----------|----------|

| 1 | TX/RX_2A | TX/RX_2B | TX/RX_3A | TX/RX_3B |

| 2 | TX/RX_4A | TX/RX_4B | TX/RX_5A | TX/RX_5B |

| 3 | TX/RX_6A | TX/RX_6B | TX/RX_7A | TX/RX_7B |

|   | ·        |          |          |          |

QUAD

# Figure 3. Cross Point Switch Diagram

| Local<br>Buffer<br>Multi-Point<br>Buffer | Data and Control<br>Bus Muxs<br>VGA, DFE, CDR,<br>CH A TX |

|------------------------------------------|-----------------------------------------------------------|

| Local<br>Buffer<br>Multi-Point<br>Buffer | Data and Control<br>Bus Muxs<br>VGA, DFE, CDR,<br>CH B TX |

| Local<br>Buffer<br>Multi-Point<br>Buffer | Data and Control<br>Bus Muxs<br>VGA, DFE, CDR,<br>CH C TX |

| Local<br>Buffer<br>Multi-Point<br>Buffer | Data and Control<br>Bus Muxs<br>VGA, DFE, CDR,<br>CH D TX |

## DS125DF1610

Ch D

Copyright © 2014–2017, Texas Instruments Incorporated

In a typical point-to-point switching application users must configure the following for each channel:

- 1. Control bus mux setting (ch reg 0x9B)

- 2. Data path mux setting (ch reg 0x96)

- 3. Enabling/Disabling the local or multi-drive buffers for each channel (ch reg 0x96)

- 4. Cross point enable bit (ch reg 0x96)

- 5. Perform a CDR reset and reset release (ch reg 0x0A)

Note, when using the cross point switch the local and multi-drive buffer should both be enabled regardless of the desired configuration.

The cross point switch can also be used to replicate data or perform a broadcast function. The options for this type of configuration include:

- 1:2 any channel input to any 2 channels output

- 1:3 any channel input to any 3 channels output

- 1:4 any channel input to all 4 channels output

When the cross point switch is configured to replicate/broadcast data a master must be assigned during the cross point configuration. The master channel will have control over the CTLE adaption. All of the slave channels will be able to adapt their own DFE, but will not have control to adapt the CTLE. In this type of configuration there must be 1 channel assigned as a master. All other channels in the broadcast network must be assigned as slaves. There cannot be more than one master channel in a broadcast network. In a broadcast configuration, the straight through path connecting the broadcasting input to its own output needs to be enabled and set to have master control.

In a typical data replication/broadcast application users must configure the following for each channel:

- 1. Control bus mux setting (ch reg 0x9B)

- 2. Data path mux setting (ch reg 0x96)

- 3. Enabling/Disabling the local or multi-drive buffers for each channel (ch reg 0x96)

- 4. Master/Slave assignment (ch reg 0x96) -- master/slave bit set to master, master function assigned by mux setting

- 5. Cross point enable bit (ch reg 0x96)

- 6. Perform a CDR reset and reset release (ch reg 0x0A)

## 7.3.5 DFE with VGA

A 5-tap DFE with a VGA can be enabled within the data path of each channel to assist with reducing the effects of cross talk, reflections, or post cursor inter-symbol interference (ISI). The DFE must be manually enabled, regardless of the selected adapt mode. Once the DFE has been enabled it can be configured to adapt only during lock acquisition or to adapt continuously. The DFE can also be manually configured to specified tap polarities and tap weights. However, when the DFE is configured manually the DFE auto-adaption should be disabled.

The DFE taps are all feedback taps with 1UI spacing. Each tap has a specified boost weight range and polarity bit.

| DFE Parameter        | VALUE (mV) (TYP)                                                                                                                              |

|----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|

| Tap 1 Weight Range   | 0 - 224                                                                                                                                       |

| Tap 2-5 Weight Range | 0 - 112                                                                                                                                       |

| Tap Weight Step Size | 7                                                                                                                                             |

| Polarity             | + (positive): Signal is attenuated by the tap weight, register bit = 0<br>- (negative): Signal is boosted by the tap weight, register bit = 1 |

## Table 3. DFE Tap Weights

The VGA is located within the DFE block. The VGA has 2-bit control and allows for 3 levels of boost. The VGA can be used to assist in the recovery of extremely small signals. Note that the default VGA should be used for most applications.

| VGA BOOST Setting (CH REG 0x8E[1:0]) | BOOST (dB) (TYP) |

|--------------------------------------|------------------|

| 00 (default)                         | 0                |

| 01                                   | 6                |

| 10                                   | 6                |

| 11                                   | 12               |

## Table 4. VGA Boost Settings

## 7.3.6 Clock and Data Recovery

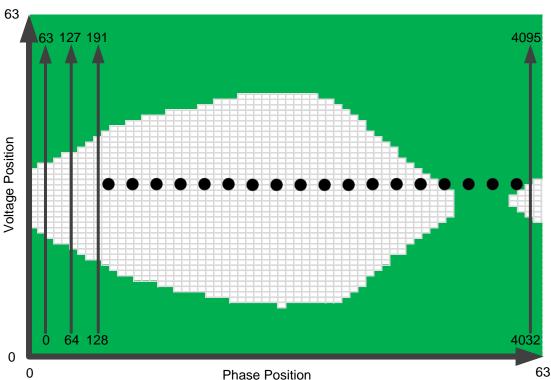

The CDR block consists of a Phase Locked Loop (PLL), reference clock based PPM counter, Input and Output Data Multiplexers (mux) and circuits to monitor single bit transitions and detect false locking. The CDR sampling position is fixed at the 0.5UI location for each bit.

By default, the equalized data is fed into the CDR for clock and data recovery. The recovered data is then output to the FIR filter and differential driver. Users can configure the CDR data to route the recovered clock and data to the PRBS checker. Users also have the option of configuring the output of the CDR to send raw non-retimed data, or data from the pattern generator.

The CDR requires the following in order to be properly configured:

- Input reference clock with proper reference clock divider setting to run the PPM counter.

- Expected data rates must be programmed into the CDR either through the rate/sub-rate Table 18 or entered manually with the corrected divider settings.

## 7.3.7 Reference Clock

The reference clock is not part of the CDR's PLL. The reference clock is connected only to the PPM counter for each CDR. The PPM counter constrains the allowable lock ranges of the CDR according to the programmed values in the rate/sub-rate Table 18 or the manually entered data rates.

The reference clock can be set to any of the 3 allowable frequencies independent of the data rate of the high speed channel. The input reference clock can be single-ended or differential for the 25 MHz or 125 MHz settings. If the 312.5 MHz setting is used, the input signaling type should be differential. The reference clock can be output through the CLK\_MON pins for observation or daisy chaining the reference clock to the next device. If the CLK\_MON port is used for daisy chaining then the output frequency should be set to 25 MHz.

If the reference clock port is configured to operate in single-ended mode, the 2.5V LVCMOS clock signal should be applied to the REF\_CLK\_P pin. In this configuration the REF\_CLK\_N pin should be floated (N/C). In this case the LVCMOS clock signal should be DC coupled into the REF\_CLK\_P pin. If the reference clock port is configured for differential mode, it is recommended to AC couple the clock signal into the DS125DF1610 device.

Configuring the reference clock frequency is done in share register 0x02[6:5]. Configuring the reference clock input port for single-ended or differential mode operation is done in share register 0x0B[4]. Enabling or disabling the CLK\_MON port is done in share reg 0x0A[0]. Selecting the CLK\_MON outputs to transmit the divided (25 MHz) or undivided (input frequency) clock frequency is done in share register 0x04[7].

| INPUT FREQUENCE | INPUT CONFIGURATION          | DEFAULT CLK_MON<br>FREQUENCY | RECOMMENDED CLK_MON<br>OUTPUT FREQUENCY FOR<br>DAISY CHAINING |  |  |  |

|-----------------|------------------------------|------------------------------|---------------------------------------------------------------|--|--|--|

| 25 MHz          | Single-ended or Differential | 25 MHz                       | 25 MHz                                                        |  |  |  |

| 125 MHz         | Single-ended or Differential | 125 MHz                      | 25 MHz                                                        |  |  |  |

| 312.5 MHz       | Differential                 | 312.5 MHz                    | 25 MHz                                                        |  |  |  |

## Table 5. REF\_CLK and CLK\_MON Configurations

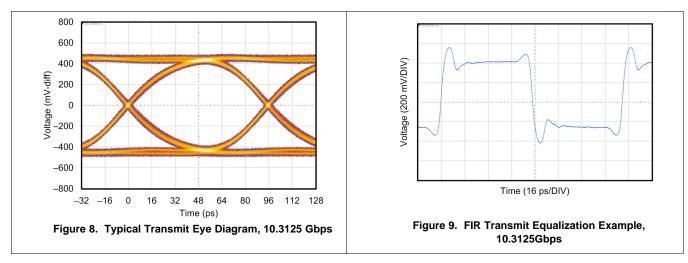

## 7.3.8 Differential Driver with FIR Filter

The DS125DF1610 uses a 3-tap FIR filter to assist with transmit equalization. The FIR filter consists of a pre cursor tap, a main cursor tap and a post cursor tap. Each tap has a polarity bit and 64 available levels. By default, the main cursor tap is set to a positive polarity, while the pre cursor and post cursor taps are set to a negative polarity. Users can invert the polarity of all 3 FIR taps to invert the polarity of the output data.

The DS125DF1610 output driver can be manually powered off through SMBus register control.

## 7.3.9 Setting the Output V<sub>OD</sub>

The output differential voltage ( $V_{OD}$ ) of the driver is controlled by manipulating the drv\_sel\_vod bits, DEM bits, and FIR main cursor tap. The Table 6 below shows various settings for  $V_{OD}$  settings ranging from 150m $V_{PP}$  to 1200 m $V_{PP}$ . Using the FIR, DEM and drv\_sel\_vod bits is the recommended method for configuring the output  $V_{OD}$  for the best signal integrity.

| V <sub>OD</sub> (mV <sub>PP</sub> ) | DEM SETTING | drv_sel_vod |     | FIR  |      |  |  |

|-------------------------------------|-------------|-------------|-----|------|------|--|--|

|                                     |             | SETTING     | PRE | MAIN | POST |  |  |